实验三:计数器实验——计数器的使用

一、 实验目的与意义

- 了解FPGA实现计数器的原理。

- 掌握Verilog实现计数器的编程方法。

- 掌握QuartusII集成开发环境的使用。

二、 实验设备及平台

- iCore4 双核心工控板。

- Blaster(或相同功能)仿真器。

- Micro USB线缆。

- QuartusII开发平台。

- 装有WIN XP(及更高版本)系统的计算机。

三、 实验原理

- 1、计数器原理:计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

- 2、计数器的Verilog实现:

表3-1

| 端口名称 | I/O | 功能描述 |

| clk_25m | Input | 模块的工作时钟,频率为25M |

| rst_n | Input | 模块复位,低电平复位 |

| fpga_ledg | output | 低电平时LED灯亮 |

- 3、本实验计数器的实现形式:本实验中,计数器在每个时钟上升沿加一,达到设定的计数值时自动清零,重新开始计数。计数器计满时改变LED的状态,故LED表现形式为不停闪烁。通过改变计数器的计数值大小可以改变LED的闪烁频率。

四、 代码讲解

本实验例程同样分为三个模块,这里不再一一讲解,只讲解最关键的计数器控制led灯模块。

//----------------定义模块的输入输出端口,如表3-1所示----------------// module counter_ctrl ( input clk_25m, input rst_n, output fpga_ledg ); //----------------计数器控制绿色led闪烁---------------------------// reg ledg; reg [24:0]cnt; //定义25位的寄存器型变量,作为计数器 //----------每次clk_25m上升沿来时执行always块中内容--------------// always@(posedge clk_25m or negedge rst_n) if(!rst_n) begin ledg <= 1'd1; cnt <= 25'd0; end //-----------实现了cnt从0加至5000000为一个计数周期----------------// //----------即每隔[5000000*(1/25m)]s执行一次led取反操作-----------// else if(cnt == 25'd5000000) begin ledg <= ~ledg;//ledg取反操作,即实现了绿色led灯闪烁的功能 cnt <= 25'd0;//cnt计数达到5000000时自动清零,开始下一轮计数 end else cnt <= cnt + 1'd1;//cnt值没有达到5000000时自动加1 …… endmodule

五、 实验验证

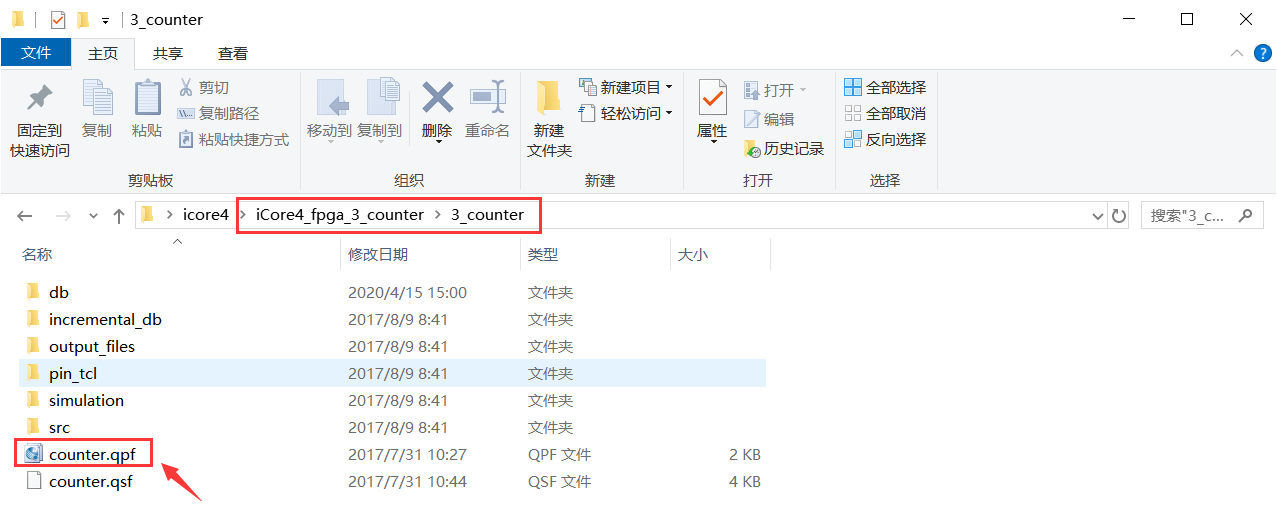

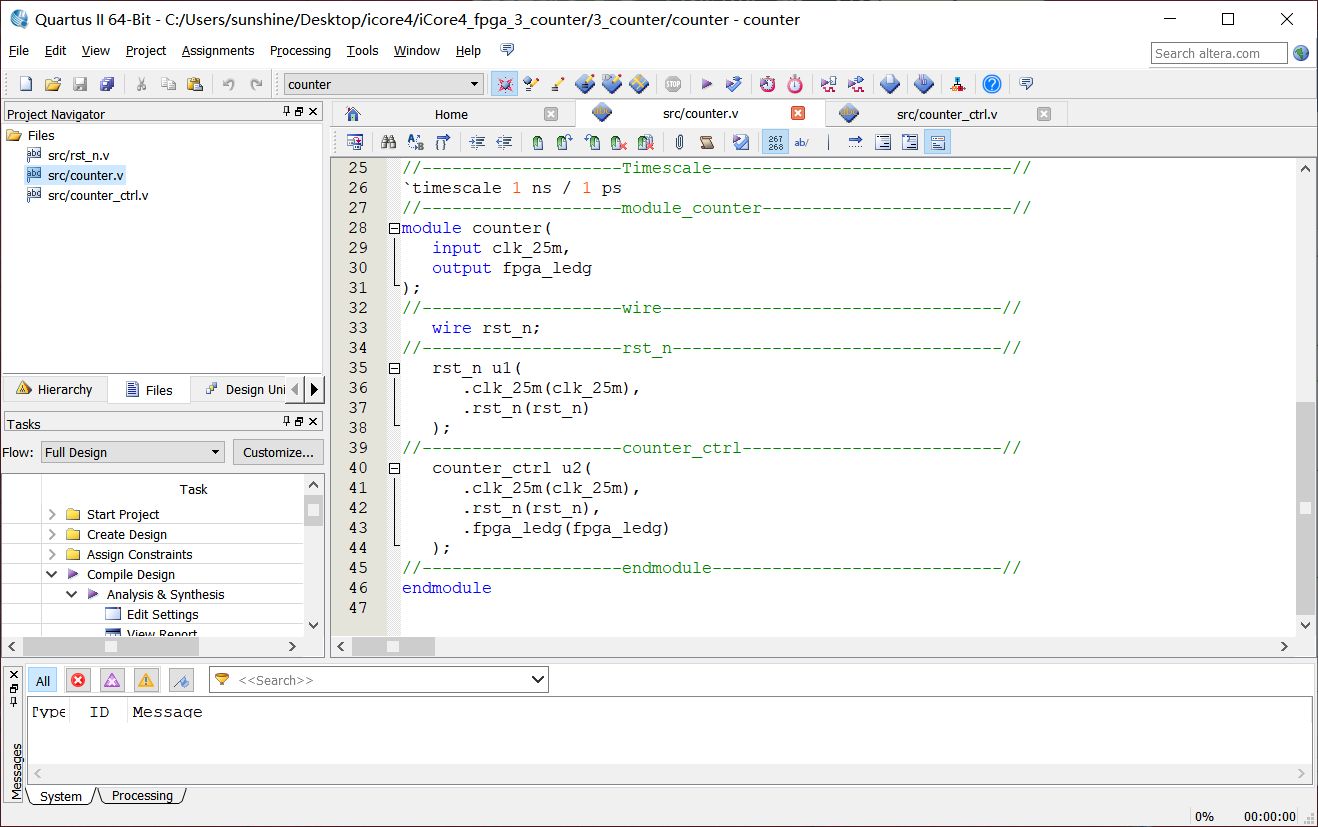

1、双击打开例程里的QuartusII工程文件。如图3-1、3-2所示。

1、双击打开例程里的QuartusII工程文件。如图3-1、3-2所示。

2、对工程文件进行相关配置、编译及引脚锁定等操作后将配置文件下载至iCore4双核心工控板,观察实验现象。

3、实验现象应为:iCore4双核心工控板上与FPGA相连的绿色led灯不断闪烁。

六、 拓展实验

- 请试着改变计数器变量cnt计数的最大值(注意:cnt定义时的位数决定了cnt数值可变化的范围),以此来改变led灯的闪烁频率。