| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-11-23 | zgf | 初次建立 |

实验十:PWM输出实验——不同方波信号的输出

一、 实验目的与意义

- 了解PWM信号含义。

- 掌握宏定义、参数变量的使用方法。

- 掌握HqFpga的使用方法。

二、 实验设备及平台

- iCore3L 双核心板。

- XiST USB Cable(或相同功能)仿真器。

- Micro USB线缆。

- 装有HqFpga软件开发平台的电脑一台。

三、 实验原理

- PWM全称是Pulse Width Modulation,是脉冲宽度调制缩写。它是通过对脉冲宽度进行调制,等效输出所需要的波形。在PWM波形属性中频率和占空比是两个非常重要的参数。而本实验的主要目的就是通过Verilog语言,在FPGA实现不同频率和占空比的PWM信号。

- PWM信号的频率是和周期对应的,占空比是指在一个周期内,高电平的持续时间占整个信号周期的百分比。通过调节信号周期,可以实现信号频率的控制;通过调节周期内高电平的持续时间,可以实现占空比的控制。

- 本实验就是通过控制PWM信号的周期和占空比,实现不同频率和占空比的方波信号输出。具体实现方法是:以系统时钟周期为单位,对其进行计数,控制输出信号高电平持续的系统时钟周期个数和低电平持续的系统时钟周期个数,从而实现占空比和周期的控制。

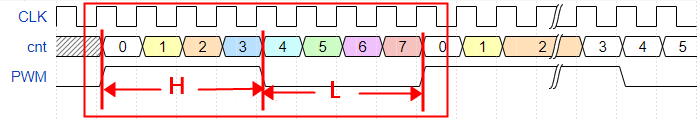

- 以下图为例,红框中为PWM信号的一个周期。其中H表示的高电平持续4个CLK时钟周期,L表示的低电平也持续4个CLK时钟周期。因此这是一个占空比50%,周期是CLK周期的8倍。

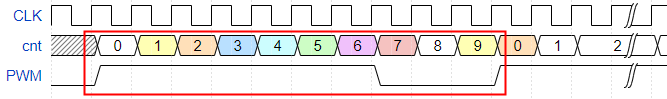

- 而下图则是一个占空比70%,周期是CLK时钟周期10倍的PWM信号。

- 通过上面两个图示的理解,那么实现PWM信号的输出,可以采用对系统时钟周期进行计数的方式实现。iCore3L的系统时钟是25MHz,以系统时钟周期上升沿作为触发条件,进行累加计数。如果要得到一个频率为500KHz的信号,那么其周期是系统时钟周期的

- 25000000Hz/500 000Hz =50(倍)

- 即计数器从0计到49所用的时间,是500KHz信号的一个周期。如果使500KHz信号在计数器从0计数到29的时候是高电平,30计数到49的时候是低电平,那么,就可以得到1个占空比为60%的500KHz PWM信号。

四、 代码讲解

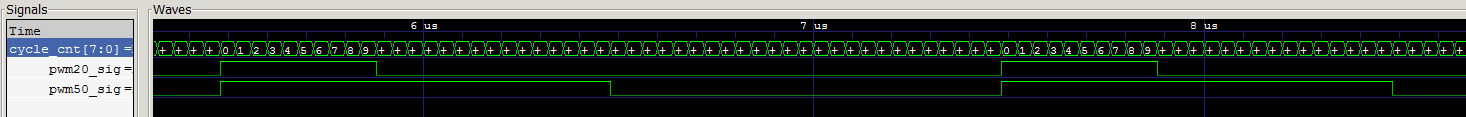

- 本实验中参考时钟为clk_fpga(25MHz),频率控制参数为cycle,占空比参数为puty_50和puty_20。频率为500KHz的波形计算公式为:

- 25MHz/(cycle-1)=500K Hz;

- 占空比为20%的周期参数计算公式为:

- puty_20/cycle;

- 占空比为50%的周期参数计算公式为:

- puty_50/cycle。

- 则输出信号的Verilog代码实现如下:

//输出占空比为50%\20%、频率为500KHz的波形 reg [7:0]cycle_cnt; reg pwm20_sig_r; reg pwm50_sig_r; always@(posedge fpga_clk or negedge rst_n) begin if(!rst_n) begin cycle_cnt <= 8'd0; pwm20_sig_r <= 1'd0; pwm50_sig_r <= 1'd0; end else begin if(cycle_cnt==cycle-1'd1)//计数器清零,同步两个信号相位 begin cycle_cnt <= 8'd0; pwm20_sig_r <= 1'd1; pwm50_sig_r <= 1'd1; end else if(cycle_cnt==puty_50-1'd1) //变换占空比为50%的波形 begin pwm50_sig_r <= 1'd0; cycle_cnt <= cycle_cnt + 8'd1; end else if(cycle_cnt==puty_20-1'd1) //变换占空比为20%的波形 begin pwm20_sig_r <= 1'd0; cycle_cnt <= cycle_cnt + 8'd1; end else //计数器自加 begin cycle_cnt <= cycle_cnt + 8'd1; end end end assign pwm20_sig = pwm20_sig_r; assign pwm50_sig = pwm50_sig_r;

五、 实验步骤及实验结果

1、 新建工程,器件选择SL2S-25E-8U213C,在源文件一栏点击“+”号,将例程下的3个.V文件添加到工程中;分别是包含顶层模块的pwm.v文件、包含输出信号生成模块的pwm_ctrl.v文件和包含复位信号产生模块的rst_n.v文件。

2、 点击左侧边栏的“设计管理”按钮,弹出界面中选择顶层模块,点击“语法检查”,看工程代码有无报错。

3、 语法检查通过后点击主界面的“全部运行”按钮进行编译,生成bit文件。

4、 将下载器连接到iCore3L 双核心板。

5、 给iCore3L供电,将编译生成的bit文件下载到FPGA中。

六、 拓展实验

1、 改变cycle和puty参数,观察信号变化。