| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-03-02 | gingko | 初次建立 |

实验十三:3-8译码器实验——FPGA实现3-8译码器

一、 实验目的与意义

- 掌握3-8译码器的原理。

- 掌握状态机的使用方法。

- 掌握QuartusII的使用方法。

二、 实验设备及平台

- iCore4T 双核心板。

- iTool A(或相同功能)仿真器。

- USB Type C线缆。

- Keil MDK 开发平台。

- Quartus开发平台。

- 电脑一台。

三、 实验原理

- 译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另一个代码。译码是编码的反操作。根据输入和输出信号数量的关系译码器分为全译码器和部分译码器两类。

- 3-8译码器是一种常见的全译码器,输入是3位的二进制代码,共有8种组合,输出是与这8种组合对应的8个输出信号。译码器将每种二进制的代码组合译成对应的一根输出线上的高、低电平信号。其框图如图13.1所示。

- 根据3-8译码器的逻辑功能可知其逻辑真值表如表13.1所示。

- 表13.1 3-8译码器逻辑真值表

| 输入 | 输出 | |||||||||

| a2 | a1 | a0 | y7 | y6 | y5 | y4 | y3 | y2 | y1 | y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

四、 代码讲解

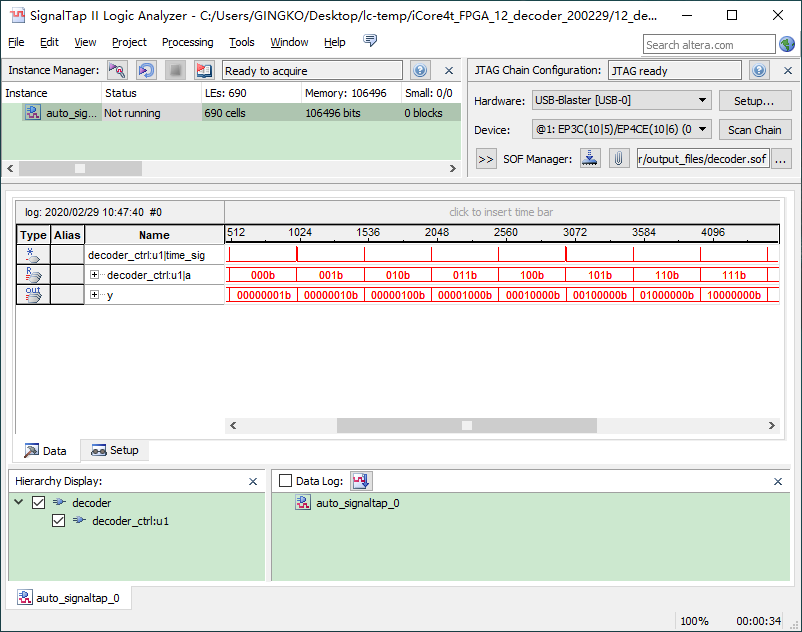

- 本实验首先通过内部程序自身产生输入信号a,并设置一个20us的定时器根据编码器的工作原理依次切换输入信号的值;然后通过状态机根据逻辑真值表将输入信号译码成对应的输出信号,改变8根输出线上的高低电平。其代码如下:

/*************************************************/ //利用状态机实现3-8译码器的输出信号,输出译码信号与真值表一致 reg [7:00]y_r; always@(posedge clk_25m or negedge rst_n) begin if(!rst_n) begin y_r <= 8'b000000000; end else begin case(a) 3'b000:begin y_r <= 8'b00000001; end 3'b001:begin y_r <= 8'b00000010; end 3'b010:begin y_r <= 8'b00000100; end 3'b011:begin y_r <= 8'b00001000; end 3'b100:begin y_r <= 8'b00010000; end 3'b101:begin y_r <= 8'b00100000; end 3'b110:begin y_r <= 8'b01000000; end 3'b111:begin y_r <= 8'b10000000; end default:begin y_r <= 8'b000000000; end endcase end end assign y = y_r;

五、 实验步骤及实验结果

六、 拓展实验

- 设计一个部分译码器(如:4-10译码器),观察信号变化。