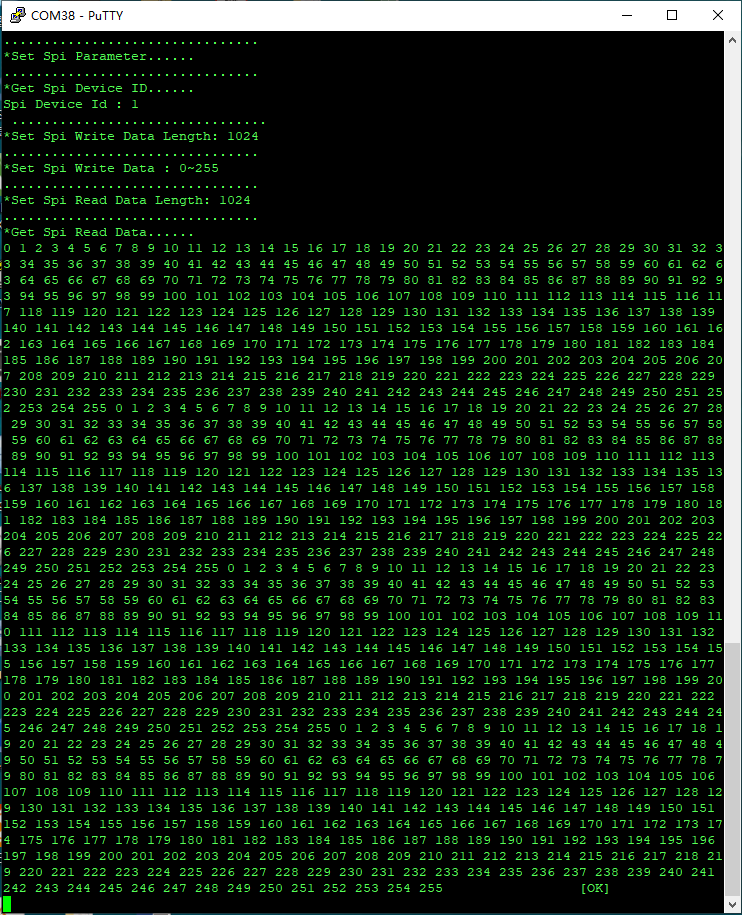

本实验基于ARM+FPGA构架,通过ARM首先发送查询ID指令,然后依次通过指令设置写数据的长度、写数据地址、读数据的长度、读数据的地址,然后对比写入数据和读出数据是否一致判断数据是否写入成功,从而基于SPI总线实现ARM与FPGA之间的通信。

1、更改写数据长度、写数据地址、读数据长度、读数据地址参数时,秩序更改初始化值即可,代码如下:

注意:在设置过程中,地址和长度之和不能大于1024,这是由FPGA内部设置的RAM容量决定的。

//Parameter Value

//注意:地址和长度之和不能大于1024

write_address = 0;

write_length = 1024;

read_address = 0;

read_length = 1024;

//------------------------------------------------//

////////////////按字节接收SPI发送过来的数据//////////////

///////接收模块///////

reg [3:0]receive_state;

reg [7:0]data_in;

reg [7:0]receive_byte_r;

reg spi_rx_en_r;

always@(posedge spi_clk or negedge rst_n or posedge cs_delay)

begin

if((!rst_n)||(cs_delay))

begin

receive_state <= 4'd0;

receive_byte_r <= 8'd0;

data_in <= 8'd0;

spi_rx_en_r <= 1'd0;

end

else //低时钟时可以利用提取沿的方式

begin

case(receive_state) //从高位开始接收数据,每8个spi_clk时钟接收一个Byte

4'd0:begin

receive_state <= receive_state + 1'd1;

data_in <= {data_in[6:0],spi_mosi};

spi_rx_en_r <= 1'd0;

end

4'd1,4'd2:begin

receive_state <= receive_state + 1'd1;

data_in <= {data_in[6:0],spi_mosi};

end

4'd3:begin

receive_state <= receive_state + 1'd1;

data_in <= {data_in[6:0],spi_mosi};

spi_rx_en_r <= 1'd1;

end

4'd4,4'd5:begin

receive_state <= receive_state + 1'd1;

data_in <= {data_in[6:0],spi_mosi};

spi_rx_en_r <= 1'd0;

end

4'd6:begin

receive_state <= receive_state + 1'd1;

data_in <= {data_in[6:0],spi_mosi};

end

4'd7:begin

receive_state <= 4'd0;

data_in <= {data_in[6:0],spi_mosi};

receive_byte_r <= {data_in[6:0],spi_mosi};

end

endcase

end

end

//------------------------------------------------//

///////发送模块///////

reg [3:0]send_state;

reg spi_miso_r;

reg spi_tx_en_r;

reg [7:0]data_out;

always@(negedge spi_clk or negedge rst_n or posedge cs_delay)

if((!rst_n) || (cs_delay))

begin

send_state <= 4'd0;

spi_tx_en_r <= 1'd0;

data_out <= 8'd0;

end

else

begin

case(send_state)

4'd0:begin

spi_miso_r <= data_out[7];

send_state <= send_state + 1'd1;

end

4'd1:begin

spi_miso_r <= data_out[6];

send_state <= send_state + 1'd1;

end

4'd2:begin

spi_miso_r <= data_out[5];

send_state <= send_state + 1'd1;

end

4'd3:begin

spi_miso_r <= data_out[4];

send_state <= send_state + 1'd1;

end

4'd4:begin

spi_miso_r <= data_out[3];

send_state <= send_state + 1'd1;

spi_tx_en_r <= 1'd0;

end

4'd5:begin

spi_miso_r <= data_out[2];

send_state <= send_state+ 1'd1;

spi_tx_en_r <= 1'd1;

end

4'd6:begin

spi_miso_r <= data_out[1];

send_state <= send_state + 1'd1;

spi_tx_en_r <= 1'd0;

end

4'd7:begin

data_out <= send_byte;

spi_miso_r <= data_out[0];

send_state <= 4'd0;

spi_tx_en_r <= 1'd0;

end

endcase

end