| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-03-17 | gingko | 初次建立 |

实验八:软件复位信号实验——全局复位信号

一、 实验目的与意义

- 掌握Verilog HDL语言的使用方法。

- 掌握QuartusII的使用方法。

- 掌握软件复位信号的工作原理及使用方法。

二、 实验设备及平台

- iCore4T 双核心板。

- iTool A(或相同功能)仿真器。

- USB Type C 线缆。

- Keil MDK 开发平台。

- Quartus开发平台。

- 电脑一台。

三、 实验原理

- 复位指的是在可编程器件、可编程控制器等电子设备中,为防止程序跑飞或者保证多个子程序同时运行,在程序中手动或者自动的方法使软硬件恢复到一个特定的工作节点的过程,而这个手动或自动控制的信号就是复位信号。

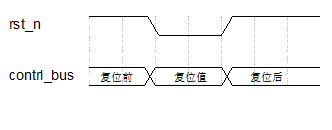

- 在FPGA程序中,一个复杂的功能由多个子模块共同完成,为了保证各个子模块同时运行,在程序内部设定一个全局复位信号,属于异步复位信号。其工作原理时序如图8.1所示:

- 如图所示,其复位原理是:将复位信号作为程序控制的触发信号,在复位信号(rst_n)下降沿处对控制总线进行复位,将其赋值为复位值,有效复位信号(低电平)结束后,可根据需要对控制总线重新进行赋值。

四、 代码讲解

- 复位信号的产生原理是:首先做一个产生复位信号的计数器always块,然后利用条件运算符和关系运算符产生一个短时间内具有低电平的的信号,将该信号作为复位信号。其代码如下:

//生成复位信号的计数器,采用时许逻辑语言描述 reg [31:0]rst_cnt; always@(posedge clk_25m) begin if(rst_cnt==32'd250000000) begin rst_cnt<=32'd250000000; end else begin rst_cnt <= rst_cnt + 1'd1; end end wire rst_n = ((rst_cnt>32'd125000000) && (rst_cnt<32'd225000010)) ? 1'd0 : 1'd1;

五、 实验步骤及实验结果

1、将硬件正确连接,如上图所示。

1、将硬件正确连接,如上图所示。

2、将编写好的代码进行编译,并下载到开发板中;

3、观察其实验结果——程序下载后,首先开发板上FPGA_LED为亮状态,经过大约5秒钟,复位信号有效,对FPGA_LED进行复位置为灭状态,复位大约4秒钟,再次点亮FPGA_LED。

六、 拓展实验

1、通过Signaltap工具采集复位信号和led控制信号,看是否与其工作原理一致;