乘法器实验_乘法器使用

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-07-02 | gingko | 初次建立 |

实验八:乘法器实验——乘法器IP核的调用

一、 实验目的与意义

- 了解乘法器。

- 掌握调用乘法器IP核的用法。

- 掌握QuartusII集成开发环境的的使用方法。

二、 实验设备及平台

三、 实验原理

- 通过FPGA的一个I/O口连接开发板上的LED:设定I/O为输出模式。调用内部乘法器IP核完成计算后,改变输出LED的状态。

四、 实验步骤

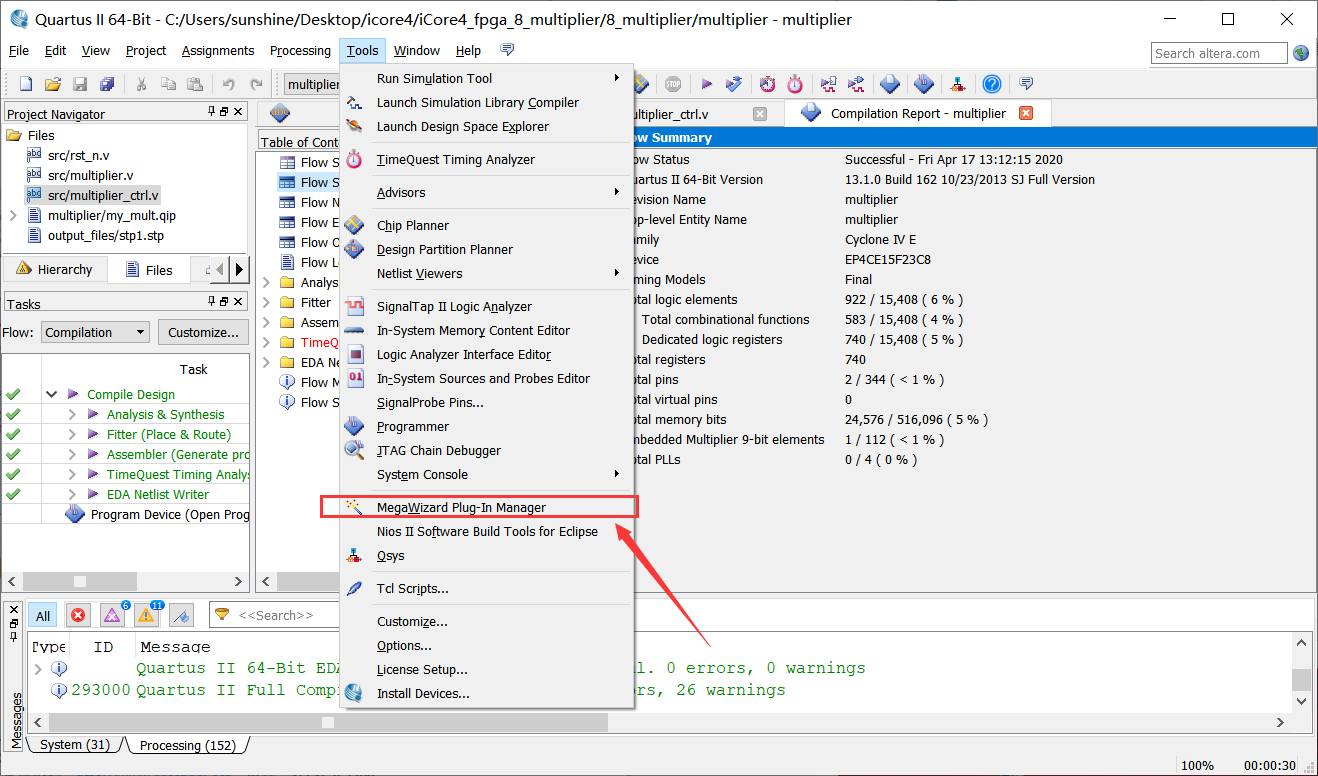

1、新建工程,并新建verilog文件,本例程仍然按模块划分非三个verilog文件。然后打开Tool→Megawizard Plug-In Manager。如下图所示。

2、选择第一个选项新建,点击Next。如下图所示,

2、选择第一个选项新建,点击Next。如下图所示,

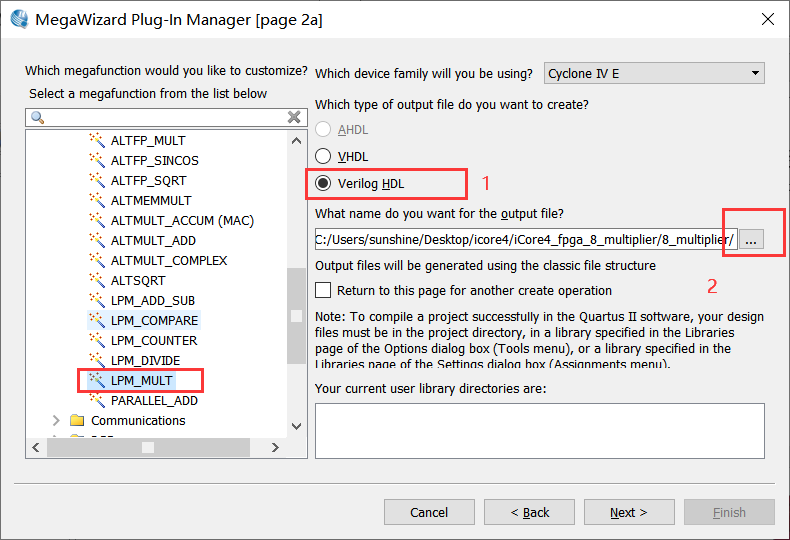

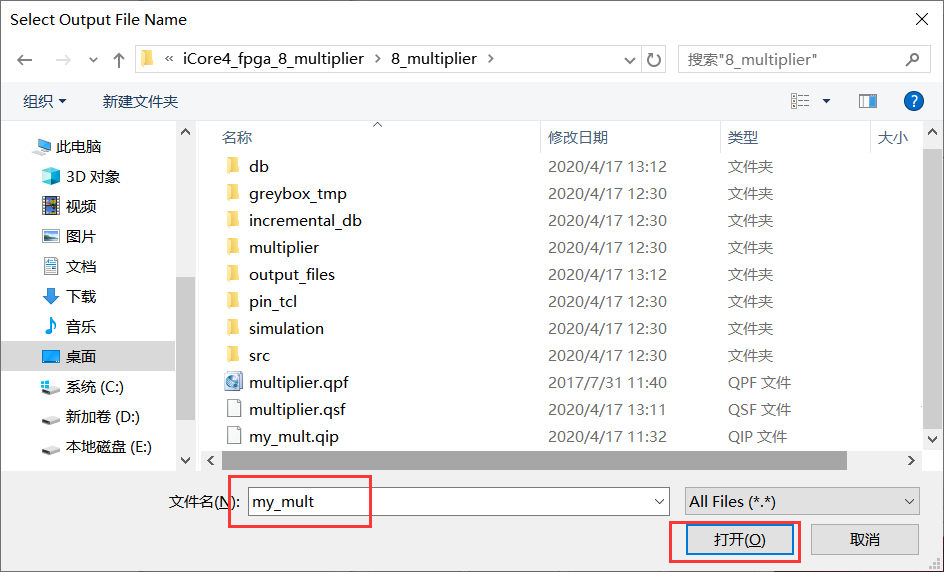

3、在左侧的栏里Arithmetic文件夹下找到并选中LPM_MULT,在框1处选择Verilog HDL,再点击框2中按钮选择存放目录,如下图所示。然后点击Next。

3、在左侧的栏里Arithmetic文件夹下找到并选中LPM_MULT,在框1处选择Verilog HDL,再点击框2中按钮选择存放目录,如下图所示。然后点击Next。

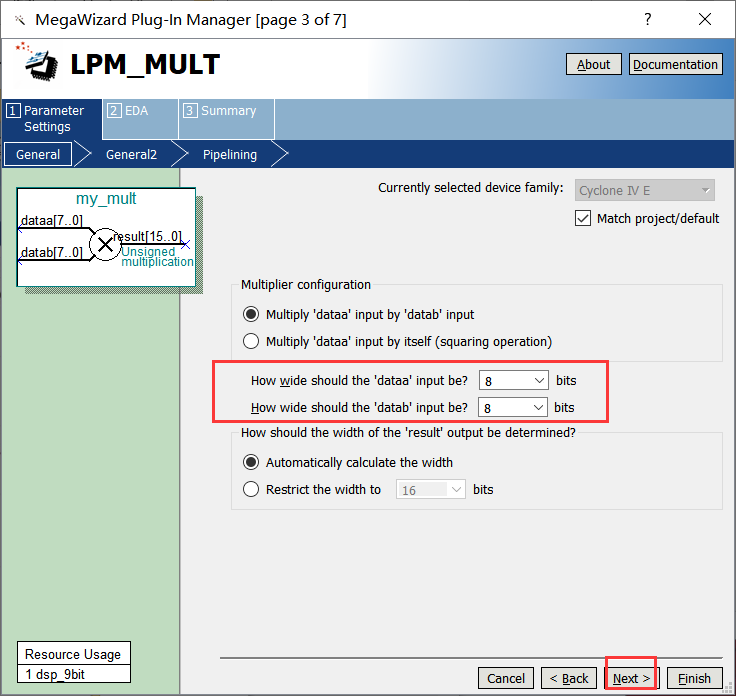

4、在框1处选择乘法器输入数据的宽度,此处以8位宽度为例,如下图所示,然后点击Next。

4、在框1处选择乘法器输入数据的宽度,此处以8位宽度为例,如下图所示,然后点击Next。

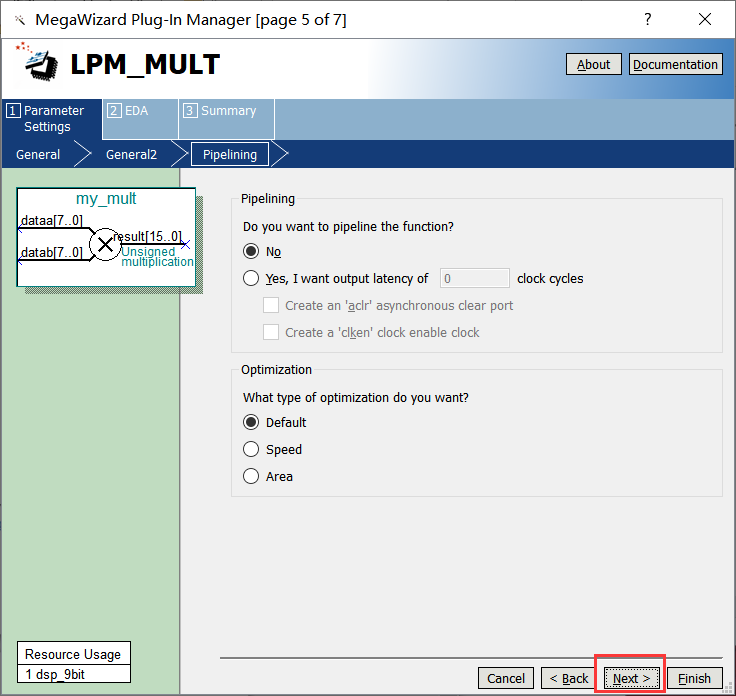

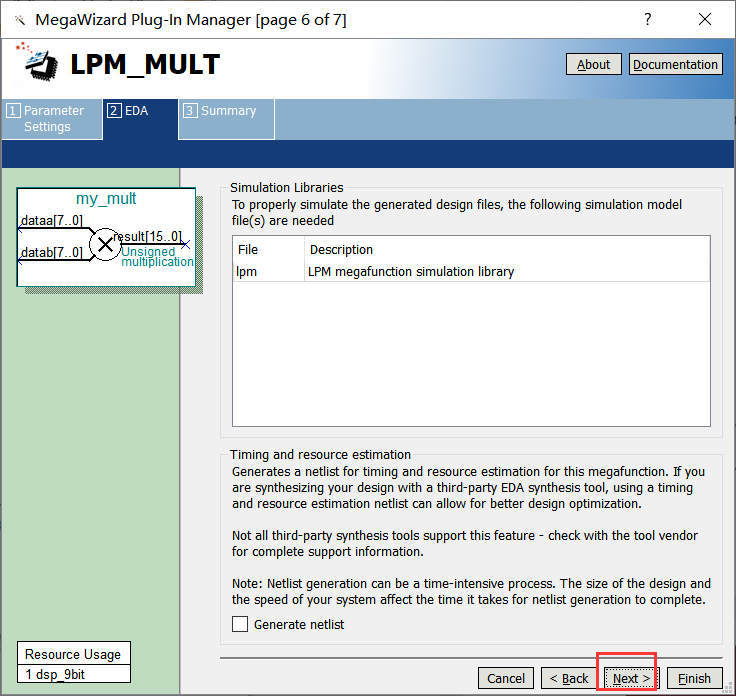

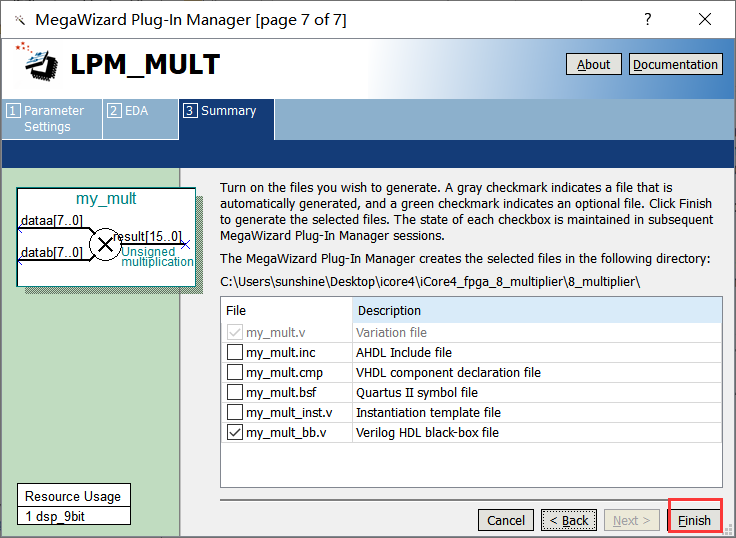

5、接下来的几页保持默认设置直接点击Next,最后点击Finish即可。

5、接下来的几页保持默认设置直接点击Next,最后点击Finish即可。

6、此时就完成了乘法器的创建。在程序中调用该乘法器即可实现乘法器功能。相关代码如下。

6、此时就完成了乘法器的创建。在程序中调用该乘法器即可实现乘法器功能。相关代码如下。

//---------------实例化mult模块并调用该模块进行乘法器运算---------------// my_mult u1( .dataa(a), .datab(a), .result(out) ); //---定义fpga_ledg与乘法器输出的第六位状态(为0时led点亮)保持相应一致---// wire [15:0]out; assign fpga_ledg = out[6];

7、接着完成相关配置、引脚分配、编译等工作后,将配置文件下载至iCore4开发板。

8、接着按照前面教程所述,使用Signaltap II采集乘法器的输入输出信号,观察是否与程序描述一致。

五、 实验现象

- Signaltap II采集到的信号与Verilog描述功能一致。

- iCore4上与FPGA相连的绿色LED灯闪烁。

乘法器实验_乘法器使用.txt · 最后更改: 2022/03/22 10:28 由 sean