| 银杏科技有限公司旗下技术文档发布平台 |

| 技术支持电话 | 0379-69926675-801 |

| 技术支持邮件 | Gingko@vip.163.com |

| 版本 | 日期 | 作者 | 修改内容 |

| V1.0 | 2019-12-25 | gingko | 初次建立 |

实验三十二:千兆以太网传输

一、实验目的与意义

了解以太网帧结构和IP协议以及UDP协议的定义。

了解PHY芯片RTL8211EG的引脚设定和信号规范。

学习千兆以太网传输原理和物理层接口GMII的时序控制方法。

掌握GMII接口千兆以太网的UDP协议通信模块设计。

二、实验设备及平台

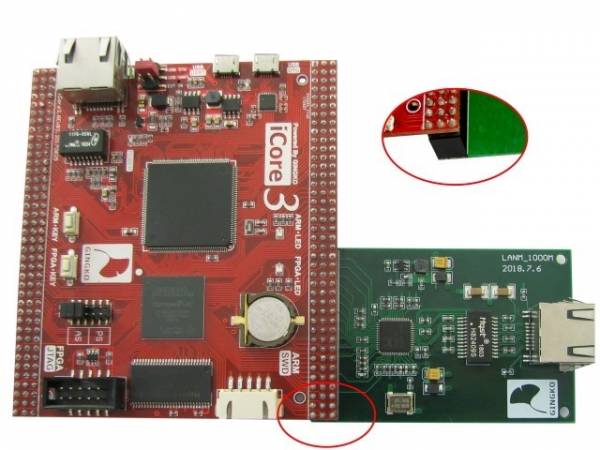

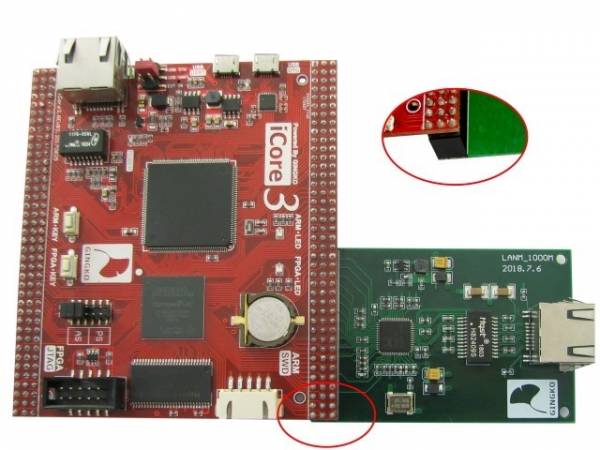

iCore3 双核心板( FPGA型号为EP4CE10F17)

点击购买-

Blaster(或相同功能的)仿真器和USB线缆

点击购买Micro USB线缆和千兆速率网线。

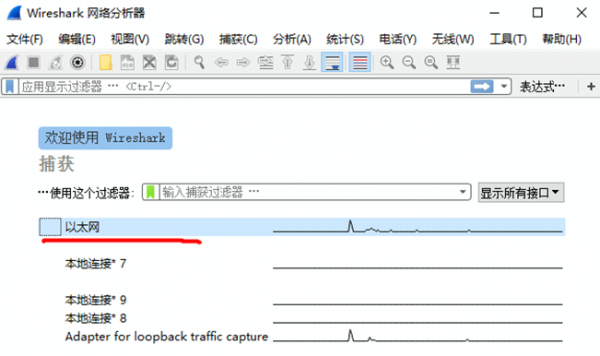

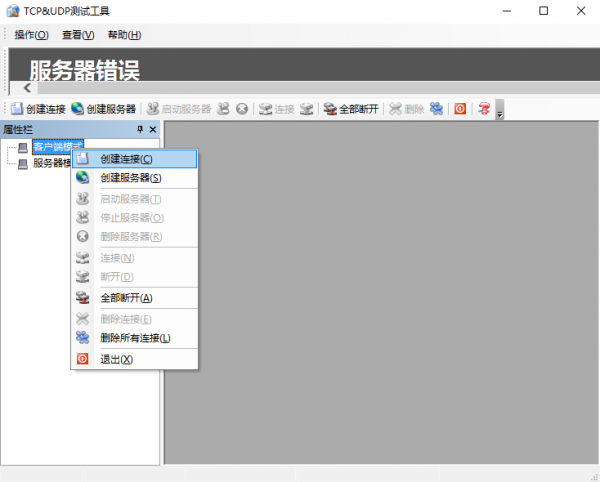

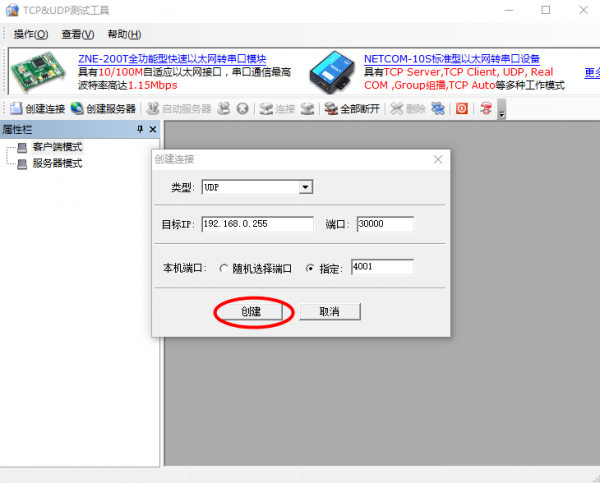

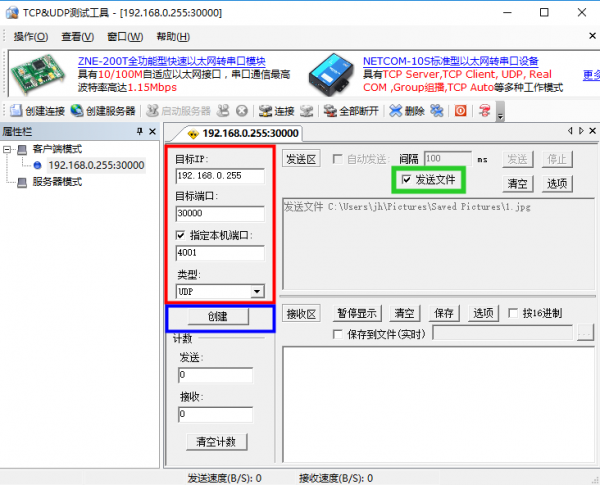

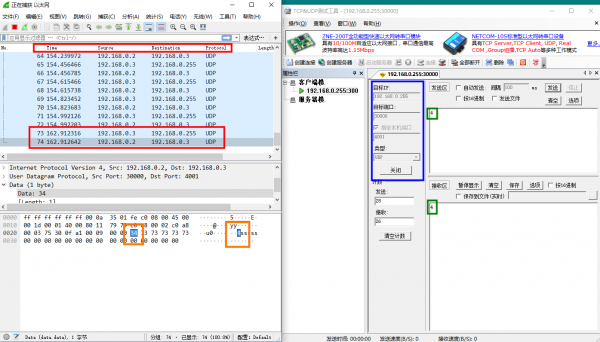

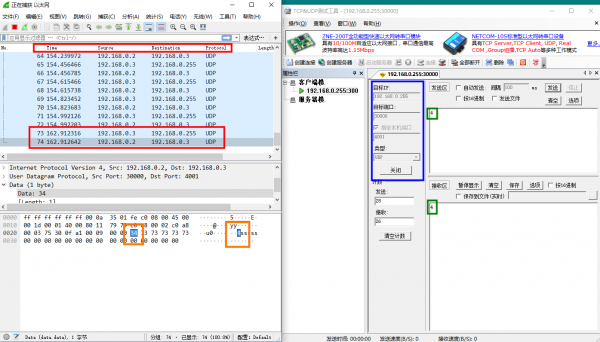

QuartusII开发软件(本实验中使用的是13.1版本)、TCP&UDP测试工具软件、wireshark抓包软件。

一台带有千兆网卡的电脑。

注意事项1: 注意FPC转接板和千兆网卡模块下边缘对齐连接,如图30-1红圈内标注所示。

注意事项1: 注意FPC转接板和千兆网卡模块下边缘对齐连接,如图30-1红圈内标注所示。

注意事项2: 确认PC端网卡和网线是千兆速率,网线的水晶头连接紧密稳定。

注意事项3: 下载前请确认绑定的引脚或者加载的pin.tcl文件和千兆网与核心板之间的连接引脚相对应。

三、实验原理

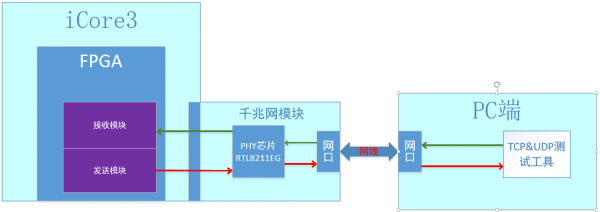

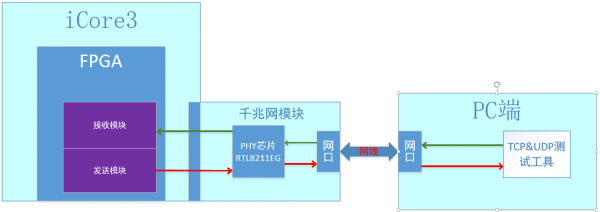

1、数据收发流程

首先确认实验目的,本次实验可以划分为实现两个目的:

1)FPGA接收PC发送的数据并实现数据包的解析。

2)FPGA打包数据,并发送至PC。 =

具体细分的话,要实现FPGA单次收发数据的功能,和测试FPGA大量发送数据至PC端的极限速率。

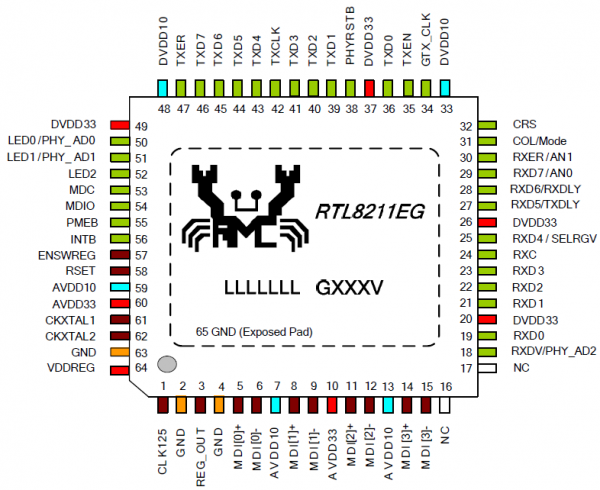

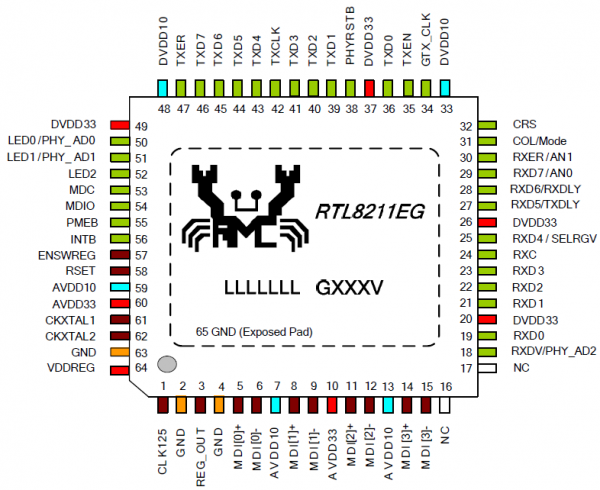

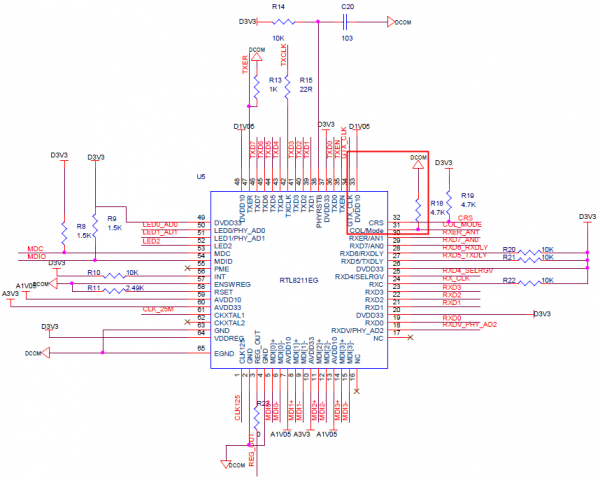

2、PHY芯片RTL8211EG

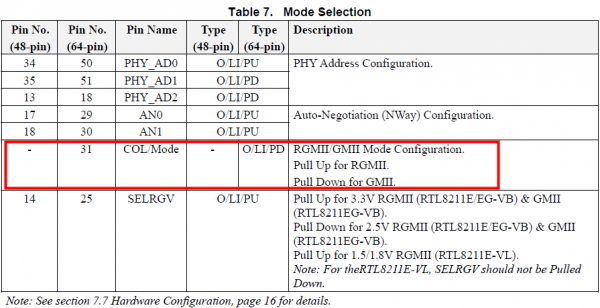

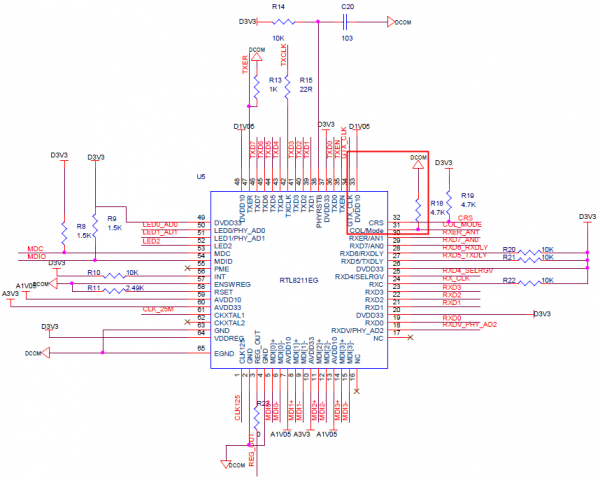

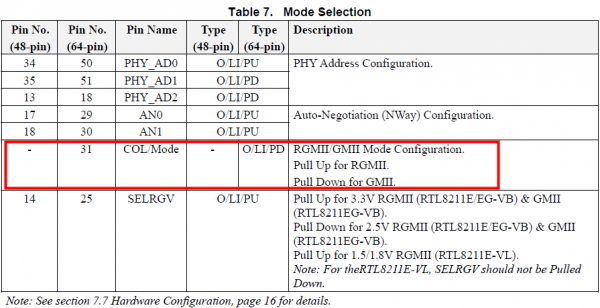

RTL8211EG作为高集成度的网络收发芯片,支持多种收发模式,支持GMII和RGMII两种接口。可以通过配置,使其工作在RGMII或者GMII模式。GMII接口使用引脚较多,采用时钟单边沿采样数据。而RGMII则在时钟的上升沿和下降沿都采样数据,节约引脚但增加了时序控制的复杂度。至于选用哪种接口,视需要而定。本实验的千兆网模块已经通过硬件配置使RTL8211EG工作在GMII模式,寄存器配置采用的是默认设置。因此,了解PHY芯片的硬件驱动原理和处理好数据的收发即可。

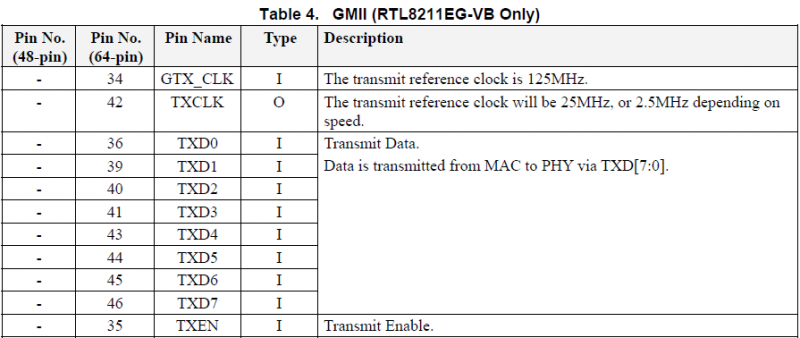

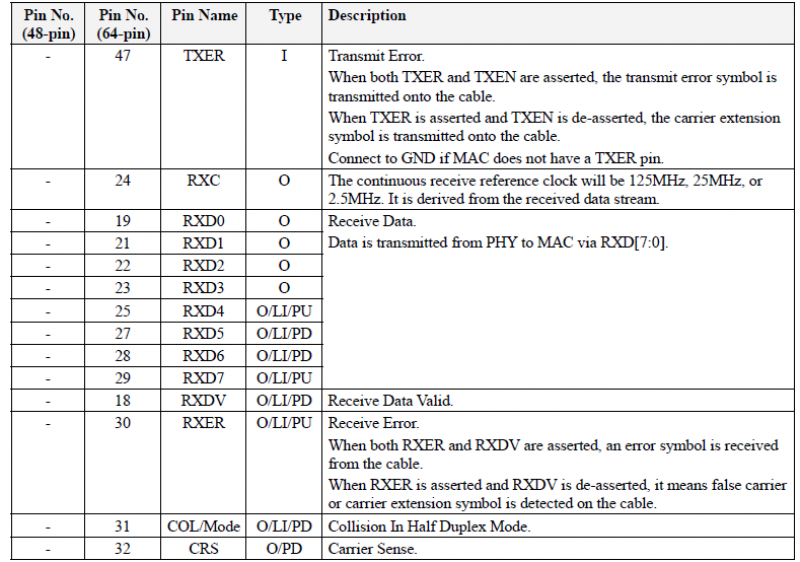

通过阅读RTL8211EG芯片手册中GMII模式下对应引脚的介绍,可以知道各引脚的编号,输入输出类型以及功能描述等。包括数据收发对应的引脚以及模式配置引脚。

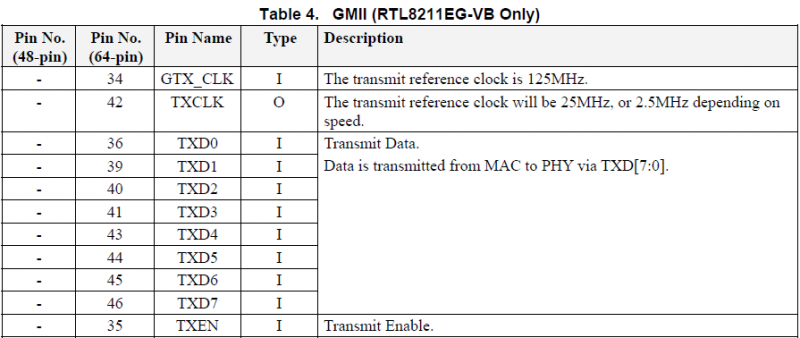

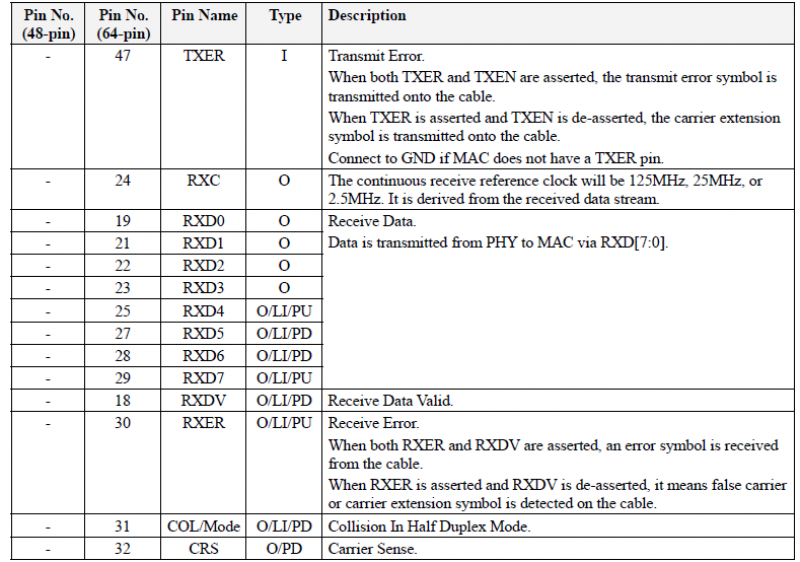

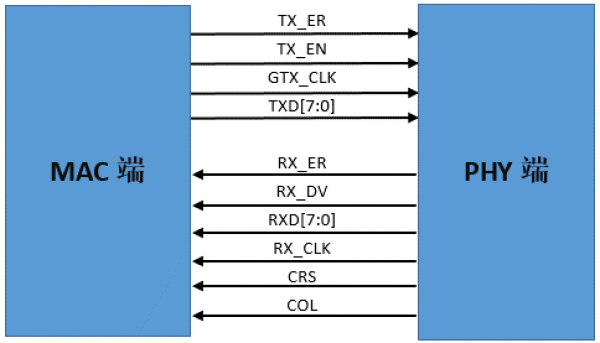

3、GMII接口

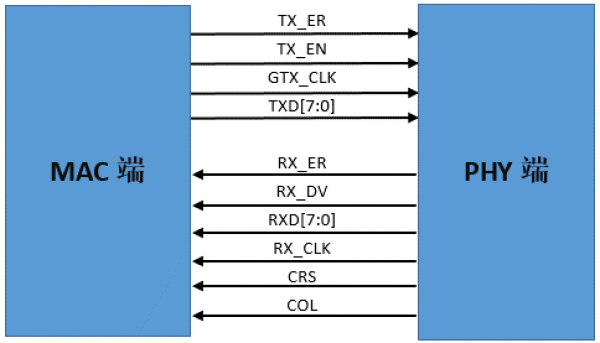

GMII接口采用8位数据通道,125MHz的工作时钟,可达1000Mbps的传输速率。符合IEEE802.3-2000标准以太网协议。在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK。本次实验是千兆网实验,使用的是GTX_CLK。

TXCLK也是发射参考时钟,跟PHY芯片的传输速率有关。这个时钟是由PHY芯片提供,指向MAC侧的。100Mbps速率下,TXCLK的频率为25MHz,10Mbps速率下,TXCLK频率为2.5MHz。

RXC也是PHY芯片提供的连续接收参考时钟。100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。把FPGA看成MAC端,千兆网模块看成PHY端,他们之间的信号关联如下图所示:

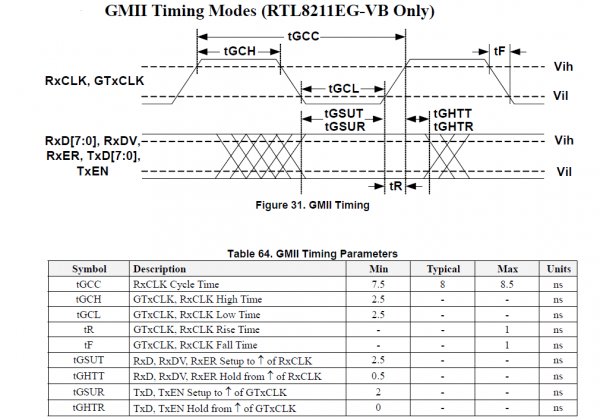

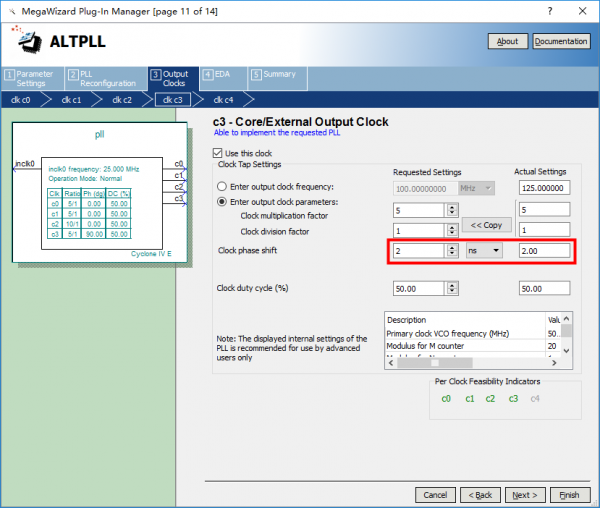

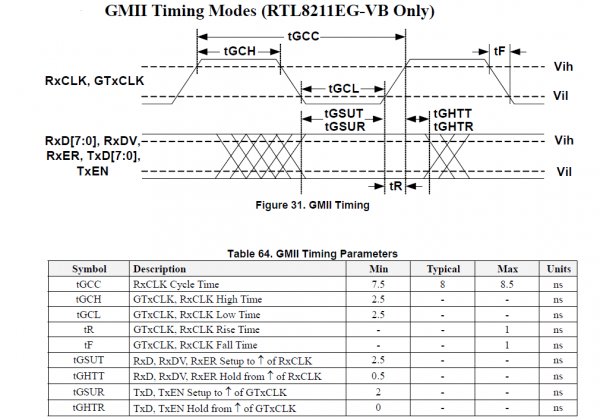

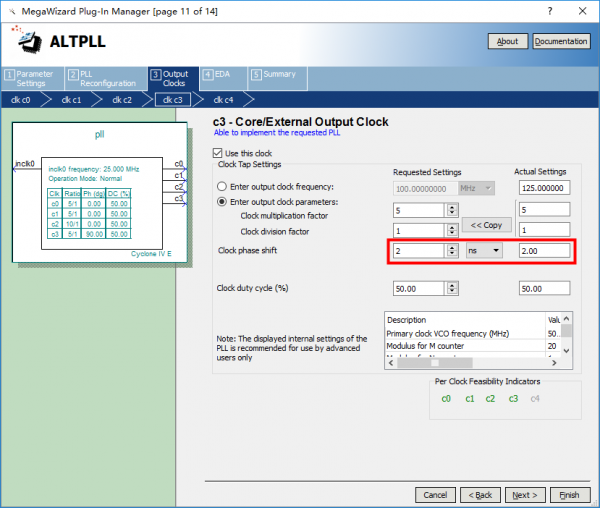

图中可以看出,tGCC即RXCLK时钟周期,典型值是8ns,因为时钟频率是125MHz。tGSUR到时钟上升沿的最小值是2ns,也就是TXD的跳变沿要比GTXCLK的上升沿最少要早2ns。我们代码中命名为GTX_CLK(tGCC)的时钟,由PLL IP核输出。在PLL IP核关于此时钟的设定中我们设置了时钟沿延后2ns。如下图红框中所示:

四、以太网

1、以太网帧结构

| 前导码 | SFD | 目标地址 | 源地址 | 类型 | 数据(IP数据包) | CRC |

| 7byte | 1byte | 6byte | 6byte | 2byte | 46-1500byte | 4byte |

| 字段名称 | 字段含义 |

| 前导码 | 7个字节的0x55,用于以太网前导 |

| SFD | 1个字节的帧起始符,0xD5,表示以太网数据帧的开始 |

| 目标地址 | 接收方MAC地址,6字节 |

| 源地址 | 发送方MAC地址,6字节 |

| 类型 | 网络协议类型,0x0800表示为IP协议,0x0806表示是ARP协议 |

| 数据 | 46-1500字节,不够最少字节的用0x00填充。 |

| CRC | CRC-32 校验,从目标地址到数据结束都为需校验内容 |

上面两个表格,是对帧结构以及帧结构中各字段含义的讲解。可以这么理解,一帧数据就是依次由7个字节的0x55,一个字节的0xd5,12个字节的MAC地址,2个字节的IP协议类型值,一串长度不定的数据,和4个字节的CRC校验位组成。

接收端首先接收到的是由7个字节的0x55构成的前导码,然后收到一个0xD5作为帧起始符。起始符之后收到目标MAC地址,源MAC地址,然后是网络协议类型。本实验采用的是IPv 4网络协议,这个协议类型字段的值就应该是0x0800。然后是数据长度以及CRC-32的校验数据。

发送端与此类似,先发送7个字节的0x55,接着发送一个字节的0xd5,然后按顺序发送MCA地址协议类型以及数据和CRC校验值。

标准以太网帧长度最小值为64 字节,最大值1518字节,有兴趣的可以查一下这两个数是怎么算的。这里的64和1518都是从目标地址开始算起的,不包括前导码和SFD,这也是为什么帧数据除了头部和校验以外的长度范围是46字节到1500字节。

2、IP协议

| 版本(4bit) | 首部长度(4 bit) | 服务类型(1 byte) | 总长度(2 byte) |

| 标识(2 byte) | 标识(3 bit) | 片偏移(13 bit) |

| 生存时间(1 byte) | 协议(1 byte) | 首部校验和(2byte) |

| 源IP地址(4 byte) |

| 目标IP地址(4 byte) |

| 选项(如果有) |

| 数据 |

| 字段名称 | 字段含义 |

| 版本 | IP协议版本,IPv 4 的协议版本号为4 |

| 首部长度 | IP包头的长度,单位为4byte,即首部长度字段的值为5时,包头长度为20byte |

| 服务类型 | 只有在使区分服务时,本字段才起作用 |

| 总长度 | IP包的总长度,包括包头和数据 |

| 标识 | 用于分包/拼包 |

| 标志 | 用于分包/拼包 |

| 片偏移 | 用于分包/拼包 |

| 生存时间 | 数据在网络中的寿命,每经过一个路由器 -1,减到0时数据无效 |

| 协议 | 指明数据字段中的数据包协议类型,UDP(17),TCP(6) |

| 首部校验和 | IP包头部检验,只检验数据报的首部,不包括数据部分 |

| 源IP地址 | 发送方IP地址 |

| 目标IP地址 | 接收方IP地址 |

| 选项 | 可选字段(长度可变) |

| 数据 | IP数据包的数据部分(既UDP包) |

3、UDP协议

| 源端口号(2 byte) | 目标端口号(2 byte) |

| UDP长度(2 byte) | UDP长度(2 byte) |

| 数据(x byte) (如果有) |

| 字段名称 | 字段含义 |

| 源端口号(2 byte) | 发送方端口 |

| 目标端口号(2 byte) | 接收方端口 |

| UDP长度(2 byte) | UDP数据包长度,包括包头和数据 |

| UDP长度(2 byte) | UDP包头部检验,只检验数据报的首部,不包括数据部分 |

| 数据(x byte) | UDP数据包中的数据(也是帧结构的有效数据) |

4、CRC校验

五、代码讲解

1、数据接收模块

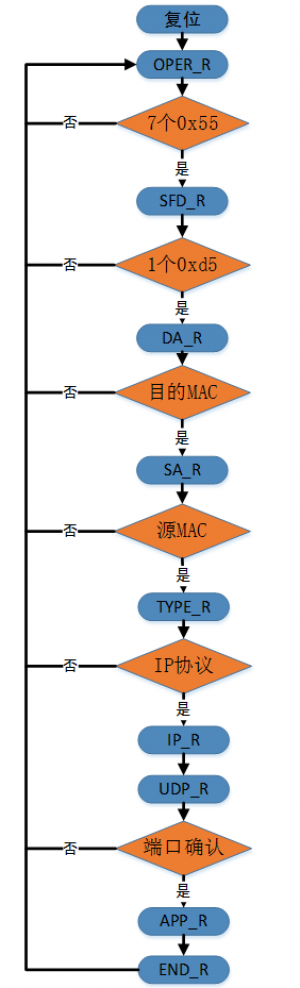

首先定义一些寄存器,用于存储接收到的头部信息。然后进行寄存器的初始化。由于数据是顺序接收和判断的,这里采用了case语句,并嵌入if判断语句控制case语句的跳转。只要图中的判断语句任意处出现否,则跳回数据接收模块的PRE_R状态。

接下来再来看一下代码部分。结合前面的学习,理解起来就比较容易了。首先来看一下数据接收模块,其功能是判断数据包是否符合协议规范,并解析出数据包中的数据。数据接收部分首先是对状态机的状态跳转控进行赋值,其次是对寄存器的定义,如代码注释所示:

//-------------------接收数据-------------------//

parameter

PRE_R = 4'd0,

SFD_R = 4'd1,

DA_R = 4'd2,

SA_R = 4'd3,

TYPE_R = 4'd4,

ARP_R = 4'd5,

IP_R = 4'd6,

UDP_R = 4'd7,

APP_R = 4'd8,

END_R = 4'd9;

reg [3:0] STATE_R;//接收状态

reg [7:0] cnt_R;//接收使用的计数器

reg [47:0]dest_mac;//目标MAC地址

reg [47:0]source_mac;//源MAC地址

reg [15:0]type;//接收数据的协议类型

reg [223:0]arp_data;//ARP中的数据

reg [159:0]ip_head;//IP报头

reg [63:0]udp_head;//UDP数据报头

reg [7:0]buffer[63:0];//数据缓存区

reg [15:0]data_lenght;//数据长度

reg [11:0] i;//数据计数器

reg [7:0]data1;

reg UDP_SD_EN;

这里有个寄存器变量data1,它的作用就像我们过安检时用的托盘。将物品放入托盘中,经过安检,取走物品后的托盘再次放入物品,过安检。于此类似,依次接收的数据,先放到变量data1中,然后对变量data1的值进行判断,是否符合帧格式,符合的话则用下一个输入值覆盖当前data1中的值,继续进行判断。

数据接收模块的主要部分是一个case语句,在case语句的不同分支中,实现对帧结构的解析和数据的读取。首先是对寄存器变量的初始化,使其在复位之后处于一个确定的状态。然后是对帧的起始标志的判断,就在PRE_R的状态判断七次存入data1中的值,如果是7个0x55,那么说明输入的前七个数值符合帧起始符,就跳转到下一个状态,判断存入data1中的值是否为帧起始符0xd5。如果是0xd5,继续判断,否则调出判断,返回初始状态。如果发送过来的是一个完整的帧数据包,则可以解析出帧数据的MAC地址,协议类型,IP地址,端口类型以及数据长度,校验码等信息。

UDP协议中,在UDP数据包里定义了数据部分的长度。那么,当我们解析出UDP数据包后,也就知道了这次发送的有效数据的长度。有了这个数据长度值,就可以在缓存接收到的数据时只存输入进来的有效数据了。

在解析UDP包头的时候,也对目标端口进行了判断。要保证TCP&UDP测试软件设置的时候的端口值和此处代码中的端口值保持一致,否则会导致数据接收失败。

UDP_R:// 接收UDP包头 8 byte

begin

if(cnt_R == 8'd7)

begin

udp_head <= {udp_head[55:0],data1};

cnt_R <= 8'd0;

if(udp_head[39:24] == 16'h7530)//16进制的7530是十进制的30000,即设定的端口号

begin

data_lenght <= udp_head[23:8] - 16'd8;//提取数据长度,udp_head的[23:8]定义了UDP包的数据长度,包括了UDP头部,所以这里要减去UDP头部的数据长度8

STATE_R <= APP_R;

end

else

begin

STATE_R <= PRE_R; //如果端口不匹配,则返回PRE_R状态

end

end

else

begin

udp_head <= {udp_head[55:0],data1};

cnt_R <= cnt_R +1'd1;

end

end

2、数据发送模块

reg flag;//连发模式标志位

reg flag_h;//连发开始位标志

reg flag_l;//连发停止位标志

always@(posedge RX_CLK or negedge rst_N )

if(rst_N==1'b0)

flag_h<=1'b0;

else if((buffer[0]==8'h33)&&(STATE_UT==APP_R))//连发开始位标志3

flag_h<=1'b1;

else

flag_h<=1'b0;

always@(posedge RX_CLK or negedge rst_N )

if(rst_N==1'b0)

flag_l<=1'b0;

else if((buffer[0]==8'h73)&&(STATE_UT==APP_R))//连发停止位标志s

flag_l<=1'b1;

else

flag_l<=1'b0;

always@(posedge RX_CLK or negedge rst_N )

if(rst_N==1'b0)

flag<=1'b0;

else if(flag_l) //连发状态停止

flag<=1'b0;

else if(flag_h==1'b1)//连发状态开始

flag<=1'b1;

看这段代码,定义了另外两个寄存器变量,用于控制flag信号,那么控制flag变量的flag_h和flag_l又是如何产生的呢?在代码中,通过对数据接收模块状态和接收的第一个字符的值进行综合判断,当接收模块处于接收有效数据,且第一个接受到的数值为“3”的时候,拉高一个时钟周期的flag_h信号。flag_l则根据接收数据的第一个字符为“s”的时候拉高一个时钟周期。这里大家应该有注意到,当我们对数据接收缓存器的第一个值buffer[0]进行判断时,对比值是8’h33和8’h73。这里的8’h33和8’h73分别是ASCII码“3”和“s”对应的16进制数。这是因为我们使用TCP&UDP测试工具给FPGA发送数据的时候选择的是ASCII格式。

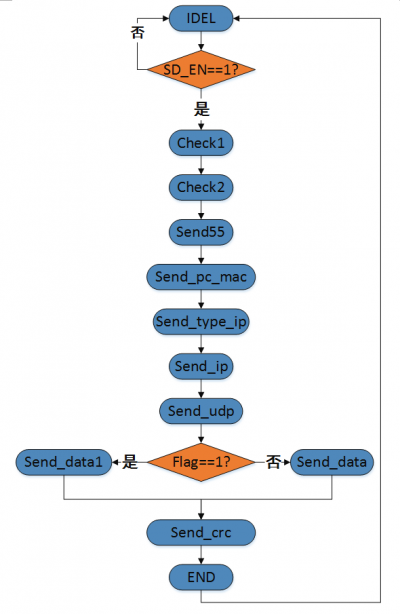

那什么时候开始进入数据发送的流程呢?首先要对帧结构头部寄存器进行初始化,设定MCA地址,协议类型,版本号和端口号等信息。然后进入IDEL状态,等待SD_EN信号为高,则进行数据长度的初始化并进入发送状态。

那么这里控制IDEL跳转到下一状态的SD_EN信号是什么作用呢?看下面这段代码就能知道,这个信号相当于一个选择器,当接收到的第一个字符为“3”的时候,flag信号为高,则SD_EN就一直为高电平了。SD_EN为高的时候,数据发送模就一直处于发送使能状态。而flag为低的时候,它的状态和UDP_SD_EN的状态就一样了,也就是FPGA每接收完一帧数据,便发送出一帧数据,并等待下一帧数据发送进来。

reg SD_EN;

always@(posedge clk_125M or negedge rst_N)

if(!rst_N)

SD_EN<=1'b0;

else if(flag)

SD_EN<=1'b1;

else if(!flag)

SD_EN<=UDP_SD_EN;

check1:

begin

if(cnt == 8'd6)

begin//IP计算首部校验和:以16位相加方式加到32位校验和中

ip_check_sum <= {ip_send[0],ip_send[1]} + {ip_send[2],ip_send[3]}+{ip_send[4],ip_send[5]} + {ip_send[6],ip_send[7]} + {ip_send[8],ip_send[9]}+{ip_send[12],ip_send[13]}+{ip_send[14],ip_send[15]}+{ip_send[16],ip_send[17]}+{ip_send[18],ip_send[19]};

crc_reset <= 1'd1;

cnt <= 8'd0;

STATE_UT <= check2;

end

else

begin

cnt <= cnt + 1'd1;

end

end

check2:

begin//IP计算首部校验和:16位相加取反

{ip_send[10],ip_send[11]} = ~(ip_check_sum[15:0] + ip_check_sum[31:16]);

STATE_UT <= send55;

end

然后正式进入数据发送阶段。首先是发送7个0x55和一个0xd5。作为帧数据开始标志,告诉接收设备,做好接收准备。之后就是发送源端和目标端MAC地址,以及协议类型,构成完整的数据帧头部。这里也要注意MAC地址的值和我们软件设置里相互对应。然后是IP数据包头和UDP数据包头部。

在发送完UDP头部之后,将要发送的就是帧内的有效数据了,这里也用flag信号控制了一下状态的跳转。当flag为高的时候,跳转到send_data1状态,否则跳转到send_data状态。

send_udp://发送UDP包头

begin

if(cnt == 8'd7)

begin

data_out <= udp_send[cnt];

cnt <= 8'd0;

data_counter <= 16'd0;

if(flag) //控制发送状态跳转至send_data1

STATE_UT<=send_data1;

else

STATE_UT <= send_data;

end

else

begin

data_out <= udp_send[cnt];

cnt <= cnt +1'd1;

end

end

send_data://发送数据

begin

if(data_lenght < 16'd19)

begin

if(data_counter == 16'd20)

begin

data_out <= buffer[data_counter];

data_counter <= 16'd0;

STATE_UT <= send_crc;

end

else

begin

data_out <= buffer[data_counter]; data_counter <= data_counter + 1'd1;

end

end

else

begin

if(data_counter == data_lenght - 16'd1)

begin

data_out <= buffer[data_counter];

data_counter <= 16'd0;

STATE_UT <= send_crc;

end

else

begin

data_out <= buffer[data_counter]; data_counter <= data_counter + 1'd1;

end

end

end

send_data1:

begin

if(cnt_l==1200)

begin

STATE_UT <=send_crc;

cnt_l<=12'd0;

end

else

begin

data_out<=8'h38;//输出数值随便定义,这里设定的“8”

cnt_l<=cnt_l+1'b1;

end

end

通过对比这两段代码可以知道,send_data和send_data1均是实现数据发送的。

send_data是按照协议流程,进行最小帧长度的判断,并处理,然后将接收数据缓冲寄存器buffer中存储的接收数据依次发送出去。

前面我们有提到,帧数据的长度为46字节到1500字节,这个长度是包括IP协议头部和UDP协议头部的,因此,一帧数据除了IP协议头部和UDP协议头部,携带的有效数据长度在19字节至1400多个字节之间。所以在发送数据的时候我们这里对需要发送的数据的长度做个判断,当发送的数据的长度不够19个字节的时候,就对其进行填充,避免被当成非法帧而丢包。

send_data1则是直接将ASCII码“8”的16进制数值连续1200次发送出去。这里的data_out的值大家给定什么,在TCP&UDP的接收区就可以收到什么。连续发送的次数只要在帧数据长度的最大值和最小值以内都可以。

回过头看一下,大概流程就是,如果接收数据的第一个字符是“3”,则flag信号为高电平。相应的SD_EN信号也为高电平,一直处于发送使能状态。同时由于flag为高,case语句中有效数据发送一直进入send_data1,即连续发送内容为1200个“8”的帧到PC端。数据发送完之后接着发送CRC校验的值,就完成了一帧数据的发送。

六、操作流程和测试结果

1、操作步骤:

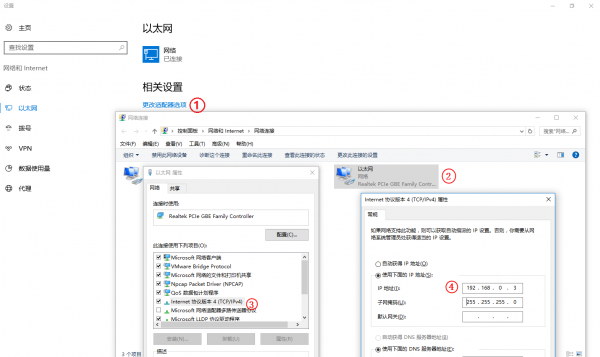

2、测试结果:

勾选【连续发送】后可以看到接收区不断的接收和发送区相同的内容。这是TCP&UDP测试软件持续将发送区内容发送至FPGA、FPGA再把接收到的内容发送至PC端的过程。

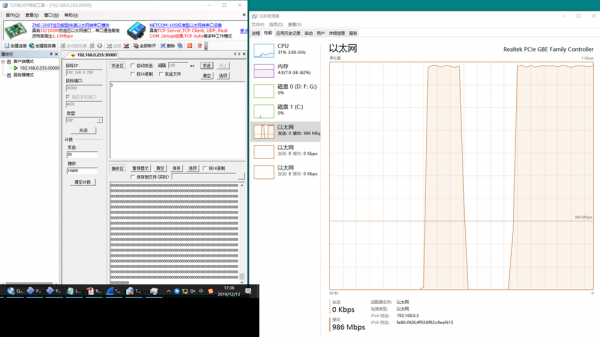

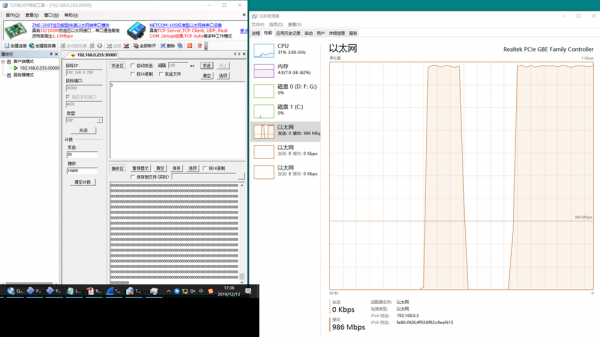

此时在TCP&UDP测试工具的发送区输入第一个字符为3的内容,并点击发送。在任务管理器界面可以看到接收速率达980 Mbps。同时可以在TCP&UDP测试工具软件的接收区看到连续的数字“8”接收进来,说明成功实现了FPGA向PC端以接近千兆的速率传输数据。

七、拓展实验:

注意事项1: 注意FPC转接板和千兆网卡模块下边缘对齐连接,如图30-1红圈内标注所示。

注意事项1: 注意FPC转接板和千兆网卡模块下边缘对齐连接,如图30-1红圈内标注所示。