锁相环实验_锁相环使用

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-07-02 | gingko | 初次建立 |

实验九:锁相环实验——锁相环IP核调用

一、 实验目的与意义

- 掌握锁相环IP核的使用方法。

- 掌握QuartusII的使用方法。

二、 实验设备及平台

三、 实验原理

- 锁相环全称是锁相环路,是一种反馈控制电路,其主要特点是利用外部输入的参考信号控制环路内部振荡信号核相位。锁相环通常由鉴相器、环路滤波器和压控震荡器三部分组成。

- FPGA内部锁相环的工作原理主要是通过调用内部IP核,改变IP核内部分频、倍频及相位差等参数,以此改变输入参考时钟的输出频率核相位,从而达到用户所需要的时钟信号驱动程序的运行。

四、 锁相环IP核调用步骤

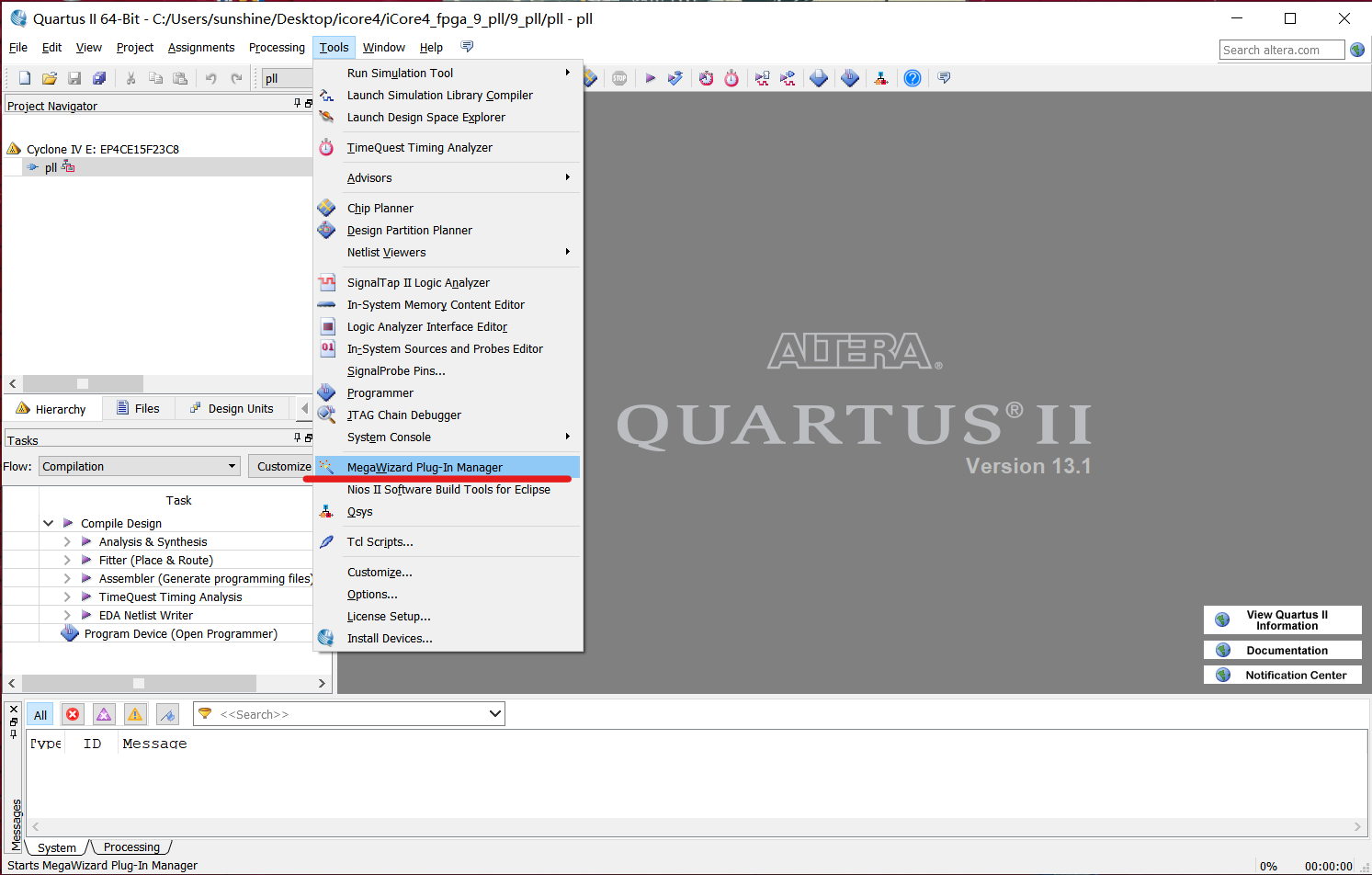

1、新建一个工程名为pll的工程,然后点击Tool →Megawizard Plug-In Manager,如图9-1所示。

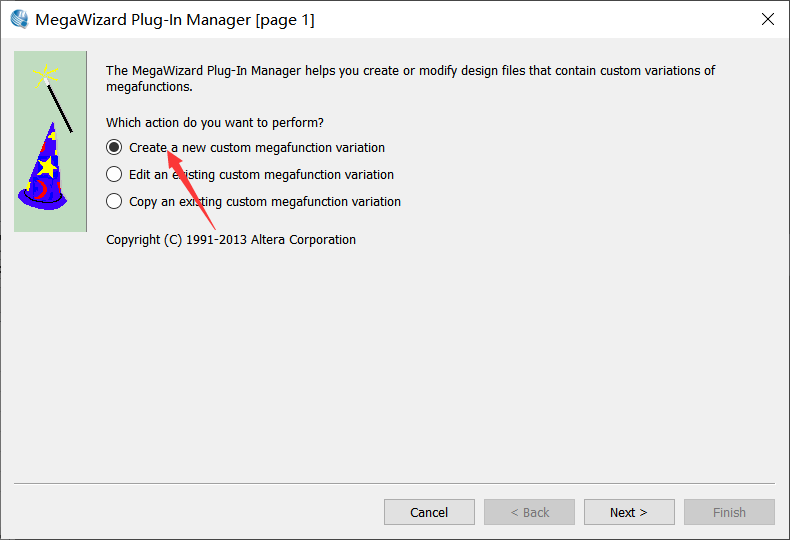

2、在该对话框选择新建IP核,如图9-2所示。

2、在该对话框选择新建IP核,如图9-2所示。

3、在此对话框选择新建IP核类型、生成的硬件描述语言、IP核文件的存储位置,如图9-3所示。

3、在此对话框选择新建IP核类型、生成的硬件描述语言、IP核文件的存储位置,如图9-3所示。

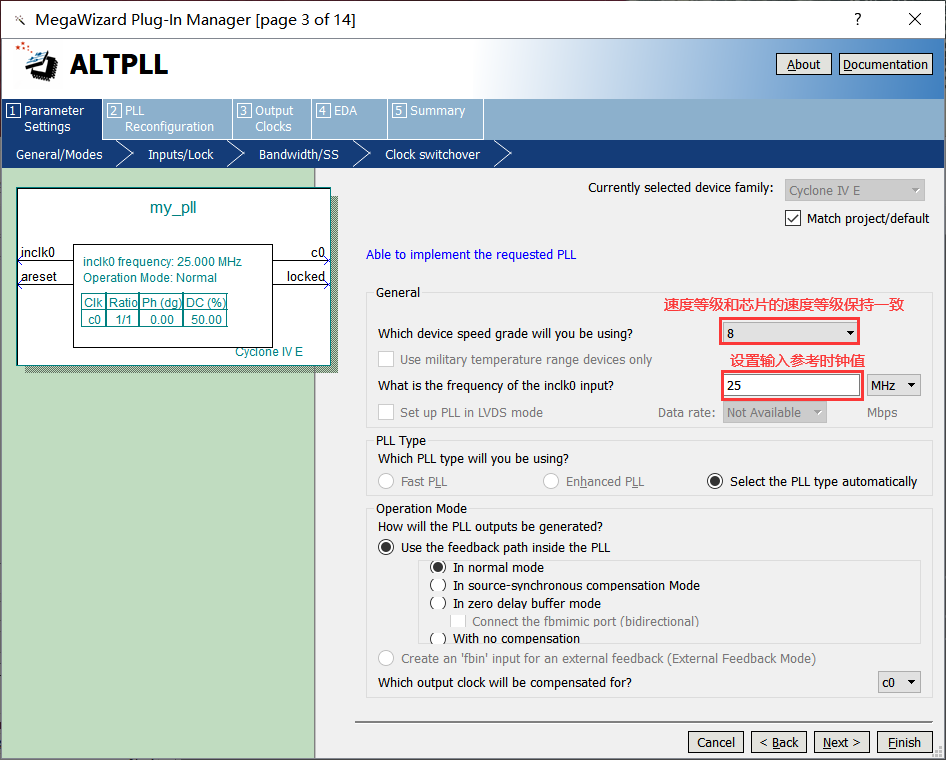

4、在此对话框中设置速度等级和输入时钟大小,设备芯片的速度等级是8,输入参考时钟是25MHz,如图9-4所示。

4、在此对话框中设置速度等级和输入时钟大小,设备芯片的速度等级是8,输入参考时钟是25MHz,如图9-4所示。

5、添加时钟复位信号和时钟锁,两个都是非必须信号,一般不需要添加,如图9-5示。

5、添加时钟复位信号和时钟锁,两个都是非必须信号,一般不需要添加,如图9-5示。

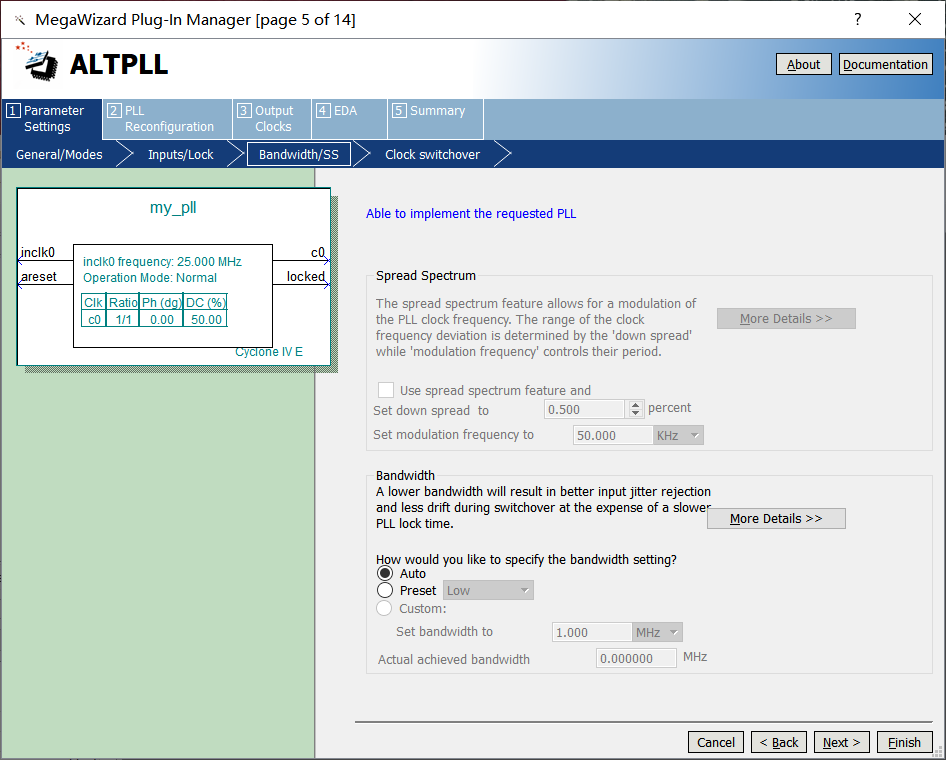

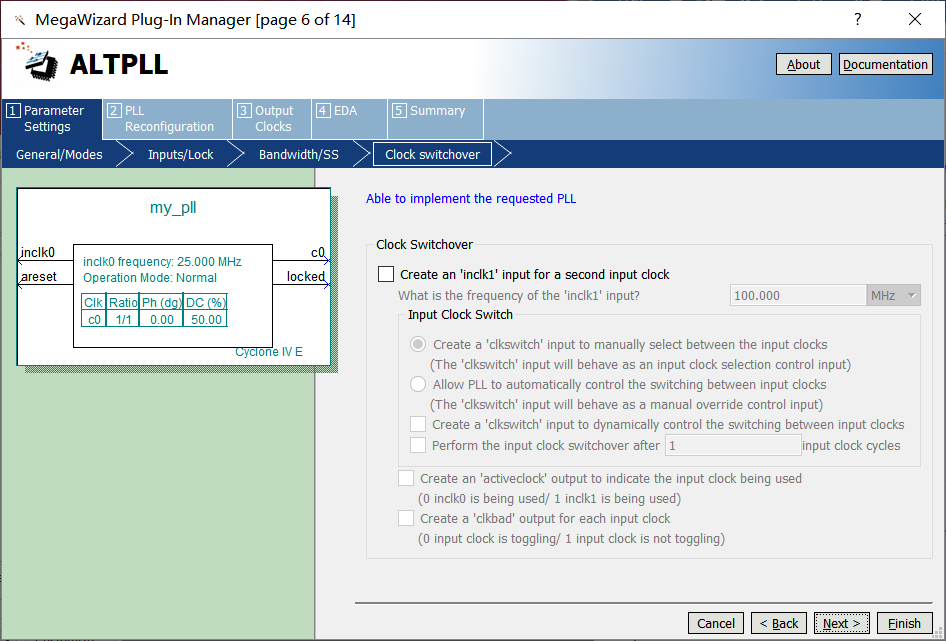

6、该对话框直接默认设置即可,如图9-6所示。

6、该对话框直接默认设置即可,如图9-6所示。

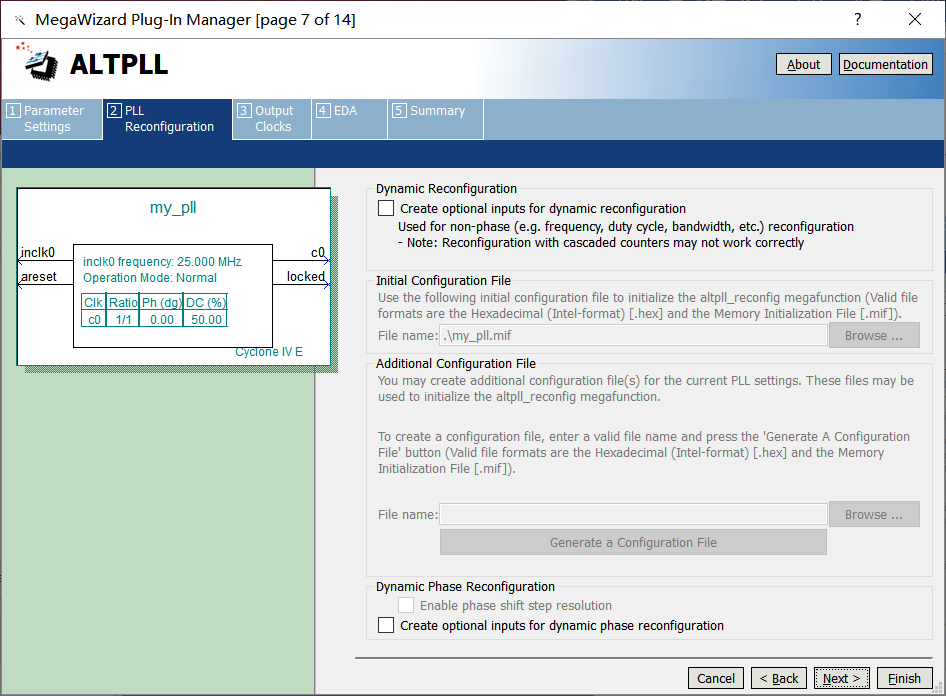

7、该对话框直接默认设置即可,如图9-7所示。

7、该对话框直接默认设置即可,如图9-7所示。

8、该对话框直接默认设置即可,如图9-8所示。

8、该对话框直接默认设置即可,如图9-8所示。

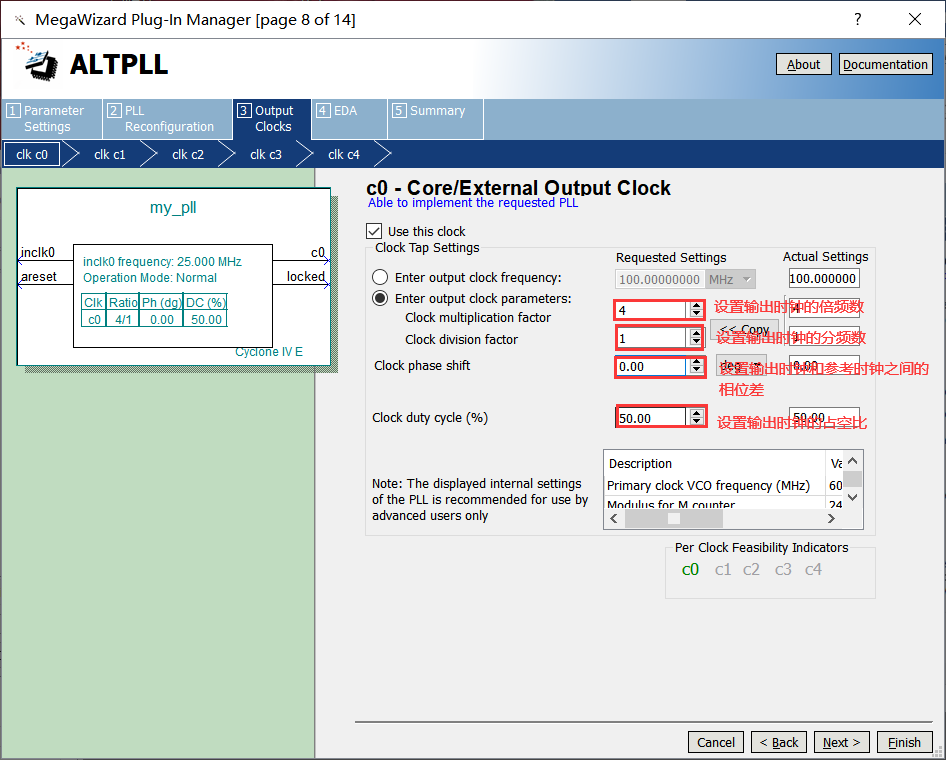

9、设置第一个输出时钟100MHz,由25MHz输入时钟进行4倍频得到的,输出时钟相位差为0,占空比为50%,设置参数如图9-9所示。

9、设置第一个输出时钟100MHz,由25MHz输入时钟进行4倍频得到的,输出时钟相位差为0,占空比为50%,设置参数如图9-9所示。

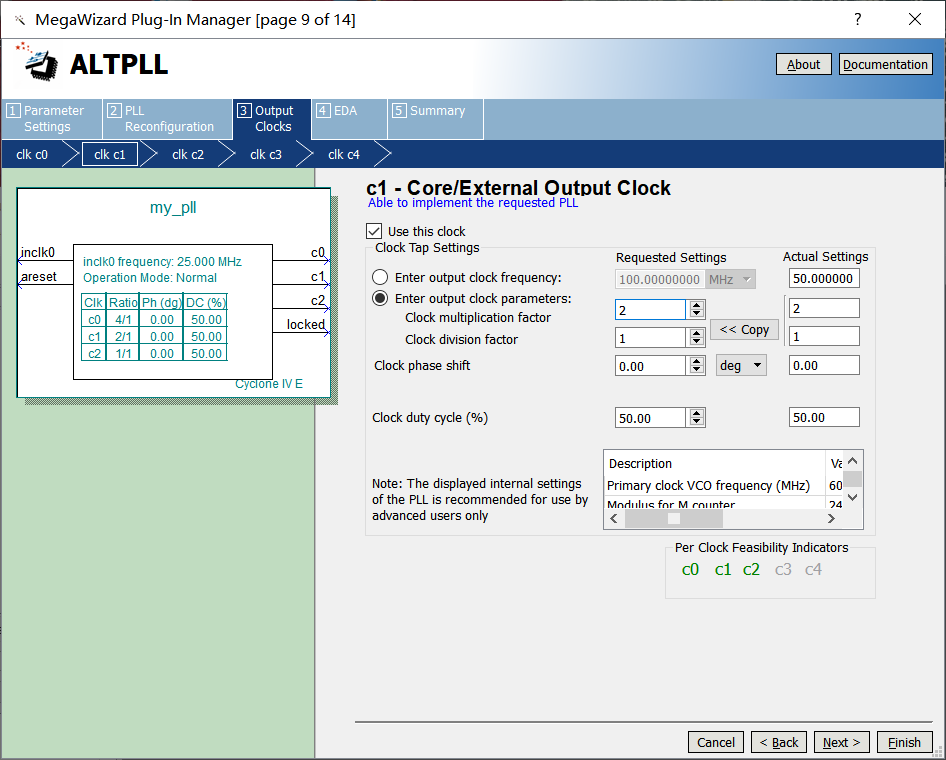

10、输出第二路时钟信号50MHz,设置参数如图9-10所示。

10、输出第二路时钟信号50MHz,设置参数如图9-10所示。

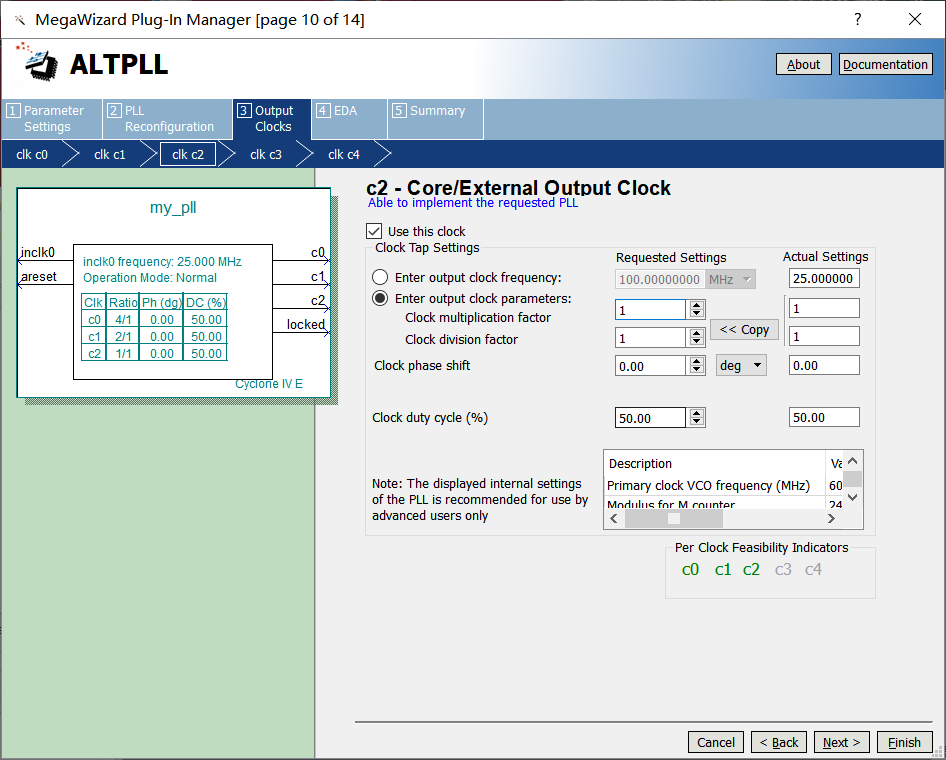

11、输出第三路时钟信号25MHz,设置参数如图9-11示。

11、输出第三路时钟信号25MHz,设置参数如图9-11示。

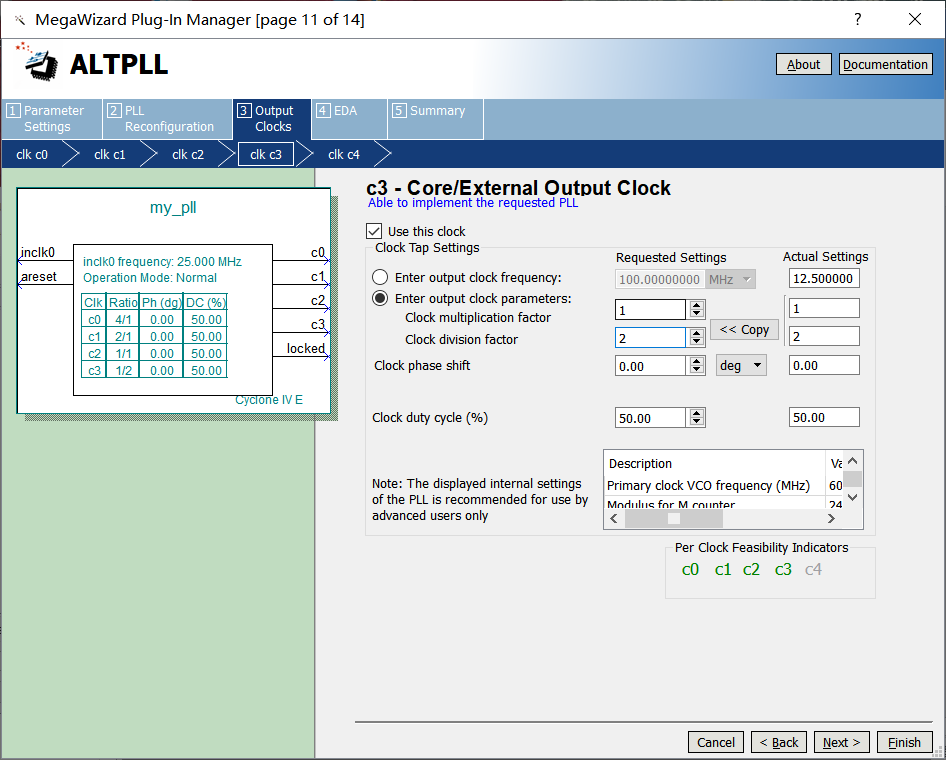

12、输出第四路时钟信号12.5MHz,设置参数如图9-12所示。

12、输出第四路时钟信号12.5MHz,设置参数如图9-12所示。

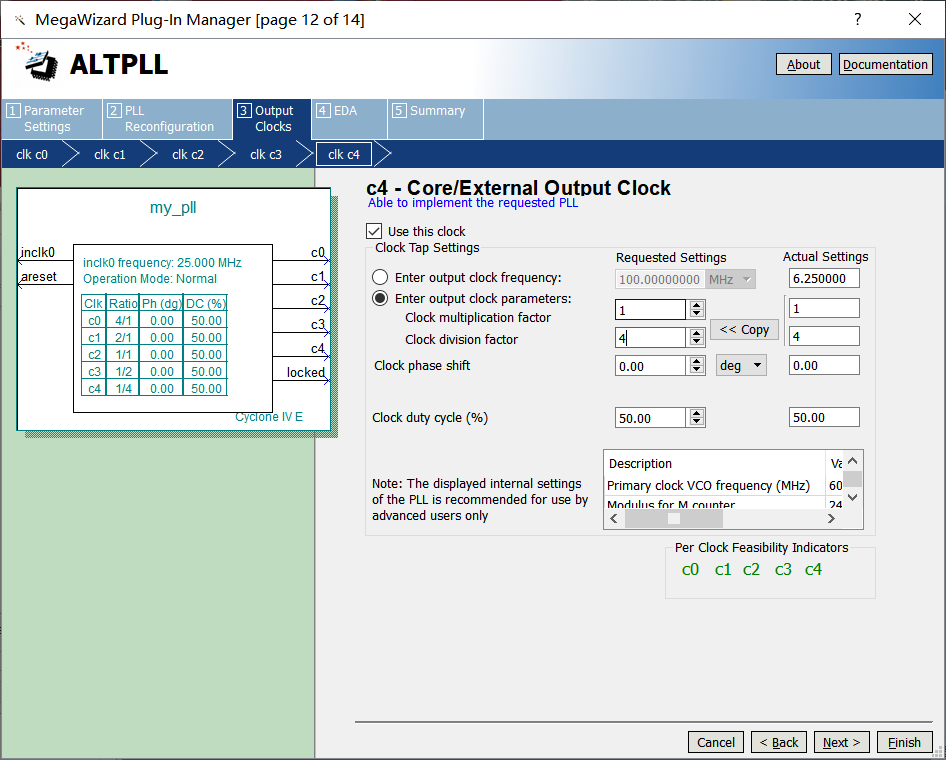

13、输出第五路时钟信号6.25MHz,设置参数如图9-13所示。

13、输出第五路时钟信号6.25MHz,设置参数如图9-13所示。

14、在该对话框一般默认设置即可,如图9-14所示。

14、在该对话框一般默认设置即可,如图9-14所示。

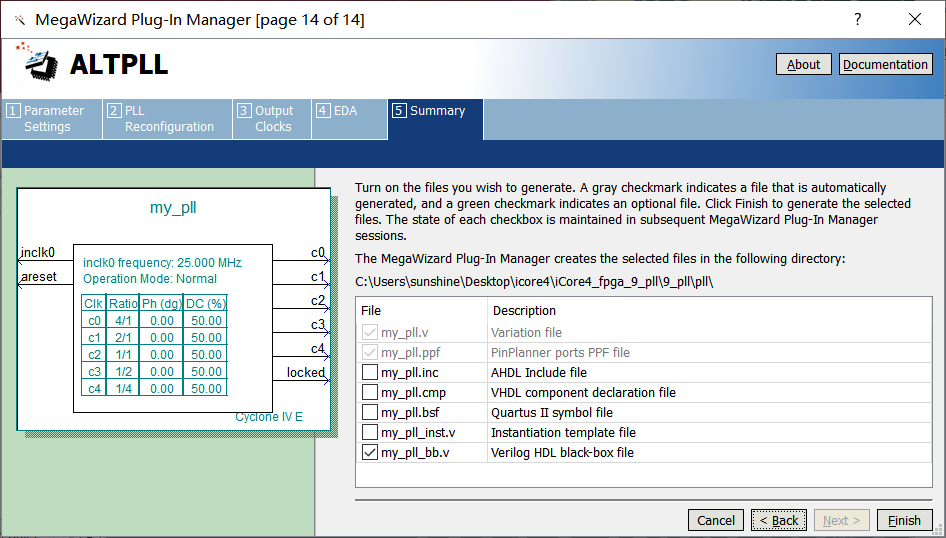

15、选择要生成的IP核文件信息,一般默认即可,如图9-15所示。

15、选择要生成的IP核文件信息,一般默认即可,如图9-15所示。

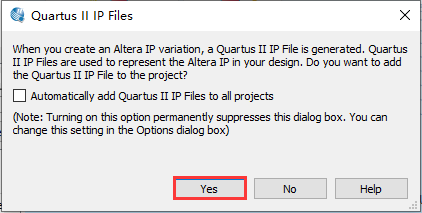

16、点击Finish后弹出该对话框,在此一定选择Yes,如图9-16所示。

16、点击Finish后弹出该对话框,在此一定选择Yes,如图9-16所示。

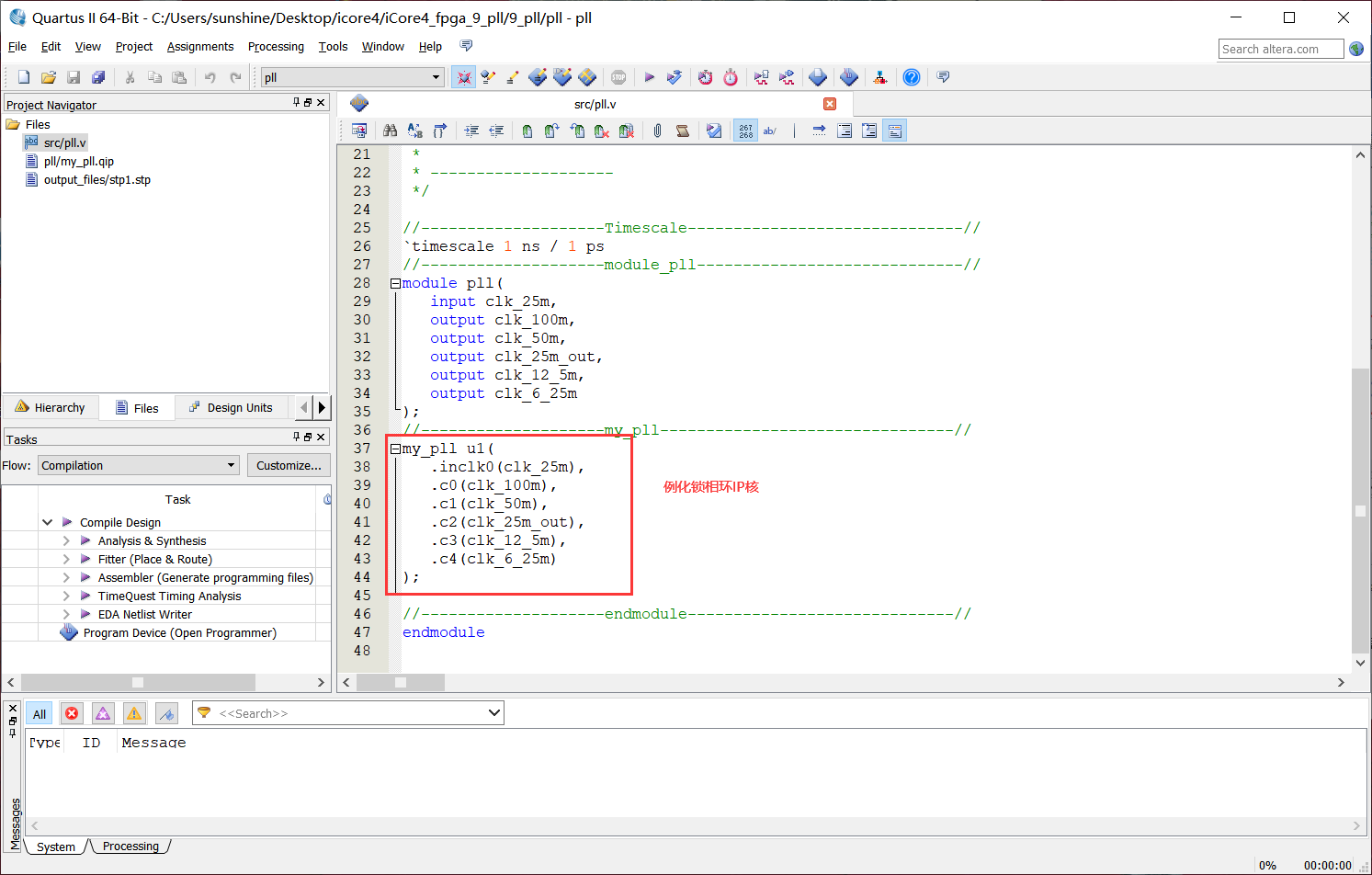

17、在工程中新建pll.v文件,并对锁相环IP核进行例化,如图9-17所示。

17、在工程中新建pll.v文件,并对锁相环IP核进行例化,如图9-17所示。

18、程序编写完成后进行编译即可,此时锁相环调用完成。

18、程序编写完成后进行编译即可,此时锁相环调用完成。

五、 实验步骤及实验结果

六、 拓展实验

- 思考下为什么6.25MHz输出时钟的相位与其他相位不一样;

- 更改相位核占空比,观察Signaltap采样结果有何不同。

锁相环实验_锁相环使用.txt · 最后更改: 2022/03/22 10:29 由 sean