这是本文档旧的修订版!

实验十:锁相环实验——锁相环使用

一、 实验目的与意义

- 了解什么是锁相环。

- 掌握锁相环的使用方法。

- 掌握 QuartusII 集成开发环境使用方法。

二、 实验设备及平台

- iCore3 双核心板。

- Blaster(或相同功能)仿真器。

- MicoUSB 线缆。

- QuartusII 开发平台。

- 装有 WINXP(及更高版本)系统的计算机。

三、 实验原理

- 通过 FPGA 的一个 I/O 口连接 LED;设定 I/O 为输出模式。内部计数器完成计数后改变 输出 LED 的状态(LED 闪烁),通过改变计数器的大小可以改变 LED 闪烁的频率。

四、 实验步骤

1、 建立工程,并新建 PLL.v 文件。打开 tool→megawizardplug-inmanager。

2、 直接点第一个新建 PLL,点击 next。

2、 直接点第一个新建 PLL,点击 next。

3、 在左侧的栏里 IO 文件夹下找到并选中 ALTPLL,在箭头 1 处选择 verilogHDL,再点 击方框中按钮。

3、 在左侧的栏里 IO 文件夹下找到并选中 ALTPLL,在箭头 1 处选择 verilogHDL,再点 击方框中按钮。

4、 输入文件名称,点击打开。

4、 输入文件名称,点击打开。

5、 保存好文件之后点击 next。

5、 保存好文件之后点击 next。

6、 方框 1 处选择速度等级,此 FPGA 的速度等级为 8,所以这里选 8,方框 2 处设置 输入时钟,开发板上的晶振是 25Mhz,这里写 25,点击 next。

6、 方框 1 处选择速度等级,此 FPGA 的速度等级为 8,所以这里选 8,方框 2 处设置 输入时钟,开发板上的晶振是 25Mhz,这里写 25,点击 next。

7、 方框 1 处是添加复位信号,方框 2 处是添加锁定信号,这个信号基本不需要,去掉 就可以了,点击 next。

7、 方框 1 处是添加复位信号,方框 2 处是添加锁定信号,这个信号基本不需要,去掉 就可以了,点击 next。

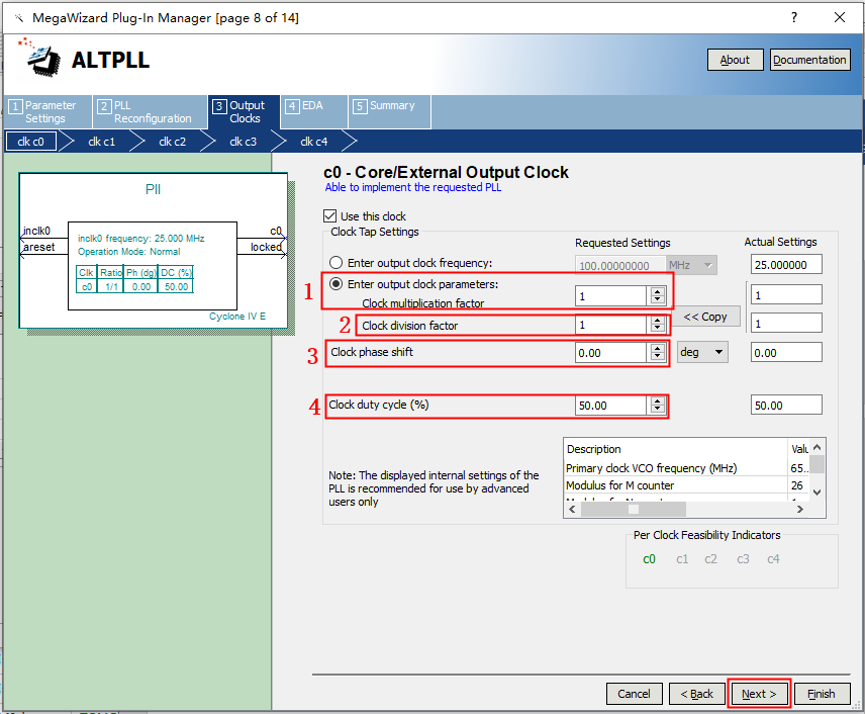

8、 接下来几项一直 next 就可以了,一直到Output Clock 设置界面。

8、 接下来几项一直 next 就可以了,一直到Output Clock 设置界面。

9、 方框 1 是倍频数,方框 2 是分频数,方框 3 是信号相位角偏移量,方框 4 是占空比, 根据需求分别设置就可以了,方框右边是实际输出,完成后点 next 即可。

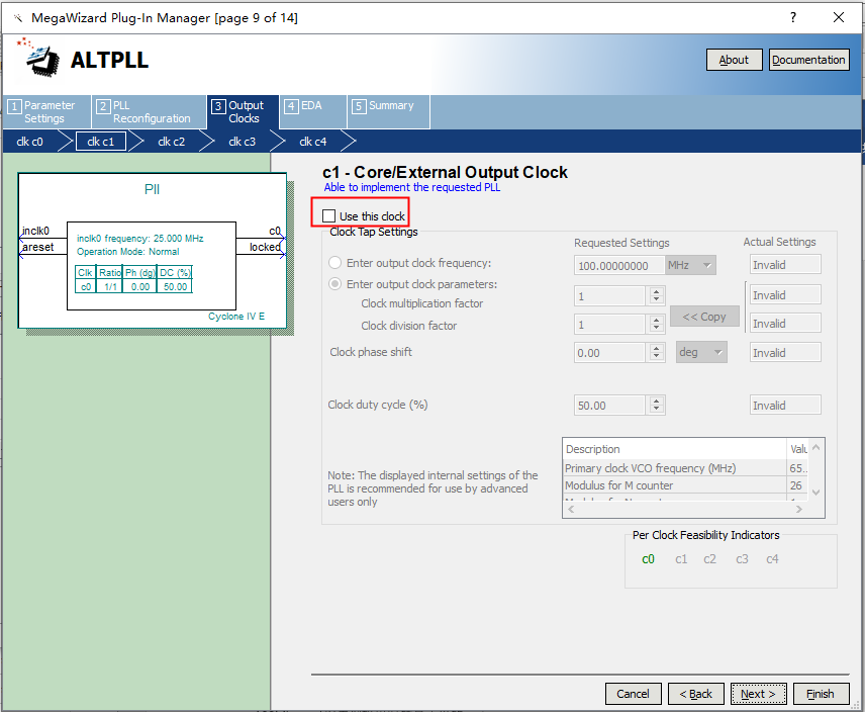

10、 接着是第二个时钟,1 个锁相环最多可以输出 5 个时钟,以后的时钟跟之前的设 置类似。唯一区别就是在箭头处勾选上,使能该时钟信号。

10、 接着是第二个时钟,1 个锁相环最多可以输出 5 个时钟,以后的时钟跟之前的设 置类似。唯一区别就是在箭头处勾选上,使能该时钟信号。

11、 此页不用设置,直接 next。

11、 此页不用设置,直接 next。

12、 这一页箭头指示是所有设置的信号信息,看看是否正确。没问题就 finish。

12、 这一页箭头指示是所有设置的信号信息,看看是否正确。没问题就 finish。

13、 接着把代码写进工程,分配引脚(使用接到排针的引脚,避免跟其他芯片引脚信 号冲突烧坏芯片),编译即可。

13、 接着把代码写进工程,分配引脚(使用接到排针的引脚,避免跟其他芯片引脚信 号冲突烧坏芯片),编译即可。

14、 打开逻辑分析仪将输出信号加入波形列表观察波形信号是否正确。

五、 实验现象

打开逻辑分析仪,加入输出波形信号查看波形,可以看到波形周期依次增大。采样时钟 为 100Mhz,可以看到输出时钟是正确的。