| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2019-02-25 | gingko | 初次建立 |

实验二:GPIO 输出实验——点亮三色 LED

一、 实验目的与意义

- 了解 FPGA 输出引脚功能。

- 了解三色 LED 特征和应用领域。

- 掌握 QuartusII 集成开发环境使用方法。

- 掌握 FPGA 引脚配置方法。

二、 实验设备及平台

三、 建立工程

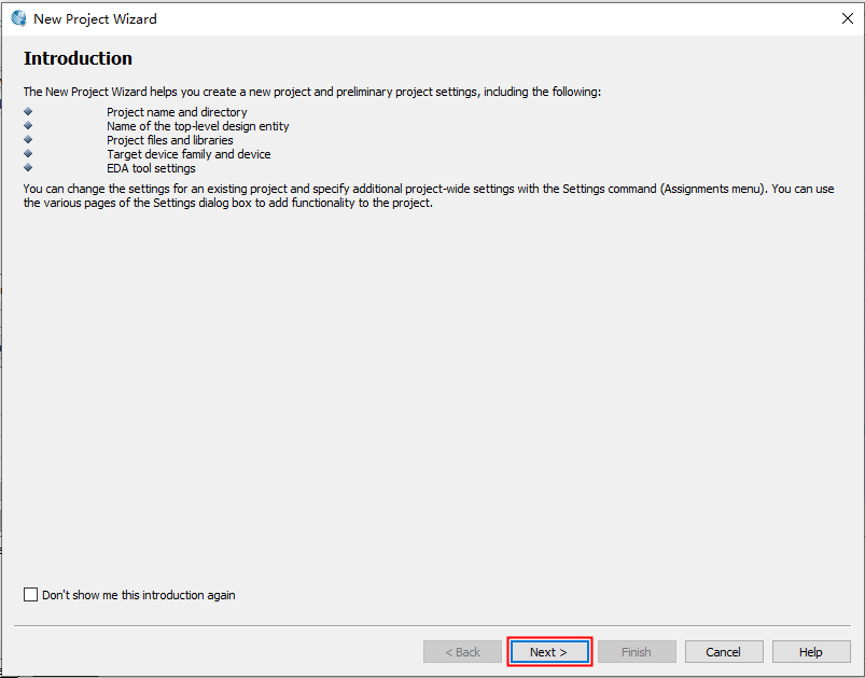

1. 打开 QuartusII 软件,点击 file→new project wizard,如图中箭头所示。

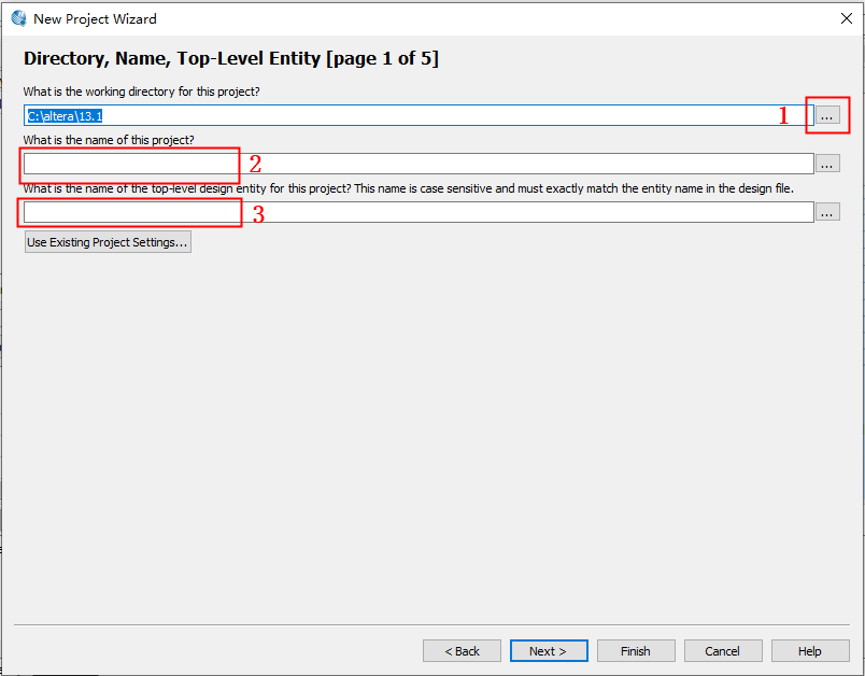

2. 点击“next”,在下一页的窗口方框 1 处选择工程存放路径,方框 2 处填写工程名 称,方框 3 处填写顶层文件名称(此处默认的是与工程名称相同,也可修改为需要的名称),这里命名为LED,完成之后点击“next”。

2. 点击“next”,在下一页的窗口方框 1 处选择工程存放路径,方框 2 处填写工程名 称,方框 3 处填写顶层文件名称(此处默认的是与工程名称相同,也可修改为需要的名称),这里命名为LED,完成之后点击“next”。

3. 此页是添加外部文件到工程中,可以在此处添加编写好的文件。本实验九先不添加文件,直接点击“next”选项。

3. 此页是添加外部文件到工程中,可以在此处添加编写好的文件。本实验九先不添加文件,直接点击“next”选项。

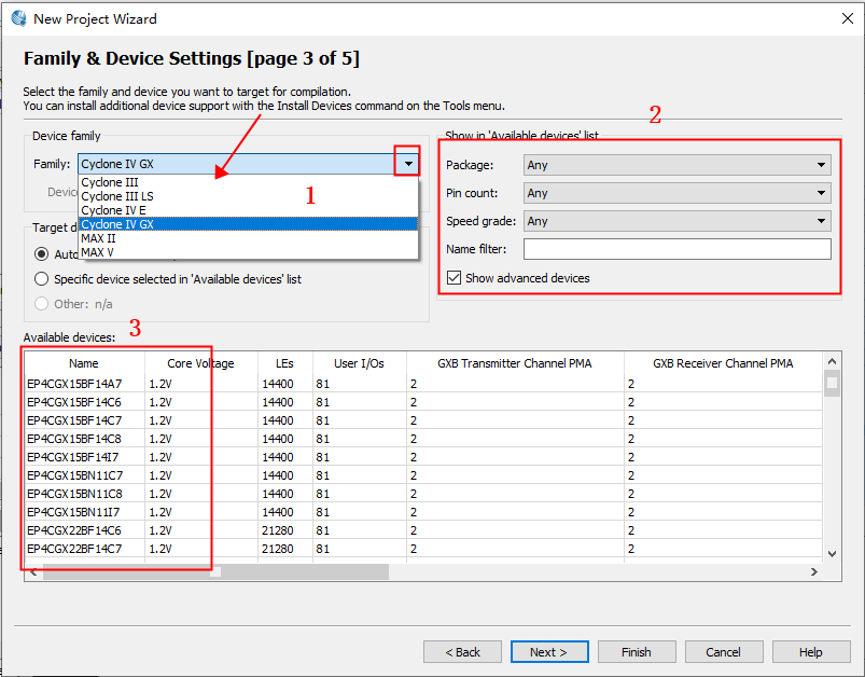

4. 这一页在 1 处选择(所需)器件的系列名称,右侧2处的方框里主要是为了筛选所需芯片型号方便快速查找。分别是选择器件封装、选择器件的引脚数量以及选择器件的速度等级,下边3处方框里的列表会根据你的选择筛选出符合条件的器件,然后找到和开发板对应的FPGA芯片型号。

4. 这一页在 1 处选择(所需)器件的系列名称,右侧2处的方框里主要是为了筛选所需芯片型号方便快速查找。分别是选择器件封装、选择器件的引脚数量以及选择器件的速度等级,下边3处方框里的列表会根据你的选择筛选出符合条件的器件,然后找到和开发板对应的FPGA芯片型号。

5. 本次我选择的是图示中的器件(iCore3双核心板FPGA型号为EP4CE10F17),列表中还列出了一些该器件的基本信息(内核电压, Les,用户可用引脚数等等)左键点击该型号(如图中箭头 1 所示),点击“next”。

5. 本次我选择的是图示中的器件(iCore3双核心板FPGA型号为EP4CE10F17),列表中还列出了一些该器件的基本信息(内核电压, Les,用户可用引脚数等等)左键点击该型号(如图中箭头 1 所示),点击“next”。

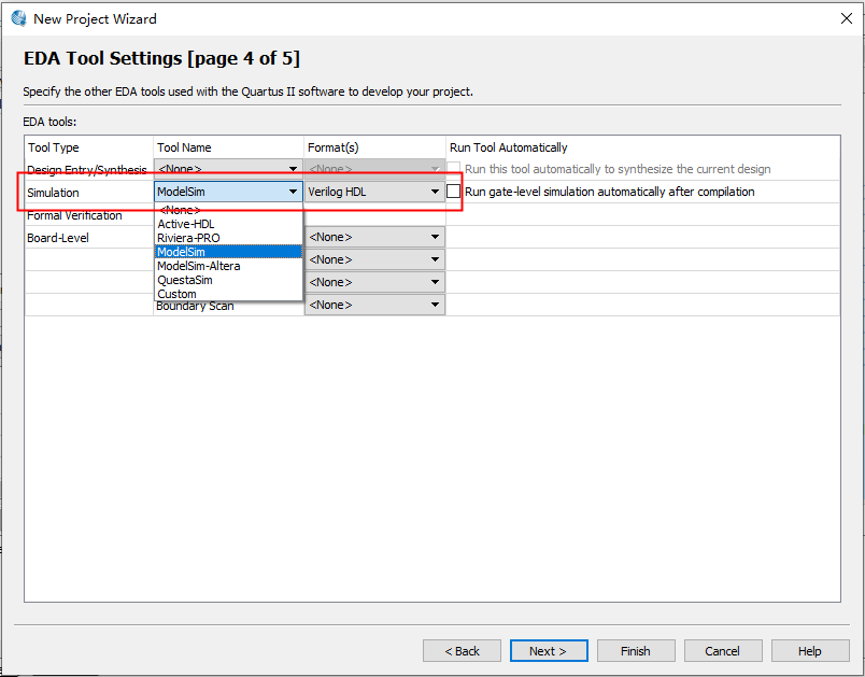

6. 这一页只用看方框处,选择仿真软件和仿真使用的语言(根据自己的实际情况选择), 如图所示,完成之后点“next”。

6. 这一页只用看方框处,选择仿真软件和仿真使用的语言(根据自己的实际情况选择), 如图所示,完成之后点“next”。

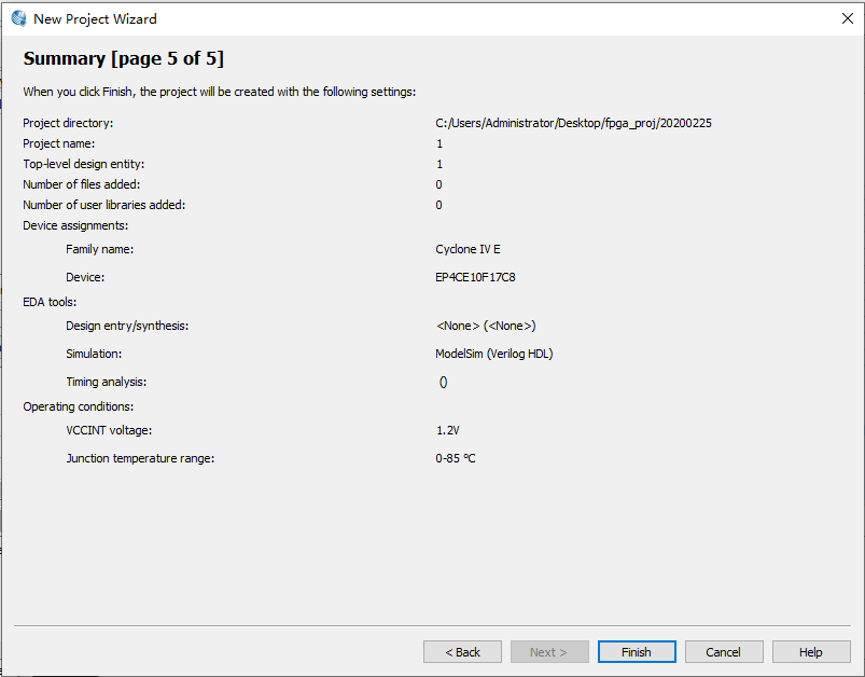

7. 这一页是显示前边操作的一些信息总汇,如果没问题,点“finish”,如果有问题,点击“back”重新操作。完成之后就出现工作界面了。

7. 这一页是显示前边操作的一些信息总汇,如果没问题,点“finish”,如果有问题,点击“back”重新操作。完成之后就出现工作界面了。

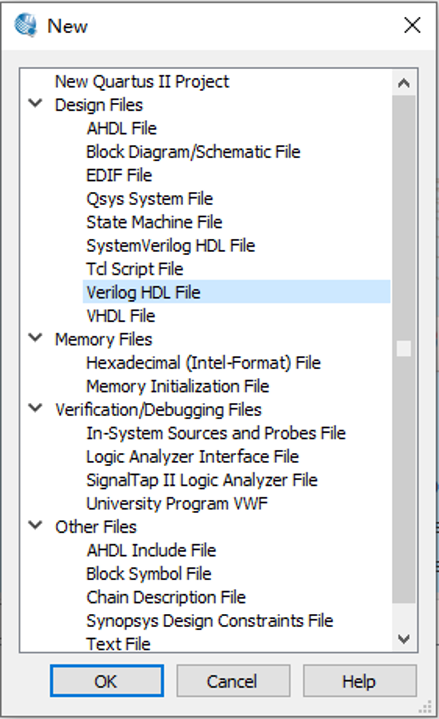

8. 这就是工作界面了,点击“file→new”或者直接点击图片方框中新建文件的图标,在弹出的窗口中选择需要建立的文件,我使用的是 Verilog 语言,所以这里我选择“Verilog HDL file”,也可选择其他类型文件(VHDL 语言选择 VHDL file,原理图文件选择“Block Diagram/Schematic File”等等),选择好所需文件,点击 OK 即可。

8. 这就是工作界面了,点击“file→new”或者直接点击图片方框中新建文件的图标,在弹出的窗口中选择需要建立的文件,我使用的是 Verilog 语言,所以这里我选择“Verilog HDL file”,也可选择其他类型文件(VHDL 语言选择 VHDL file,原理图文件选择“Block Diagram/Schematic File”等等),选择好所需文件,点击 OK 即可。

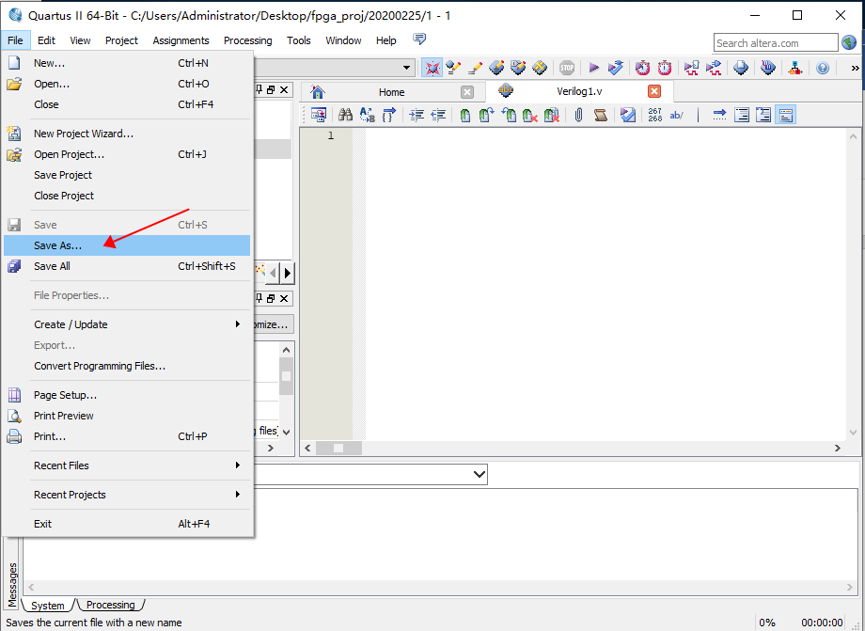

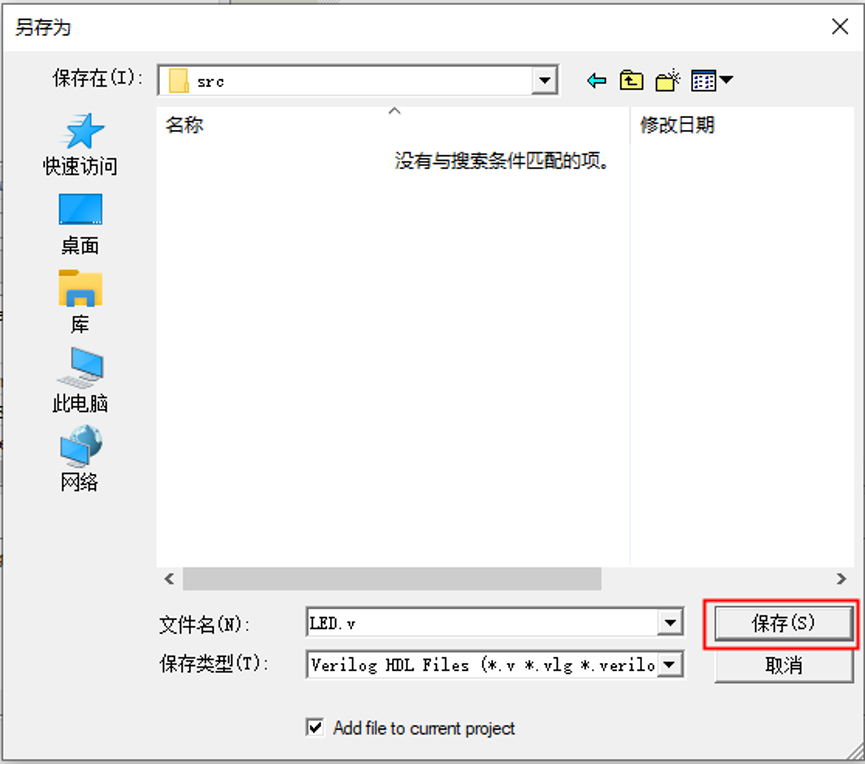

9. 一个新的文件就建立好了,此时文件是空的,点击 file→save as 保存文件(如图箭 头所指),在弹出的窗口中找到你新建工程的路径,选择源文件文件要存放的文件夹(已经提前新建好 “src”文件夹,这里直接选择此文件夹,大家可以自行建立),选择好保存地址后,在箭头处填写合适的文件名称,我这里命名为“led.v”,点击打开。在工作界面箭头处可以看见改好名称的文件。

10. 此时可以写代码了,写好以后点击方框处的全部保存。

10. 此时可以写代码了,写好以后点击方框处的全部保存。

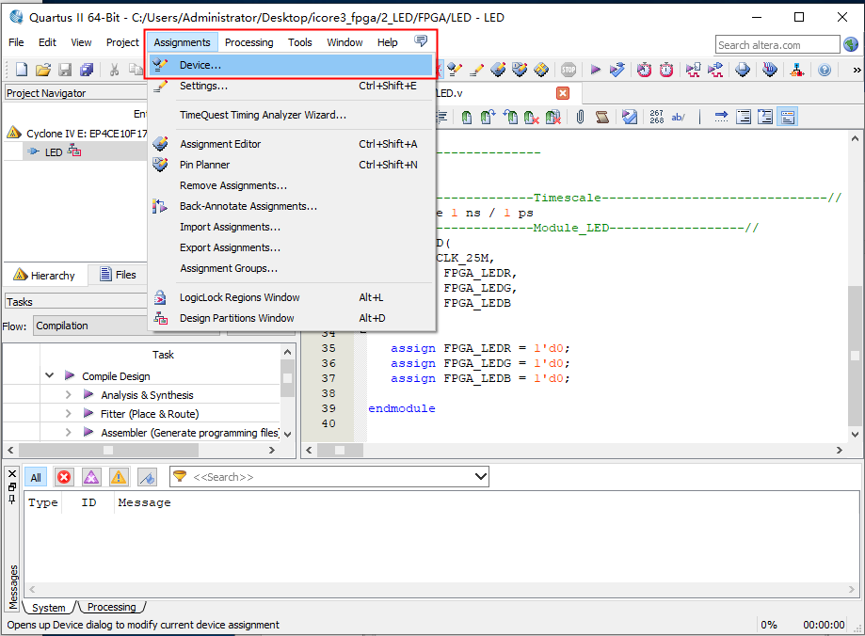

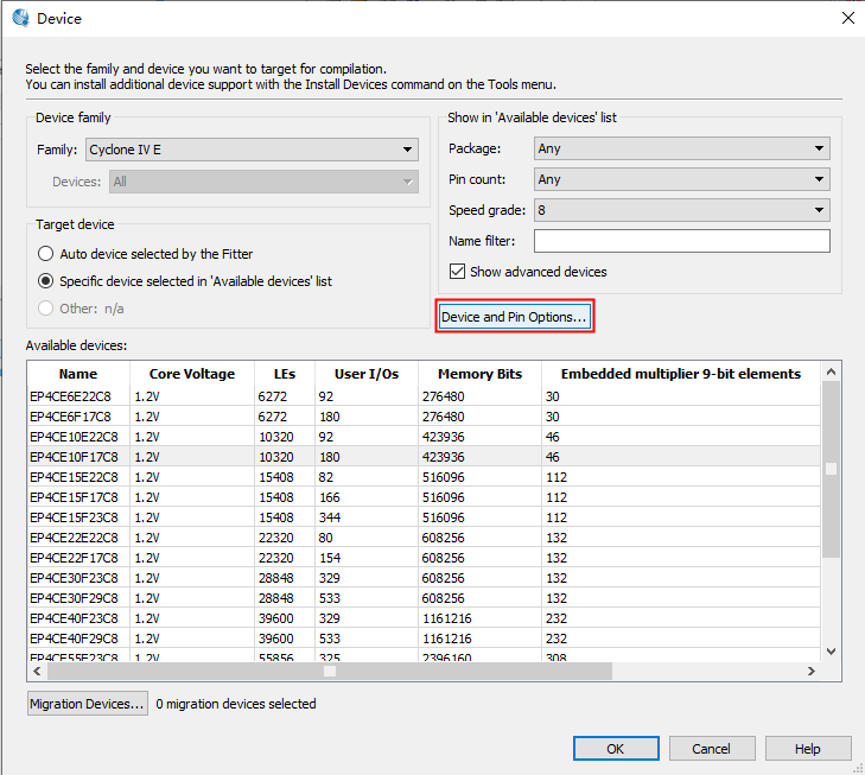

11. 点击 assignments→device,出现下边窗口,再点击方框处的 “device and pin options”, 在弹出的窗口左边栏中选择箭头 1 所示的 “unused pins”,在相应的右边栏红框处的 下拉菜单中选择 “as input ti-stated”,将未使用引脚配置为三态输入模式。

11. 点击 assignments→device,出现下边窗口,再点击方框处的 “device and pin options”, 在弹出的窗口左边栏中选择箭头 1 所示的 “unused pins”,在相应的右边栏红框处的 下拉菜单中选择 “as input ti-stated”,将未使用引脚配置为三态输入模式。

12. 然后在左边栏中选择“Dual-purpose pins”,在相应的右边栏中双击图示位置会出现下拉菜单,选择“use as regular I/O”。

12. 然后在左边栏中选择“Dual-purpose pins”,在相应的右边栏中双击图示位置会出现下拉菜单,选择“use as regular I/O”。

13. 这是选择好的界面,点击 OK 即可。

13. 这是选择好的界面,点击 OK 即可。

14. 点击图示中方框中的按钮进行编译。

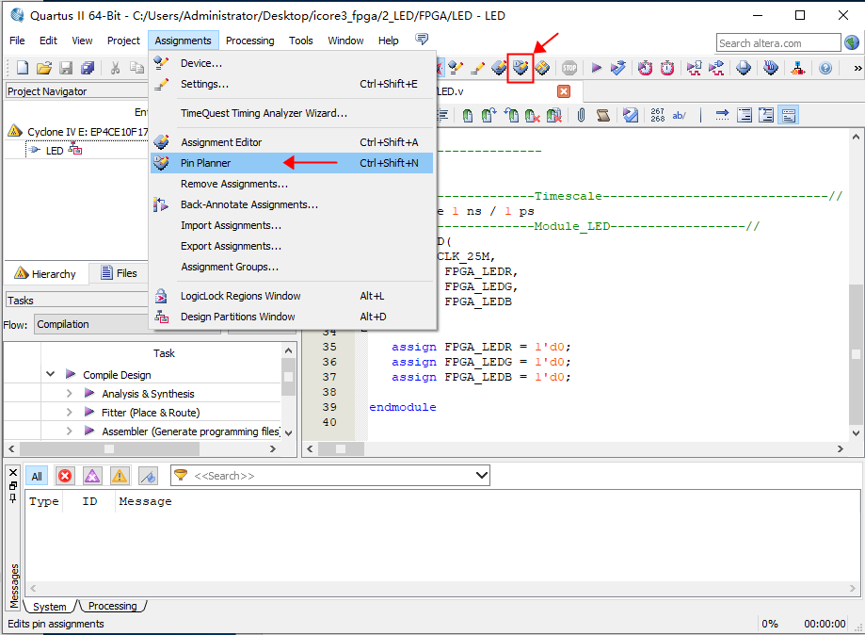

15. 点击 Assignments → pin planner 或者方框中的快捷按钮来进行引脚分配。

15. 点击 Assignments → pin planner 或者方框中的快捷按钮来进行引脚分配。

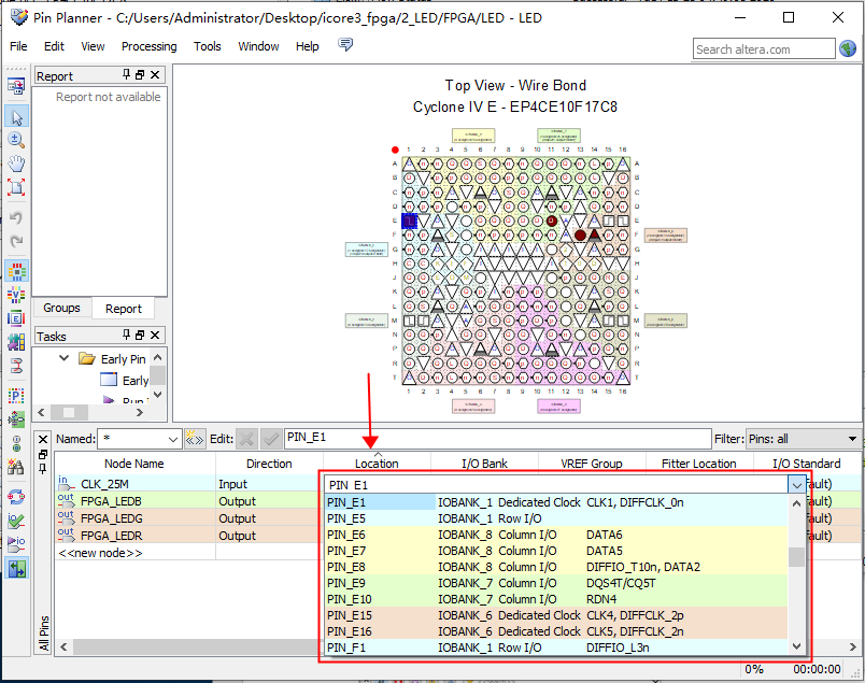

16. 在引脚分配窗口下方的列表中显示工程的输入输出引脚,双击 location 栏下(箭头 指示的位置)会出现下拉菜单,根据自己的硬件连接,选择正确的引脚,完成之后 关闭窗口即可

16. 在引脚分配窗口下方的列表中显示工程的输入输出引脚,双击 location 栏下(箭头 指示的位置)会出现下拉菜单,根据自己的硬件连接,选择正确的引脚,完成之后 关闭窗口即可

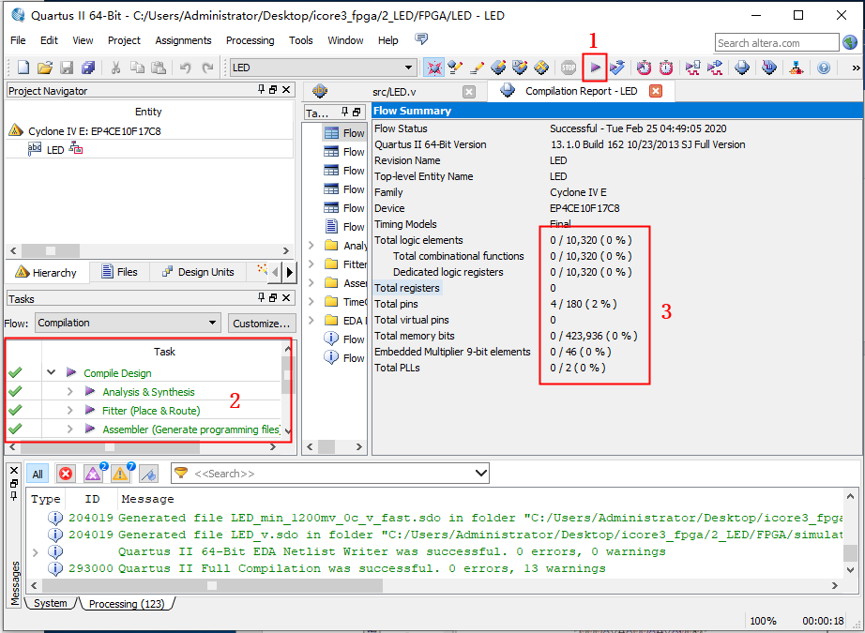

17. 接下来就是编译程序了,点击1处小方框中的图标开始编译工程(也可点击 processing→start compilation),这时候可以在下图左侧2处的方框处看到编译进度,图示是编译完成的状态,右侧方框处是生成的报告(工程占用的资源及引脚数等信息)。在图中最下方的绿色字符信息是编译提示,如果编译报错会有红色信息提示。双击红色提示信息,会定位到代码中编译错位的位置,可查看修改后再次编译,直到无报错。

17. 接下来就是编译程序了,点击1处小方框中的图标开始编译工程(也可点击 processing→start compilation),这时候可以在下图左侧2处的方框处看到编译进度,图示是编译完成的状态,右侧方框处是生成的报告(工程占用的资源及引脚数等信息)。在图中最下方的绿色字符信息是编译提示,如果编译报错会有红色信息提示。双击红色提示信息,会定位到代码中编译错位的位置,可查看修改后再次编译,直到无报错。

18. 根据前一章的教程烧写程序,观察实验现象。

四、 实验现象

iCore3 双核心板上与 FPGA 相连的三色 LED(PCB 上标示为 FPGA▪LED),红色、绿 色、蓝色)同时点亮(效果接近白光) 。