icore3l_fpga_15

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-12-07 | zgf | 初次建立 |

实验十五:3-8译码器实验——FPGA实现3-8译码器

一、 实验目的与意义

- 掌握3-8译码器的原理。

- 掌握状态机的使用方法。

二、 实验设备及平台

- iCore3L 双核心板。

- XiST USB-CABLE(或相同功能)仿真器及Micro USB线缆。

- 装有HqFpga开发软件的电脑一台。

三、 实验原理

- 译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另一个代码。译码是编码的反操作。根据输入和输出信号数量的关系译码器分为全译码器和部分译码器两类。

- 3-8译码器是一种常见的全译码器,输入是3位的二进制代码,共有8种组合,输出是与这8种组合对应的8个输出信号。这8个输出信号是只有1位高电平的8bit二进制信号。译码器将每种二进制的代码组合译成对应的一根输出线上的高、低电平信号。

- 根据3-8译码器的逻辑功能可知其逻辑真值表如表16-1所示。

- 表 15-1 3-8译码器逻辑真值表

| 输入 | 输出 | |||||||||

| a2 | a1 | a0 | y7 | y6 | y5 | y4 | y3 | y2 | y1 | y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

四、 代码讲解

- 本实验首先通过内部程序自身产生输入信号a,并设置一个20us的定时器根据编码器的工作原理依次切换输入信号的值;然后通过状态机根据逻辑真值表将输入信号译码成对应的输出信号,改变8根输出线上的高低电平。其代码如下:

//----------------------------------------------------------// //利用状态机实现3-8译码器的输出信号,输出译码信号与真值表一致 reg [7:00] y_r; always@(posedge fpga_clk or negedge rst_n) if(!rst_n) y_r <= 8'b0000_0000; else case(a) 3'b000:begin y_r <= 8'b0000_0001; end 3'b001:begin y_r <= 8'b0000_0010; end 3'b010:begin y_r <= 8'b0000_0100; end 3'b011:begin y_r <= 8'b0000_1000; end 3'b100:begin y_r <= 8'b0001_0000; end 3'b101:begin y_r <= 8'b0010_0000; end 3'b110:begin y_r <= 8'b0100_0000; end 3'b111:begin y_r <= 8'b1000_0000; end default:begin y_r <= 8'b0000_0000; end endcase

五、 实验步骤及实验结果

1.打开HqFpga软件,点击左侧栏“新建工程”按钮,弹出的“设置(S)”界面中设置工程参数如图所示,然后点击“下一步”。

2.弹出窗口直接点击“完成”按钮。

2.弹出窗口直接点击“完成”按钮。

3.点击左侧栏的“设计管理”按钮,弹出界面中点击“新建文件”按钮。

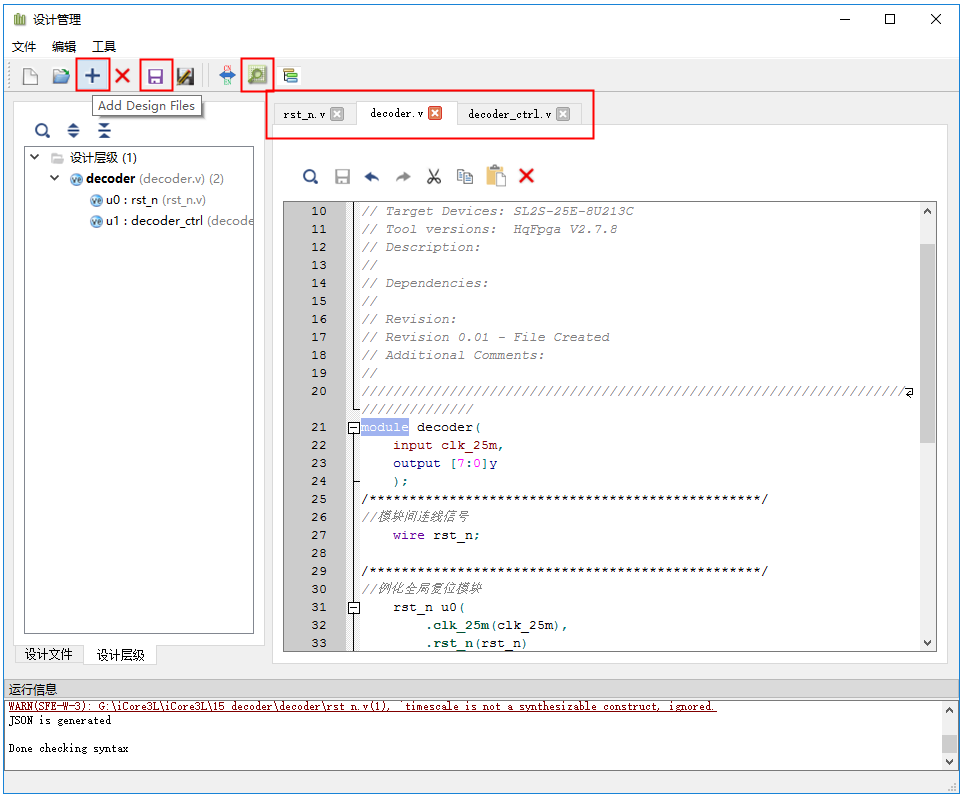

4.在编辑区输入代码并点击保存,将文件分别命名为rst_n.v(产生复位信号)、decoder_ctrl.v(产生3-8译码器功能)和decoder.v(顶层模块,调用rst_n模块和decoder_ctrl模块)。然后点击语法检查,如果无报错,点击“Add Design Files”按钮(就是那个“+”号),将保存的三个文件选中,添加到工程中,并退出此界面。

5.然后点击主界面的“RTL综合”按钮,如果无报错,点击左侧栏的“全部运行”按钮,生成下载文件。

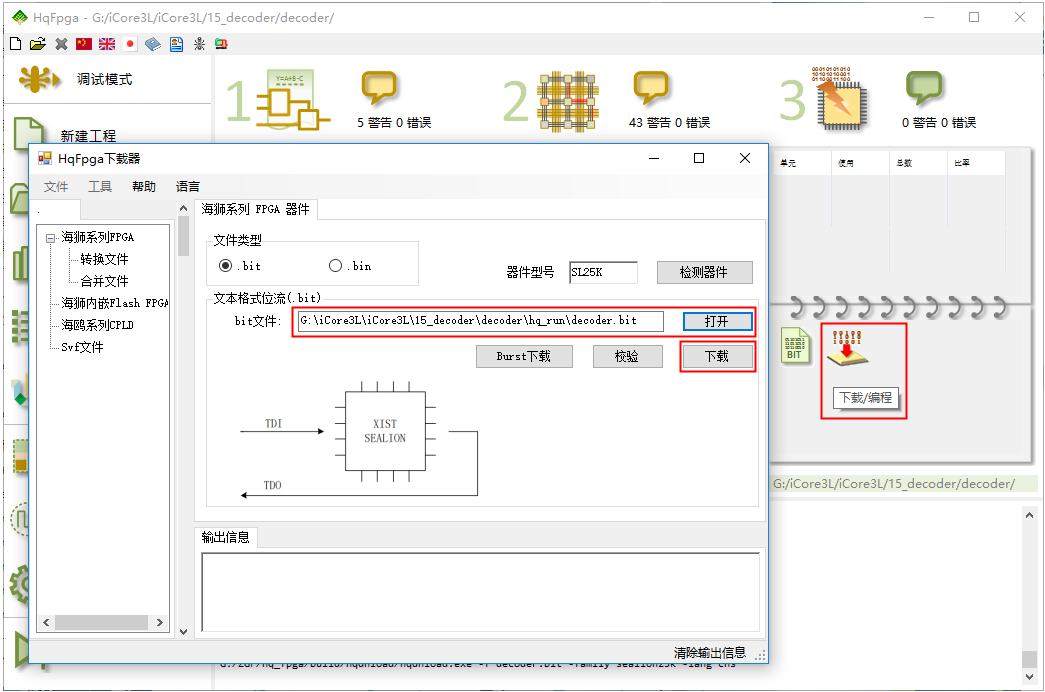

6.将下载器和iCore3L双核心板连接,给核心板供电,然后点击主界面的“下载/编程”按钮,将生成的bit文件下载到FPGA中。

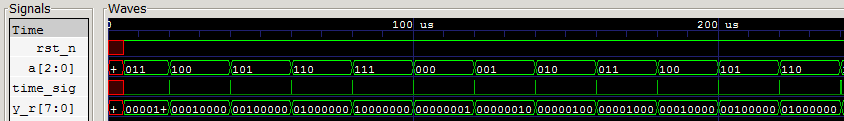

7.因为输出并未与外部设备关联,因此可以通过“调试模式”的波形查看代码运行的结果。通过对如下波形结果分析,可以发现,其输入变量a的值和输出变量y_r的值符合3-8译码器的运算结果,说明基于FPGA实现的3-8译码器功能正常运行。

六、 拓展实验

1、 设计一个部分译码器(如:4-10译码器),观察信号变化。

icore3l_fpga_15.txt · 最后更改: 2022/03/19 15:28 由 sean