icore3l_fpga_4

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-11-07 | zgf | 初次建立 |

实验四:HQINSIGHT实验——调试工具的使用

一、 实验目的

- 学习HqFpga软件“调试模式”的使用。

- 学习如何对FPGA工程进行实时调试。

二、 实验设备及平台

- iCore3L双核心板。

- XiST USB Cable下载器。

- 安装有HqFpga 2.8.5版本开发环境的电脑。

三、 调试(HqInsight)

- HqFpga集成了FPGA片上实时调试的支持,工具名称为HqInsight,它可以作为单独的工具使用;而本实验主要讲解在HqFPGA中集成的HqInsight的功能,以及在HqFPGA集成开发环境中使用HqInsight进行逻辑分析的具体步骤。

- HqInst是在正常的FPGA实现流程中添加了Instrumentor(调试信息插入)以及Debugger(实时调试)的步骤。

- Instrumentor为信号采集器,其功能包括下面几条:

- RTL 源代码解析: 解析源代码,生成内部格式文件,供信号标识使用。

- 源代码层次结构标识:以树形结构按层次列出所有代码模块及内部可调试块,便用户找到需要调试的信号。

- 调试信号标识: 以高亮及不同颜色在 RTL 源代码中标识可调试信号,并对用户选择的需要调试的信号进行标识。

- 信号采集, 收集用户选择的可调试信号,生成内部文件,以提供给实时调试器使用。

- 源代码显示:根据模块层次选择需要的任意 RTL 源代码进行显示

- 根据调试信号采集器采集到的信号信息生成专用调试电路 IP。

- 生成带有专用调试电路 IP 的 RTL 源代码。

- Debugger 为实时调试器, 其主要功能包括:

- 设置触发条件。

- 设置触发位置。

- 进行实时调试,并从波形输出器中得到输出波形,观察调试结果。

- 波形输出器: 以标准 VCD 格式输出波形,用户可以用任意支持 VCD 格式的第三方工具查看输出波形。

四、 操作步骤

1、使用HqInsight调试流程

- 打开调试信息采集器Instrumentor对需要进行调试的所有RTL源代码进行分析转换;

- 打开对应模块的各个源代码,选择所有需要进行调试的信号,设置调试方式,如 Sample Clock, Trigger, Sample 或者 Trigger and Sample;

- 根据用户设置的调试信号生成调试所需的 IP 核;

- 实现(Implement) 加入IP的新设计:RTL综合,布局/布线,生成bitstream 并下载至 FPGA 中;

- 使用实时调试器(Debugger)设定触发条件;

- 一旦触发条件激活,实时调试器通过 JTAG 线缆服务器(JTAG cable server)获取捕获的信号并重整波形,输出 VCD 格式的波形文件;

- 用户可用第三方的软件观察波形或者检查调试信息,从而追踪问题;

- 重复步骤4至7或者1至7,完成调试任务。

2、使用HqInsight Instrumentor采集调试信息

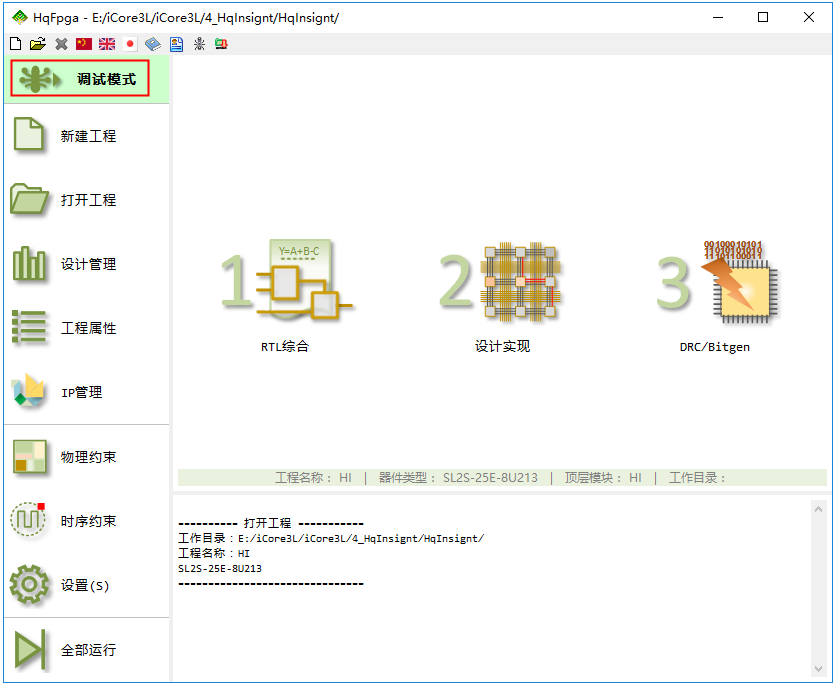

- 1. 打开本例程下的工程(也可以新建工程和源文件,并按照本例程的源文件输入工程代码,或者建立工程时直接添加本例程下的源文件),然后点击左侧栏的“调试模式”按钮,进入调试模式。

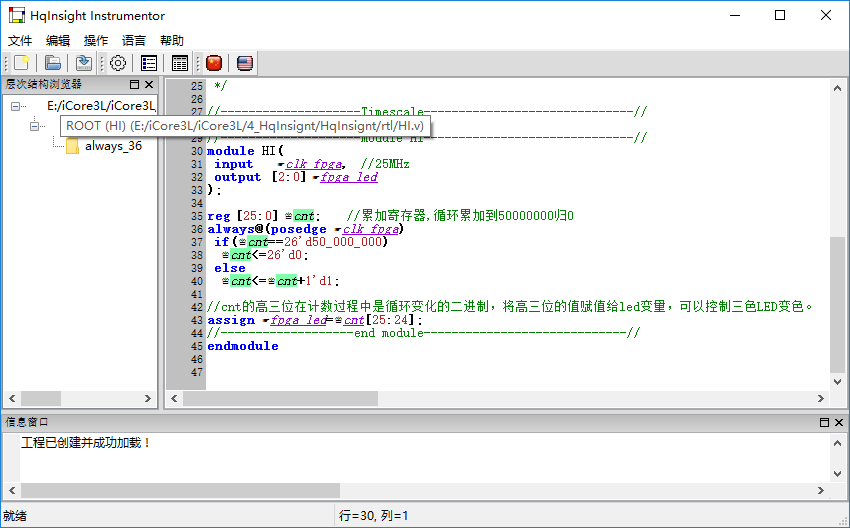

- 2、可以看到已经激活“采集调试信息”选项;单击此选项,出现如下窗口,可以看到在窗口的左侧“模块层次结构”窗口中,会显示工程下所有的模块以及工程的层次结构。

- 在模块层次结构中,会显示所有模块的调用信息,每一个模块所包含的下层模块,模块所对应的文件及相应路径。

- 3、窗口右边是调试信息显示,可以看到,不同颜色代表了不同的元素:关键字、注释及数字等,并对信号等可调试信息采取了特殊显示;对于每一个可调试信号,除了颜色,在该信号的左侧会出现一个指向该信号的小手,表示此信号是可以加入到调试中的,且用户可以在此信号出现的任何位置对该信号进行调试设置。

- 4、调试信号设置:

- 在可调试信号上单击鼠标,弹出菜单里可以选择将信号设置为何种方式:Trigger Only(仅触发)/Sample Only(仅采样)/sample Clock(采样时钟)/sample and Trigger(采样且触发)。在对信号进行设置后,信号左侧的标识会相应的发生改变,信号颜色也会发生变化。

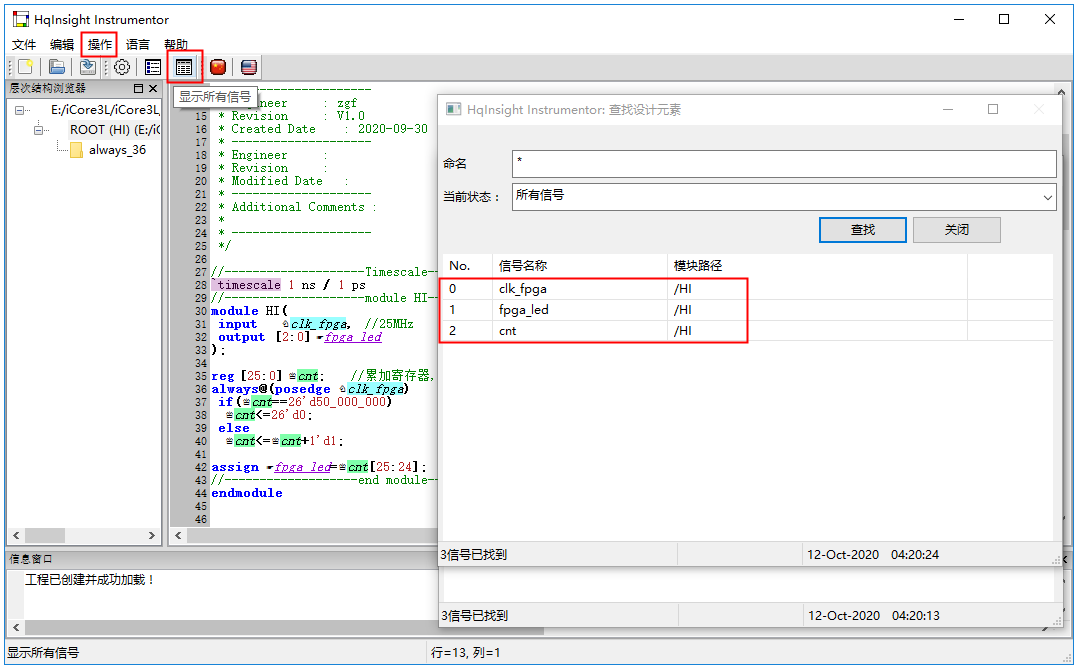

- 5、设置完所有需要调试的信号后,通过单击菜单栏“操作”按钮,在下拉菜单中选中“显示所有信号…”,或者直接单击“显示所有信号”快捷按钮都会弹出查找设计元素窗口;此窗口内可以看到设置好的信号列表,并提供相应的快速查询能力。此窗口内还可以对信号的状态做相应的修改,修改后,该信号在各个模块源代码中的显示标记也会相应改变。

- 6、点击菜单栏的“HqInsight虚拟逻辑分析仪(ILVA)配置”按钮,如图4-8红框中所示齿轮状图标,弹出窗口中可以设置采样深度,这里采样深度设置为8192。

7、用户在选择好各种信号后, 需要点击”保存工程”菜单项或者相应按钮, 对工程进行保存。 实际上, 只要用户对工程做了任何改变,都需要保存工程, 这样 HqInsight 才能根据用户的设置生成调试需要的 IP 核及中间配置文件。

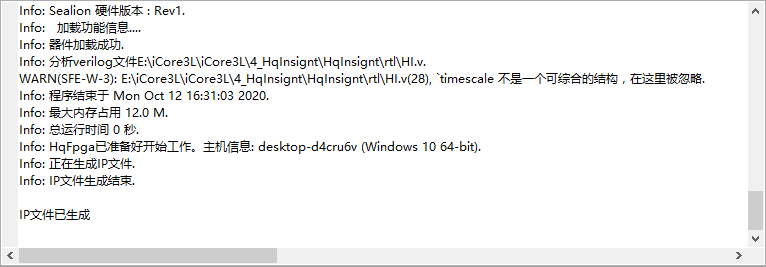

- 8、保存工程后,HqInsight 会对用户的设计源代码进行重新分析,加入对应的调试信息,生成调试需要的 IP 核及中间文件的等,各种输出信息会显示在信息输出窗口中。

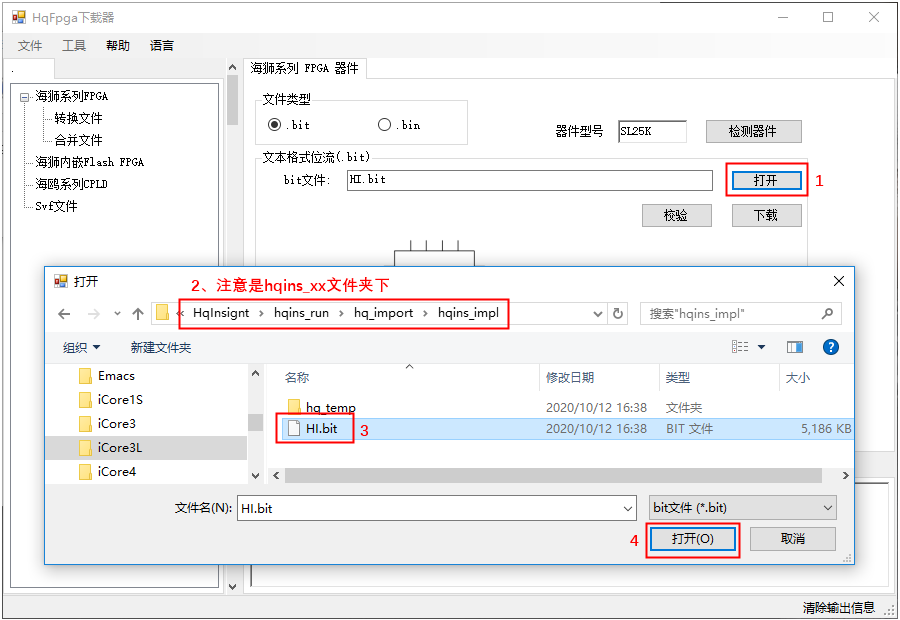

- 9、接下来关掉HqInsight Instrumentor窗口,可以看到主界面上“实现→下载”按钮激活,单击此按钮,弹出“HqFPGA下载器”界面,这里有个地方是需要注意的,这里下载的是加入调试IP核的bit文件,所以确切来说,是在hqins_文件夹下的bit文件。

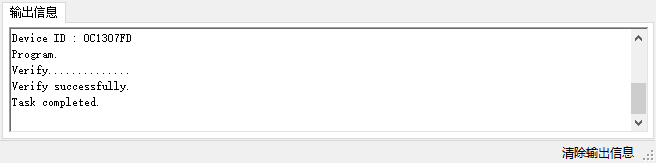

- 10、将下载器连接到双核心板,给板子供电,下载bit文件。可以观察到板子上的三色LED色彩周期变化,“HqFPGA下载器”界面的输出信息栏会输出如下提示信息。

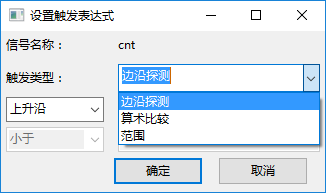

- 11、下载完成后,关闭下载界面,点击主界面的“实时调试”按钮,弹出HqInsight Debugger界面,在进行实时调试前,需要对触发信号进行设置;单击需要设置的触发信号,下拉列表中单击“设置触发条件…”,进行“设置触发表达式”参数进行设置。

- 12、“设置触发表达式”弹窗如下,可以对寄存器变量的触发类型等信息进行设置。这里选择观察cnt=0的时刻,可以设置触发类型为“算术比较”、“等于”和“26’b0”。

- 13、在调试过程中, 采样缓存在不断采样设计信号,因为,触发事件的发生和终止采样的时间这两者的关系是可以由用户控制的, 即设置触发位置。可以通过菜单项设置触发位置, 选项包括早期、中期和晚期。具体触发位置由用户根据设计的实际情况决定。通过点击工具栏的“调试”按钮,设置触发位置。

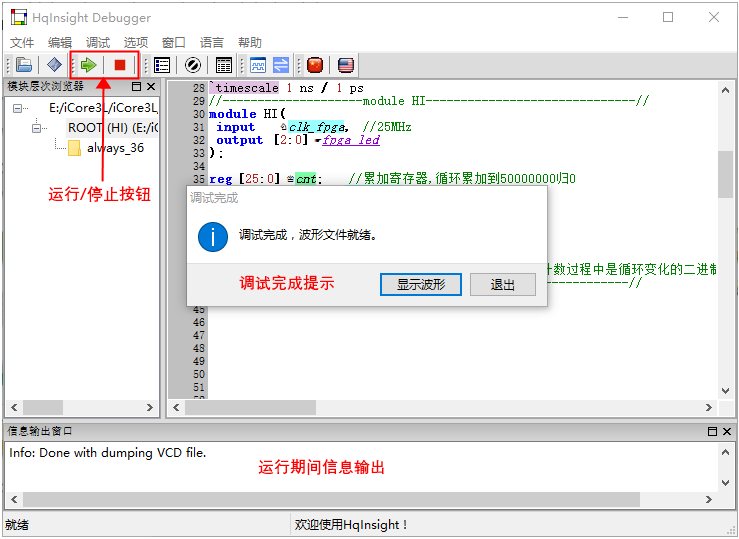

3、启动运行

- 在设置好需要的配置后,点击菜单项或者按钮可以开始运行实时调试,在调试之前,要确保正确的bitstream已经下载到FPGA中,另外JTAG线缆已经正确的连接到FPGA测试板上。

- 点击“运行”菜单或者按钮,启动调试。

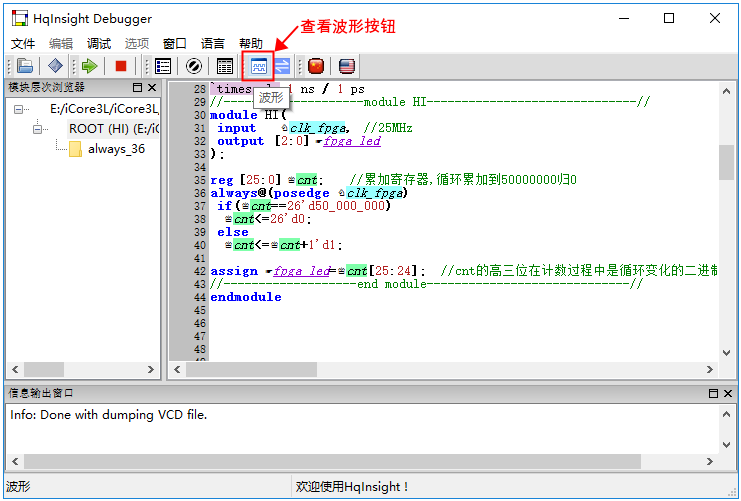

- 启动运行后,实时调试会自动开始, 每一步的调试信息会显示在信息输出窗口,Done为1表示数据采样正常完成;运行完毕,会提示调试完成,波形文件准备就绪。

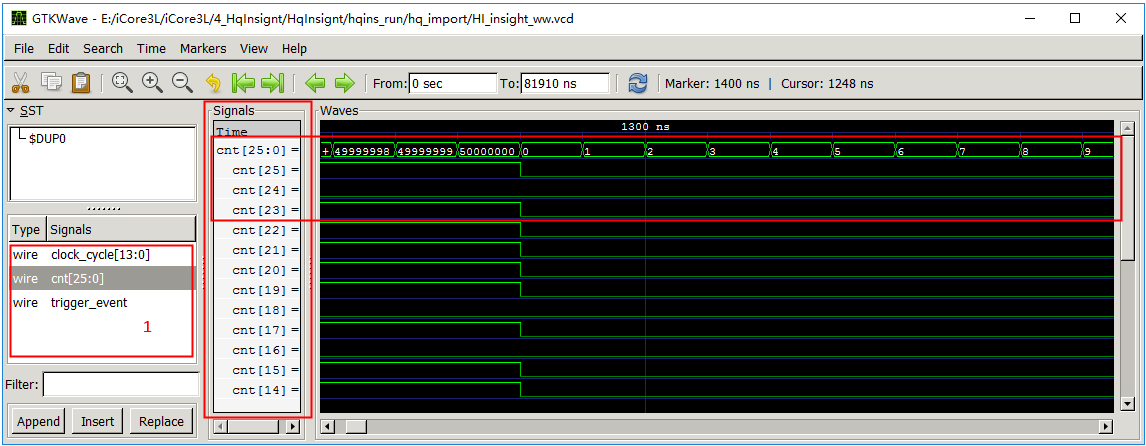

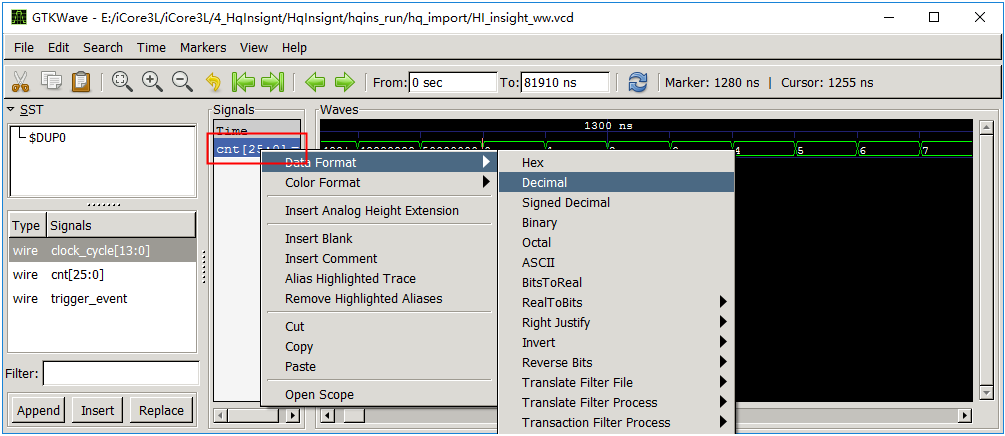

4、查看波形

icore3l_fpga_4.txt · 最后更改: 2022/03/19 15:25 由 sean