icore3l_fpga_6

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-11-18 | zgf | 初次建立 |

实验六:乘法器IP核的调用

一、 实验目的

- 学习HqFPGA软件中调用IP核的方法。

- 学习在工程中调用乘法器IP核的设计方法。

二、 实验设备

- iCore3L双核心开发板。

- XiST USB Cable 或相同功能的下载器。

- 装有HqFPGA开发环境的电脑。

三、 实验原理

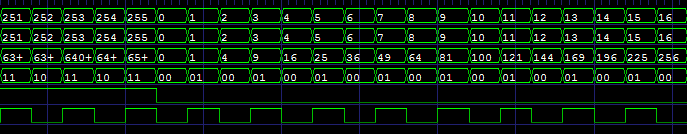

- 本实验主要是为了学习HqFpga软件乘法器IP核的调用方法,以及在工程中例化乘法器的方法,实验内容较为简单,变量a和变量b作为乘法器IP核的两个输入变量,变量q作为乘法器IP核的输出变量,以达到利用乘法器实现a*b=q的简单乘法运算。

- 其中变量a和变量b是通过自加的方式循环变化的;输出变量的最高位和最低位用于控制LED,同时可以通过Hqinsight查看波形,验证乘法运算的正确性。

四、 操作步骤

下面就讲一下调用乘法器IP核的具体步骤。

1、建立工程

- 打开HqFpga开发软件,点击左侧栏的“新建工程”按钮,目标器件选择SL2S-25E-8U213C,设计输入类型选择RTL。

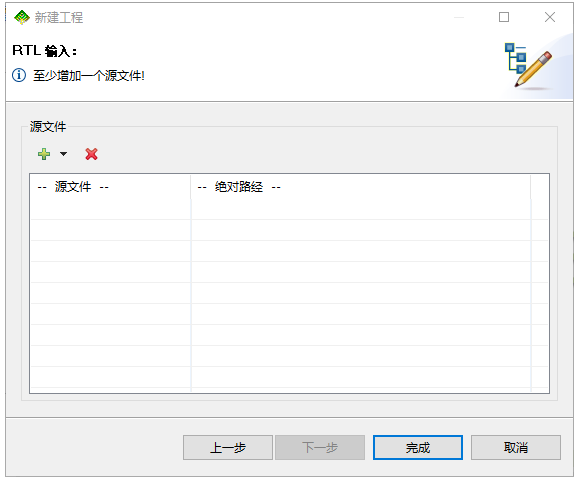

- RTL输入界面点击绿色“+”,将例程下的源文件添加到工程中,或者直接点击“完成”,在“设计管理”界面建立源文件。

2、建立乘法器IP核文件

- 1. 点击左侧边栏的“IP管理”按钮,添加IP核。

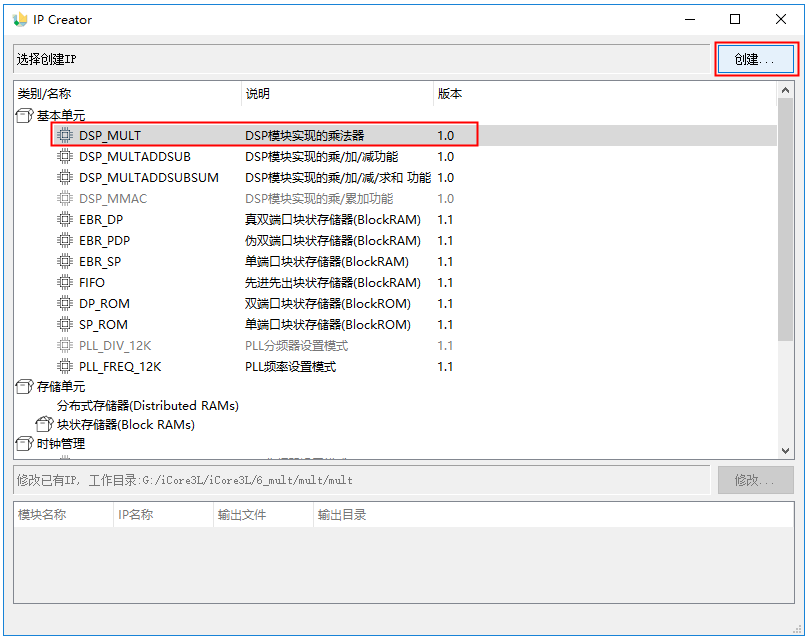

- 2. 弹出IP Creator界面,在基本单元栏,双击选中“DSP模块实现的乘法器”,或者选中“DSP模块实现的乘法器”后点击右上角的“创建”按钮,进入IP核配置界面。

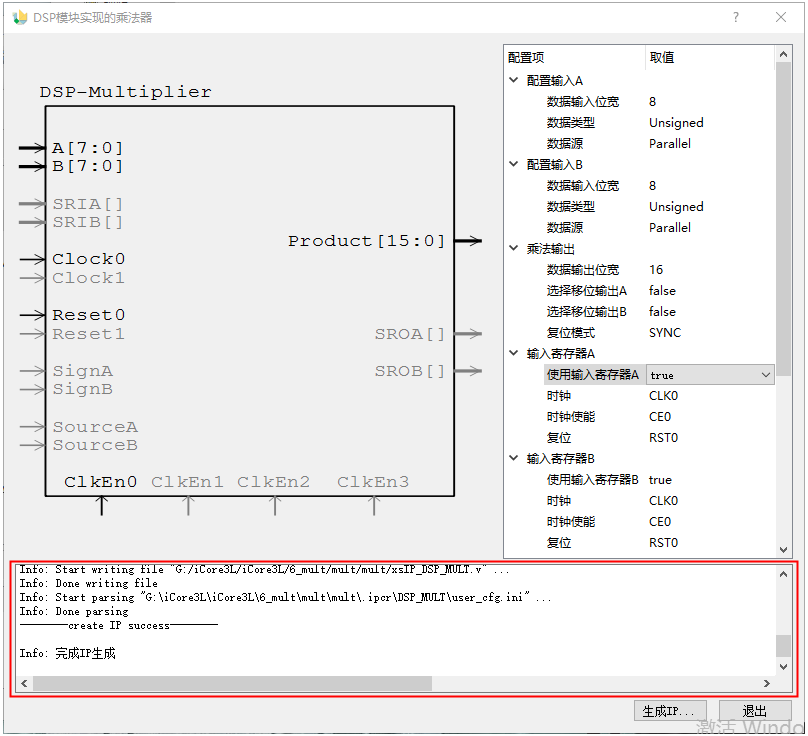

- 3. 弹出的乘法器IP核配置界面,左边显示了乘法器IP核的信号端口,右边则可以对乘法器IP核做相关的参数设置。本实验以输入数据AB位宽为8、输出位宽为16为例进行设置。设置好参数之后,点击右下角的“生成IP…”按钮。

- 4. 弹出保存界面,设置好模块名称、文件名称、输出目录等项之后,点击“开始”按钮,生成IP核文件。

- 5. IP核生成之后,在乘法器配置界面下方的信息输出栏,可以看到“完成IP生成”的信息提示,如下图所示:

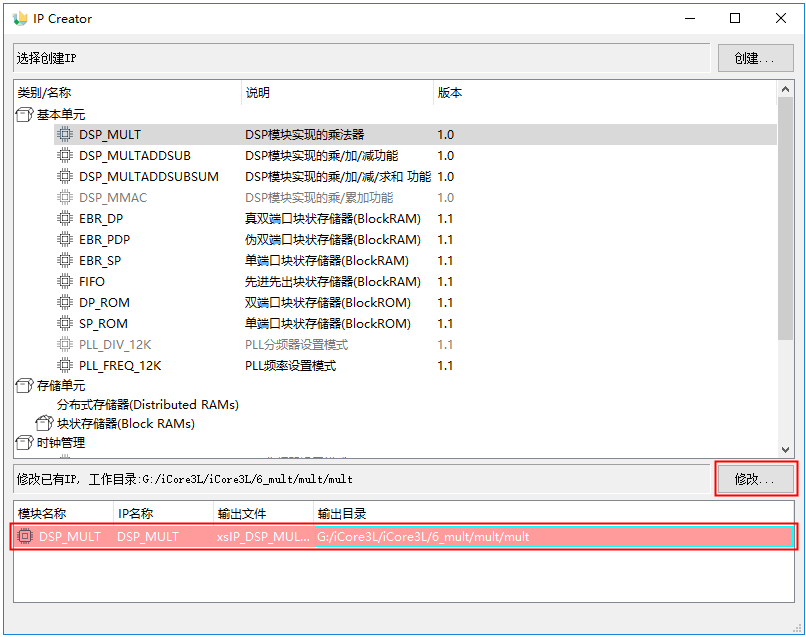

- 6. 然后点击乘法器配置界面的“退出”按钮,可以看到,IP Creator界面下方的信息输出窗口,已经有了乘法器IP核。通过双击或者单击“修改”按钮,可以对IP核参数进行修改。

3、添加IP核文件

- 如果建立工程时未添加例程下的源文件,点击左侧边栏的“设计管理”按钮,弹出“设计管理”界面,点击“新建文件”按钮,新建源文件。如果建立工程时添加了例程下的源文件,则直接进行下一步。

- 点击“语法检查”按钮,查看源代码输入是否有语法错误,如无报错,点击“保存”按钮;弹出窗口中将文件命名为mult.v,完成顶层模块的建立。

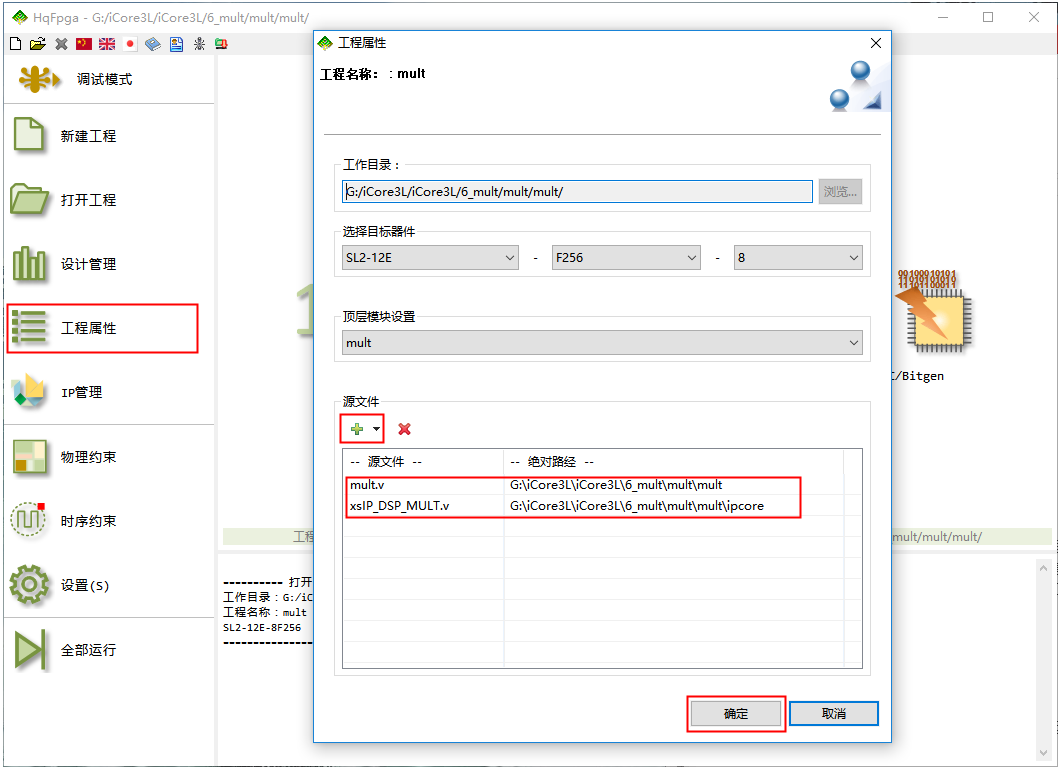

- 点击主界面左侧栏的“工程属性”按钮,弹出“工程属性”界面,在界面下方的“源文件”一栏,点击“+”号,将建立的顶层模块文件(mult.v)及乘法器IP核文件(xsIP_DSP_MULT.v)添加到工程里。

4、例化乘法器IP核及代码讲解

- 工程中添加完乘法器IP核文件后,还要在模块中调用乘法器模块才能在FPGA中构建乘法器电路。在本例程中,通过如下语法对乘法器IP核进行调用:

//-------------------- mult IP Core-------------------// DSP_MULT u0( //调用乘法器IP核 .A(a), .B(b), .Product(q) );

- 这段代码是通过例化的方式对IP核进行调用,例化的语法格式如下:

IP核模块名 例化名( .IP核信号列表 (连接到IP核该端口的信号), .IP核信号列表 (连接到IP核该端口的变量), ... ... .IP 核信号列表 (连接到IP核该端口的变量) );

- IP核模块名可以在IP核文件中找到,打开IP核文件,可以看到下图中黄色背景行代码。在关键字module后面的就是IP核的模块名,括号中是IP核模块的信号列表。

- 再来看一下变量a、b,作为乘法器的输入变量,a和b的值一直在循环变化。a和b采用累加的方式,每个时钟上升沿触发一次,计满255归零。之后使用assign 语句,将输出变量q的最高位和最低位分别用于控制三色LED的红色和绿色显示。

//----------------------------- a、b-------------------------------// always@(posedge fpga_clk or negedge rst_n) if(!rst_n) begin a<=8'd0; b<=8'd0; end else if(a==8'd255) //循环累加到255,然后归零 begin a<=8'd0; b<=8'd0; end else begin //输入变量a、b进行累加操作 a<=a+1'd1; b<=b+1'd1; end //取输出变量的最高位控制红色LED,绿色LED常亮,取输出变量的最低位控制蓝色LED assign fpga_led={q[15],1'd0,q[0]};

五、 实验结果

icore3l_fpga_6.txt · 最后更改: 2022/03/19 15:26 由 sean