icore3l_fpga_9

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-11-23 | zgf | 初次建立 |

实验九:软件复位信号实验——全局复位信号

一、 实验目的与意义

- 掌握计数器的使用方法。

- 掌握HqFpga的使用方法。

- 掌握软件复位信号的工作原理及使用方法。

二、 实验设备及平台

- iCore3L 双核心板。

- XiST USB Cable(或相同功能)仿真器。

- Micro USB线缆。

- 带有HqFpga开发平台的电脑。

三、 实验原理

- 复位指的是在可编程器件、可编程控制器等电子设备中,为防止程序跑飞或者保证多个子程序同时运行,在程序中手动或者自动的方法使软硬件恢复到一个特定的工作节点的过程,而这个手动或自动控制的信号就是复位信号。

- 常用的复位方式有三种:

- 硬件复位:复位信号接一个拨码开关或者按键等。

- 控制芯片:控制芯片产生复位脉冲。

- 电源芯片:由电源芯片在上电的时候产生的复位信号。

- 在FPGA程序中,一个复杂的功能由多个子模块共同完成,为了保证各个子模块同时运行,需要一个全局复位信号;如果没有设计复位按键,没有专用的电源或者控制芯片的时候,为了保证FPGA从一个稳定的状态开始运行,这里可以采用上电“软”复位的操作方式,既通过通过计数器计数,当计数到一定值的时候,产生一个脉冲信号作为系统的复位信号。

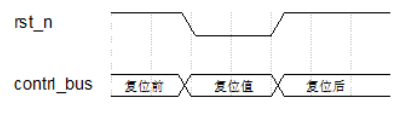

- 其设计原理时序如图9-1所示:

- 如图所示,其复位原理是:将复位信号作为程序控制的触发信号,在复位信号(rst_n)下降沿处对控制总线进行复位,将其赋值为复位值,有效复位信号(低电平)结束后,可根据需要对控制总线重新进行赋值。

- 想实现这一设计,在FPGA上电后,对时钟信号进行计数,计数到一定值的时候,将rst_n信号拉低(或者拉高),持续一段时间,然后拉高(或者拉低),产生一个低(高)电平的脉冲信号,以此脉冲信号作为FPGA内部的复位信号。

四、 代码讲解

- 复位信号的产生原理是:首先做一个产生复位信号的计数器always块,然后利用条件运算符和关系运算符产生一个短时间内具有低电平的的信号,将该信号作为复位信号。其代码如下:

//生成复位信号的计数器,采用时序逻辑语言描述 reg [31:0] rst_cnt; always@(posedge fpga_clk)//为了便于观察复位时的现象,这里将上电后复位的时间延后,且复位时间拉长 begin if(rst_cnt<32'd250000000) begin rst_cnt <= rst_cnt + 1'd1; end else if(rst_cnt==32'd250000000) begin rst_cnt <= rst_cnt; end else rst_cnt<=32'd0; end wire rst_n = ((rst_cnt>32'd175000000) && (rst_cnt<32'd200000010)) ? 1'd0 : 1'd1;//采用组合逻辑产生复位信号

- 为了方便观察程序运行效果,例程中加入了LED控制程序,用于程序运行展示。当处于复位状态时,FPGA_LED显示为红色,当非复位状态时FPGA_LED显示为蓝色。代码如下:

reg [2:0] led_r; always@(posedge fpga_clk or negedge rst_n) if(!rst_n) led_r<=3'b011; //三色led 红色亮起 else led_r<=3'b110; //三色led 蓝色亮起

五、 实验步骤及实验结果

- 打开HqFpga软件,新建工程,FPGA型号为SL2S-25E-8U213C。通过“工程属性”界面将例程下的源文件添加到新建立的工程,或者通过“设计管理”界面建立新的源文件并添加到工程中。

- 将编写好的代码进行编译,检查语法错误;

- 编译通过后添加物理约束,绑定引脚信息;

- 点击左侧栏“全部运行”按钮,进行全编译;

- 编译通过后,将生成的bit文件下载到iCore3L开发板;

- 实验现象:

- 下载成功后,FPGA_LED会显示为蓝色,5秒后会显示约1秒钟红色,之后再显示为蓝色。这个变化的过程表明程序成功运行,并在运行约5秒后成功产生了复位信号,受复位操作影响,LED在复位状态显示为红色,完成复位操作后又切换为蓝色显示。

六、 拓展实验

1、通过HqInSight工具采集复位信号和led控制信号,看是否与其工作原理一致;

icore3l_fpga_9.txt · 最后更改: 2022/03/19 15:27 由 sean