icore3lfpga_0

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 购买链接 | 敬请期待 | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V0.1 | 20201010 | zgf | 初次建立 |

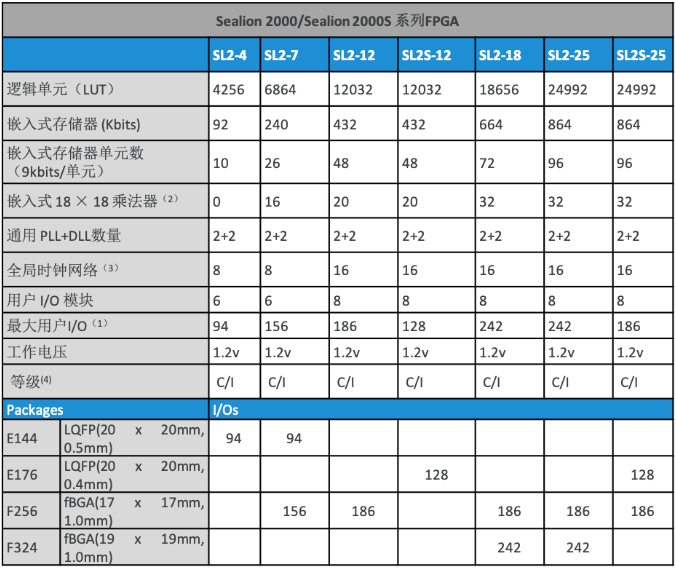

实验0:认识Sealion 2000 系列FPGA产品特性

| iCore3L采用国产器件方案,FPGA选择的是西安智多晶的 Sealion 2000系列的FPGA,型号为SL2S-25E-8U213C。这是一款采用55nm低功耗技术工艺的低成本FPGA,可以实现较高功能性的产品。下面介绍一下这款FPGA的一些产品特性。 |

一、器件特性:

- 低成本、低功耗的 FPGA 架构;

- 基于 55 纳米技术工艺(55nm),4K 到 25K 的查找表逻辑单元;

- 嵌入式高速双接口存储器(dual port SRAM/FIFO Block)(真双端口/ 伪双端口);

- 内置多个 18×18/9×9 可串行乘法器以及算数逻辑单元(ALU),可做 两层叠加实现 DSP 处理密集型应用;

- 最高可达到 335 个有效用户 I/O;

- 高达 840Mbps 发送器(Tx),875Mbps Rx 的 LVDS 接口,时钟延迟匹配电路,7:1 LVDS 界面;

- 支持 200MHz 的 DDR2 SDRAM 接口;

- DQS 输入端 90 度相位转换

- DQS 输入端到系统时钟接轨(clock domain transfer)

- 支持 167MHz 的 SDR SDRAM;

- 支持 MIPI.D-PHY 等效,1.2Gbps;

- 集成 2M*32bit 的 SDRAM

- 单一封装集成 FPGA 和 SDRAM 双芯片

- 每器件中拥有 2 个内置锁相环(PLLs)和 2 个延迟锁相环(DLLs

- 提供倍频、分频、相位转移等系统时钟功能,包含展频功能。

- 5K/7K 设备提供嵌入式闪存,可容纳两套比特流,及 500k 用户闪存; 在微秒内通电,个人密码设置的安全性;带外部 SPI 内存的双引导

- 支持商业与工业温度等级

二、器件资源:

- 管脚列表文件中的用户 I/O 管脚包括所有的通用 I/O 管脚、专用时钟管脚以及两用配 置管脚。收发器管脚和专用配置管脚不包括在这一管脚列表中。

- 嵌入式 18 × 18 乘法器均为 DSP 硬核,可做乘法器兼累加器。

- 16 个全局时钟均包含 8 个主时钟及 8 个次时钟。

- 等级:

- C:商业级,工作温度: 0℃ - 85℃

- I:工业级,工作温度:-40℃ - 100℃

三、体系结构

- 从以下几个方面介绍sealion 2000 系列FPGA体系结构

- FPGA核心架构;

- I/O特性;

- 时钟管理;

- 外部存储器接口;

- 配置。

1、核心架构

- 本系列FPGA的核心架构是由四输入查找表(LUTs),逻辑单元存储器模块以及乘法器构成。嵌入式存储器模块有9Kbit的SRAM存储器。可以把嵌入式存储器模块配置成单端口、伪双端口、真双端口、RAM以及FIFO换从器或者ROM,通过配置也可以实现特定数据宽度的存储器模块。

2、I/O特性

- 本系列 FPGA 器件的 I/O 支持可编程总线保持、可编程上拉电阻、可编程下 拉电阻、可编程延迟、可编程驱动能力以及可编程 slew-rate 控制,从而实现 了信号完整性以及热插拔的优化。

- 本系列FPGA器件同时还支持驱动阻抗匹配。

3、时钟管理

- 本系列 FPGA 中,12K 逻辑资源 FPGA 器件包含了 8 个全局时钟(GCLK)网络, 和 8 个高扇出网路;25K 逻辑资源 FPGA 器件包含了 16 个全局时钟(GCLK)网络, 其中 8 个全局时钟可以复用为高扇出网路。

- 本系列 FPGA 的器件有 2 个 PLL(每个 PLL 上均有五个输出端)和 2 个 DLL, 以提供可靠的时钟管理与综合。可以在 HqFpga 软件中对 PLL 进行重配置时钟 频率或者相位。

4、外部存储器接口

- 本系列 FPGA 器件支持 SDR、DDR、DDR2 等 SDRAM 接口。接口可能位于器件 的一个或多个 I/O 模块(I/O bank),以实现更灵活的电路板设计。

- 本系列 FPGA 器件 DDR SDRAM 存储器接口解决方案,由一个 PHY 接口和一 个存储控制器组成。智多晶提供了 PHY 接口 IP,您可以将它与您自己定制的存 储控制器或智多晶提供的存储控制器一起使用。

5、配置

- 本系列 FPGA 器件使用 SRAM 单元存储配置数据。每次 FPGA 上电后,配置数 据会被下载到 FPGA 中。低成本配置选项包括串行被动模式、串行主动 SPI 模式 和串行 JTAG 模式。这些选项实现了通用应用程序的灵活性,并提供了满足特定 配置以及应用程序唤醒时间要求的能力。

- 详细内容可阅读Sealion 2000 系列FPGA芯片手册了解。

icore3lfpga_0.txt · 最后更改: 2020/10/10 16:18 由 zgf