icore3lfpga_1

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 购买链接 | 敬请期待 | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V0.1 | 20201010 | zgf | 初次建立 |

实验一:认识Hqfpga开发软件——环境搭建与调试下载

- HqFpga是西安智多晶微电子有限公司(XIST)旗下的FPGA开发软件。HqFpga2.8.5目前支持Sealion2000系列FPGA器件。

- HqFpga在单一的可执行文件中集成了从综合、布局、布线等所有FPGA实现功能。而其他FPGA设计软件是将各个功能用不同的可执行文件来实现,虽然这些单独的执行文件也集成在一个软件系统中,但是不同的可执行文件之间只能通过文件接口来传递设计信息,造成工作重复(每个可执行文件都要进行数据读入、输出)、运行时间长(大量工作浪费在接口转换上)、无法全局优化等问题。

- HqFpga在同一可执行环境下所继承各项功能,可以共享所有信息,例如统一的数据模型、时序分析结果等、HqFpga还提供一键式(Push-Button)的运行模式,并提供多种界面语言,方便用户完成简单、快速、高效及优化的FPGA开发。

一、 环境搭建

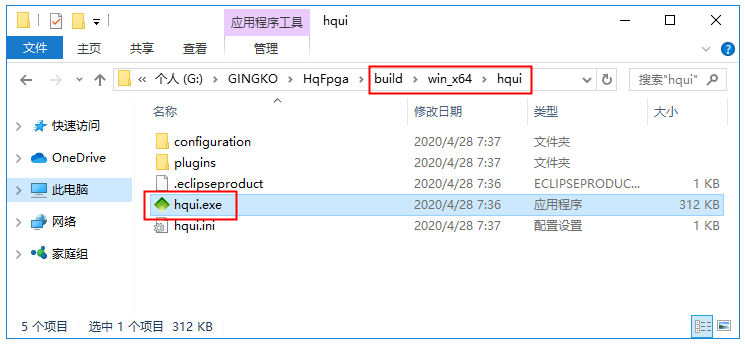

- HqFpga软件是一个免安装的开发环境,用户只需将HqFpga 软件包直接解压缩至目标目录,即可完成安装。只需找到图1-1中所示程序,双击运行即可打开HqFpga开发环境;为方便使用,可以在合适的位置给此应用程序建立快捷方式。

- 在Windows平台上,如果提供了安装程序(名为“setup_hqfpga.exe”或相似名称的程序),用户可直接运行该安装程序并按照相应指示完成安装。

- HqFpga的图形用户界面程序为:

- <安装目录>/build/<platform>/hqui/hqui[.exe]

- HqFpga的主程序为:

- <安装目录>/build/<platform>/bin/hqui[.exe]

- 其中<platform>可以是:

- linux26_x86_64 linux内核2.6 64位操作系统

- win_x86 Windows X86 32位操作系统

- win_x64 Windows X86 64位操作系统

- 安装后的HqFpga包含如下内容:

- Build/ 包含HqFpga主执行文件以及辅助文件

- doc/ 包含HqFpga的帮助文档

- samples/ 包含示例文件是的用户能快速学习使用HqFpga

- 注意:

- 如果将HqFpga 安装到windows系统目录下,例如:“C:\Program Files”或者“C:\Program Files(X86)”,用户必须用管理员权限运行HqFpga。

- 如果HqFpga 在运行过程中发生任何异常的文件或者目录错误,建议关掉防病毒软件再重试。

二、 软件介绍

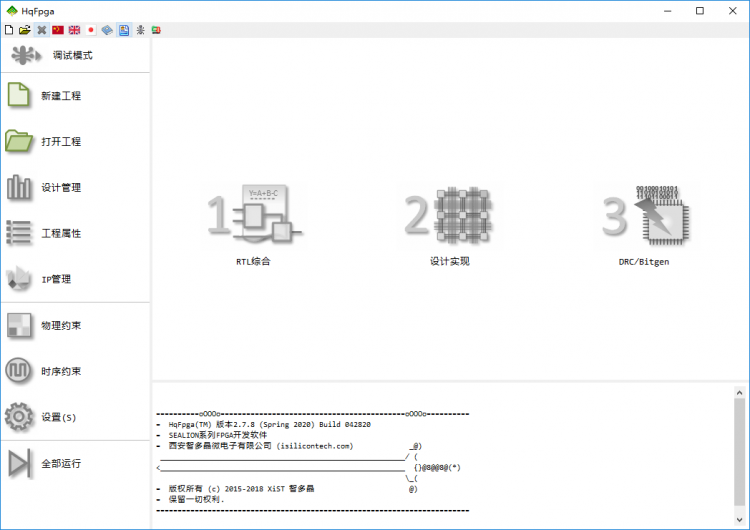

- 通过双击安装目录/hqui/子目录下的可执行文件hqui.exe启动HqFpga GUI,可以看到HqFpga界面包含三个主操作按钮,如图1-2所示:

- RTL综合

- 设计实现

- DRC/Bitgen

- 分别对应设计的三个主要步骤:

- 设计输入——》设计实现——》设计校验(DRC)及位流生成。

1、 RTL综合

- 通过点击“RTL综合”按钮可以运行指定的RTL综合工具。

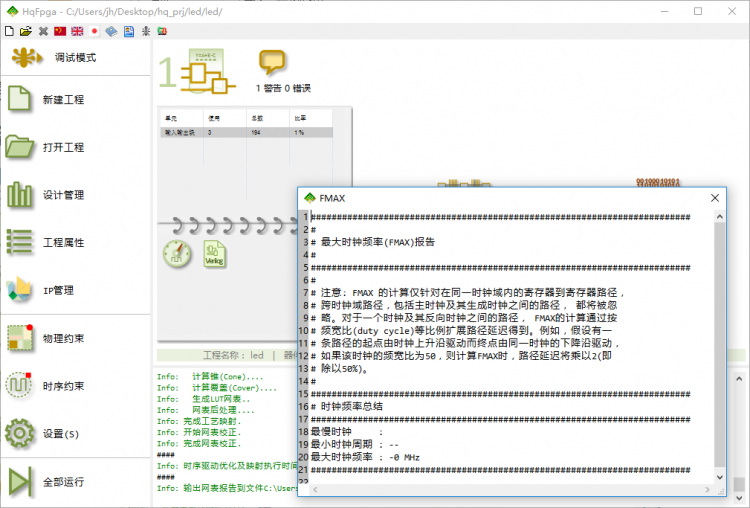

- 当RTL综合完成后,会在图形界面上会产生一个大的活页标签,标签上半部分显示综合后的FPGA资源利用的概要信息以及最大时钟频率值。用户可以在资源利用概要信息上方,通过鼠标悬停弹出对话框查看完整的资源利用信息,如图1-4中所示。用户还可以鼠标单击最大时钟频率(FMAX)值,弹出对话框显示FAMX相关的详细时序路径信息。

- 注意:

- 由于FPGA布局布线尚未完成,所以资源利用信息与最终实际占用的FPGA资源信息可能会有出入。

2、 设计实现

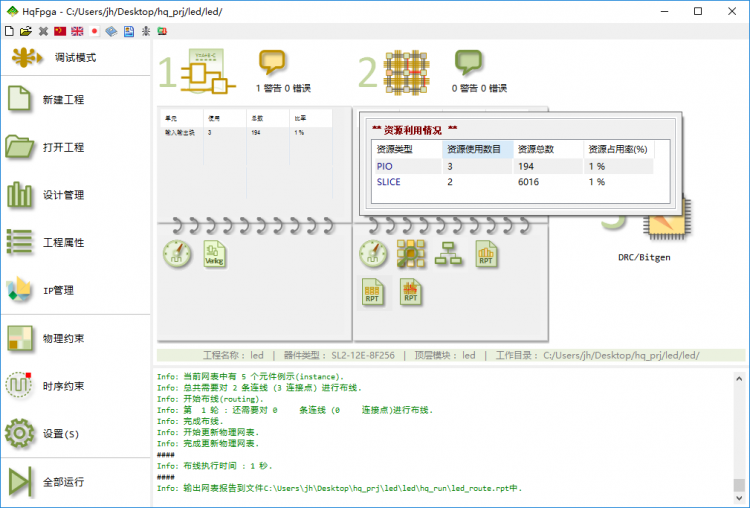

- 用户可通过点击“设计实现”按钮,进行布局布线等操作。设计实现过程运行完毕后,图形界面上会产生一个大的活页标签,标签上半部分显示FPGA实现后资源利用的概要信息以及最大时钟频率值。用户还可以在资源利用概要信息上方通过鼠标悬停弹出对话框查看完整的资源利用信息。通过鼠标单击最大时钟频率(FMAX)值,弹出对话框显示FMAX相关的详细时序路径信息,如图1-5中所示。

- 与RTL综合后显示的资源利用信息不同,这里所显示的是最终的FPGA资源占用结果。同样,与RTL综合显示的FMAX的预估值不同,这里所显示的FMAX值是最终的确定值。

- “设计实现”完成后产生的活页下半页上有几个功能按钮,可用于分析检查设计实现结果,如进行时序分析和查看详细布局信息等等。

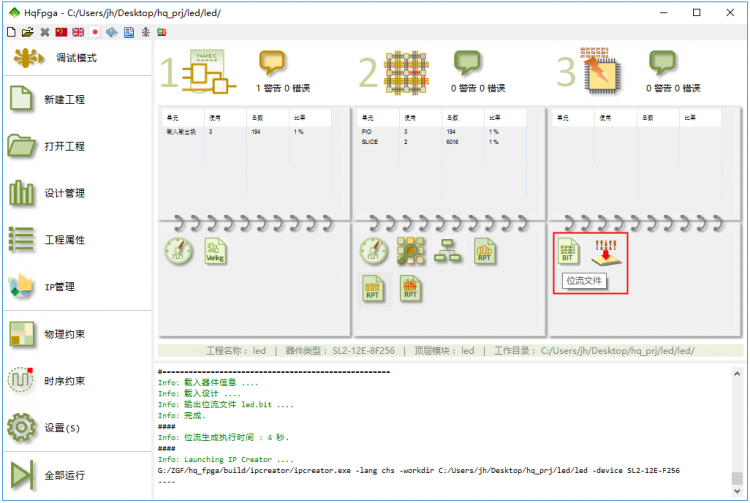

3、 DRC和Bitgen

- 设计实现通过之后,“生成位流”按钮激活,点击“RDC/Bitgen”按钮进行设计规则检查(DRC)并生成位流(Bitstream)文件。

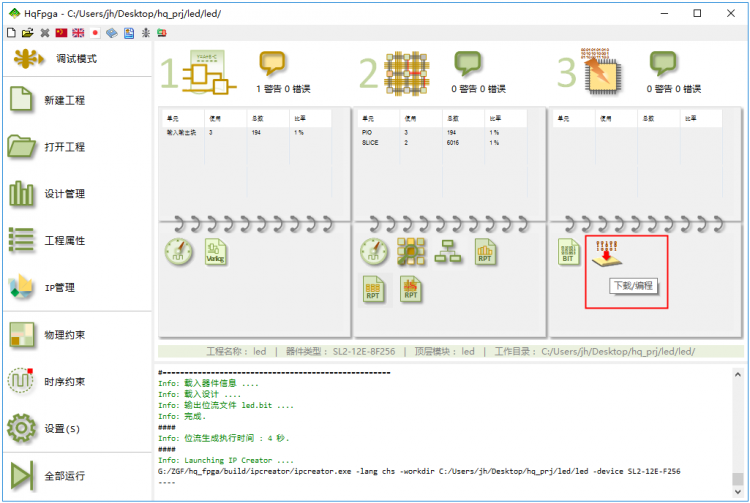

- 可以看到,DRC通过后,产生活页的下半页有“位流文件”和“下载编程”两个选项,如图1-6中红框中所示。

- 点击活页中的“下载/编程”选项。

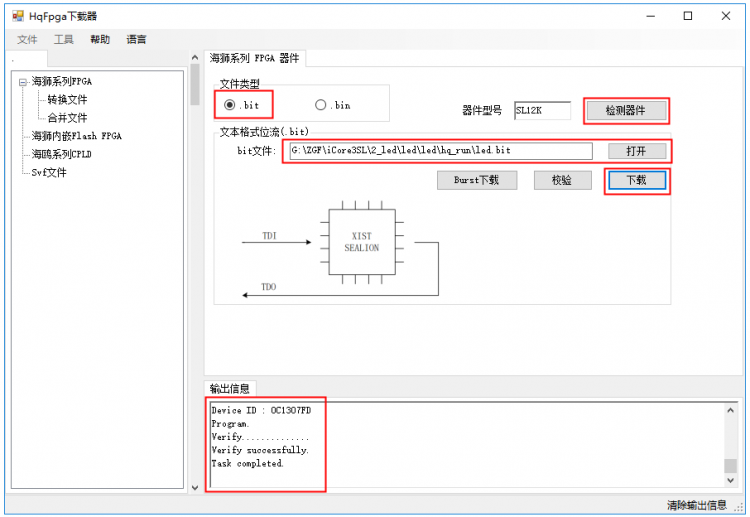

- 将下载器和核心板与电脑连接,并给核心版供电。弹出的下载界面如图1-8所示,点击界面中“检测器件”按钮,可以查看检测到的器件型号与工程设置中型号是否一致。然后点击“打开”按钮找到DRC产生的bit文件并选中,再点击“下载”按钮;输出信息窗口会给出是否下载成功的提示。如果下载失败,可尝试给核心板重新上电后再次下载。

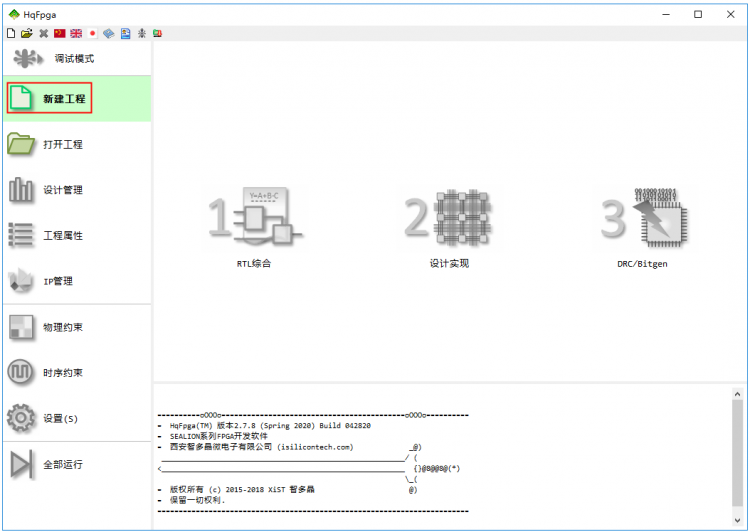

4、 新建工程

- 利用HqFpga进行设计时,对每个新的设计需要建立与之对应的工程,用于保存设计的各种信息:目标器件,源文件、中间文件、设计结果等。

- 通过单击“新建工程”按钮建立新工程。

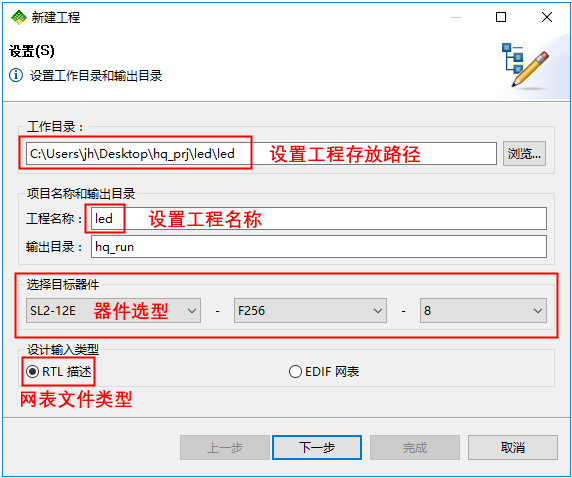

- 点击“新建工程”按钮,会弹出“新建工程”窗口,如图1-10中所示;在此窗口中可以设置工程存放路径、给工程命名,以及器件选型、设计输入格式选择等。

- 注意:

- 不能把工作目录放在Windows的系统目录及其子目录下,包括(但不限于):桌面目录:C:\user\…\desktop, windows目录C:\Windows,程序安装目录C:\Program Files 或 Program Files(X86),等等。另外,工作目录名称中不能包含特殊字符,例如空格、括号等,也不建议包含中文字符。

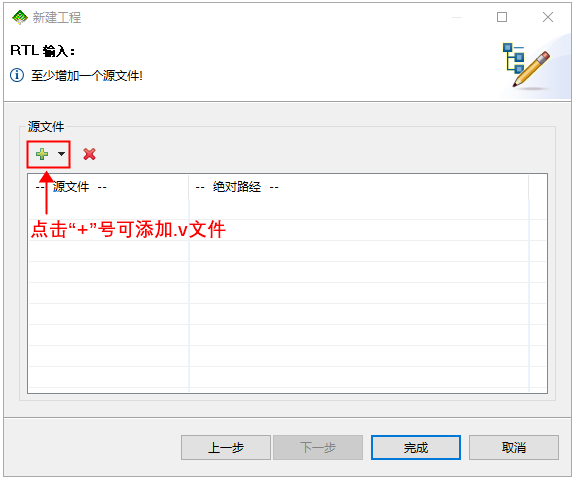

- 在“新建工程”窗口中点击“下一步”,会弹出RTL输入设置界面,点击界面中的“+”号可以添加源文件或者网表文件,如图1-11中所示。也可以直接点击“完成”按钮,后面再新建源文件。

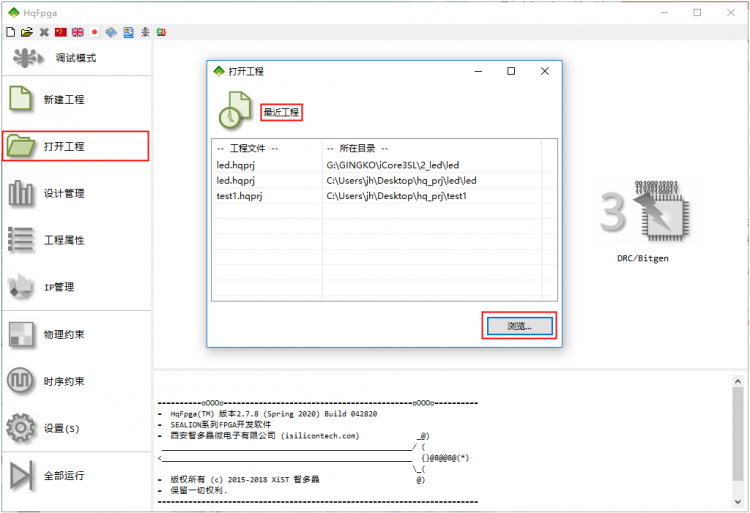

5、 打开工程

6、 设计管理

- 如果需要新建源文件,可以点击界面左侧栏里的“设计管理”按钮,进入“设计管理器”界面,通过点击“新建文件”图标建立源文件;在编辑区输入编辑内容后可以点击“语法检查”按钮,检查语法错误。语法检查通过后,点击“保存”按钮,保存文件并命名,完成源文件的建立。

7、 工程属性

8、 IP管理

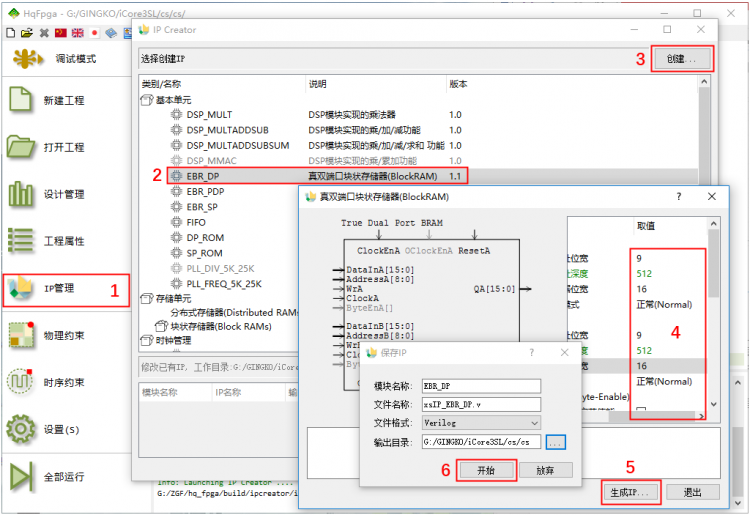

- 点击左侧栏的“IP管理”按钮,弹出“IP Creator”窗口,此窗口内选择需要的IP核,点击右上角的“创建…”按钮,弹出IP核设置界面;设置好IP核相关参数,点击右下角的“生成IP…”,弹出IP核文件保存窗口;将IP核的模块名、文件名、输出目录设置好之后,点击“开始”按钮,即可完成对IP核的创建,如图1-15中数字所示操作顺序。

9、 添加约束

1)、物理约束

- “RTL综合”正常完成后,“设计实现”按钮激活,点击该按钮即可进行FPGA后端设计实现过程,如布局布线等。通常在设计实现之前,用户往往需要加入时序或者物理设计约束。添加约束时,用户可以通过HqFpga自带的约束编辑器新增、修改时序或物理约束。

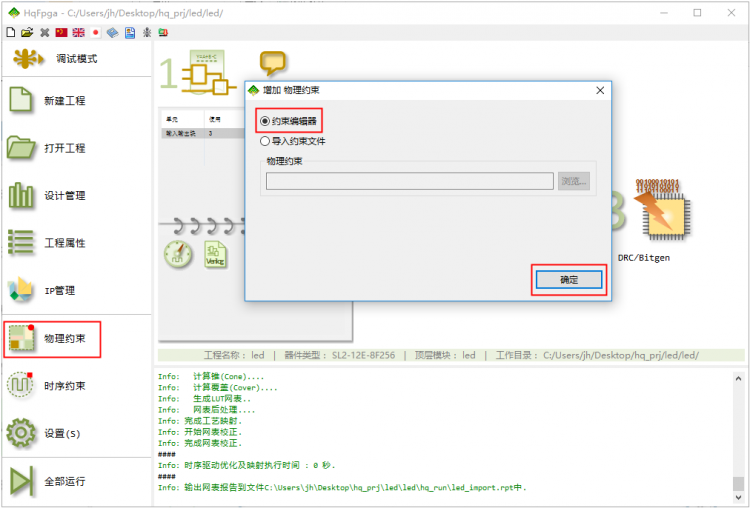

- 点击左侧栏里“物理约束”按钮,弹出的对话框中选择约束编辑器,然后点击确定,如图1-16所示。

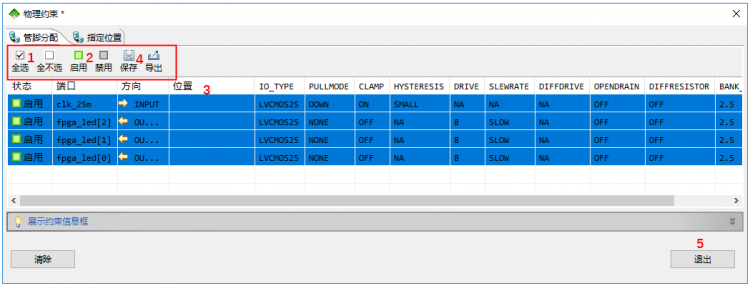

- 之后弹出如下窗口,勾选1处的“全选”,然后点击2处的“启用”;或者直接单击3位置栏里的空白处。之后根据硬件信息在3处设置引脚绑定信息。最后点击4处的保存和5处的退出按钮。

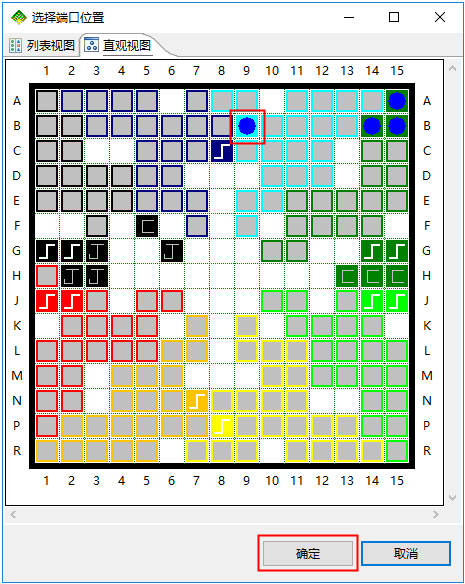

- 在信号列表对应的位置栏下单击,会出现一个带“…”的框,点击那个框,会出现“选择端口位置”窗口,在“直观视图”界面,点击相应位置,然后点击确定,即可完成引脚的绑定。

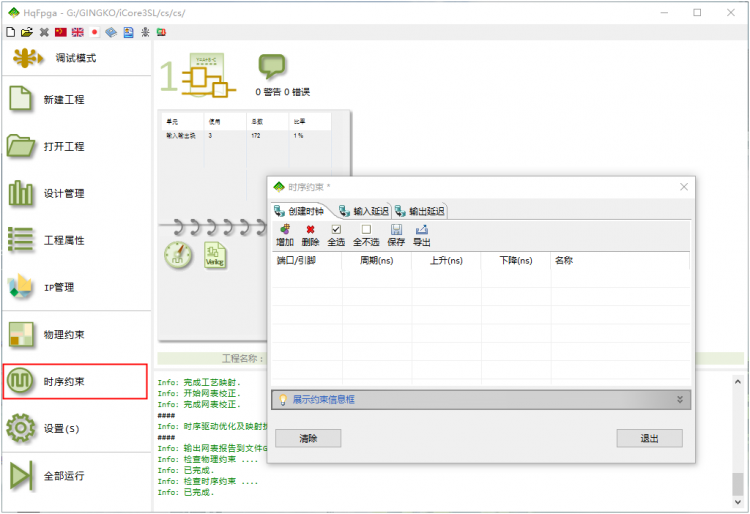

2)、时序约束

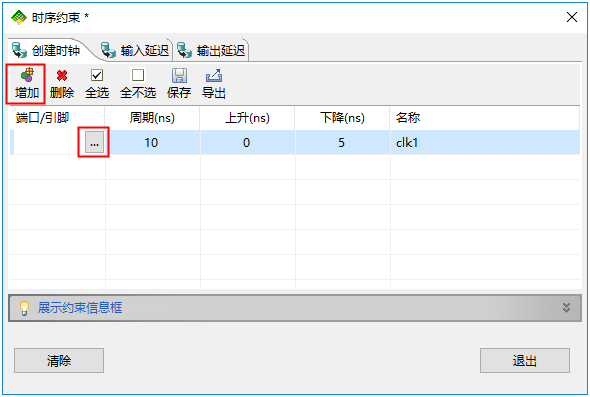

- 点击左侧栏“时序约束”按钮,可对信号进行时序约束设置。点击之后,弹出如图1-19所示设置窗口,可以对时钟、输入输出信号进行相关设置。

- 以时钟信号为例,点击“增加”按钮,在“端口/引脚”栏单击,会出现一个带“…”的方框。

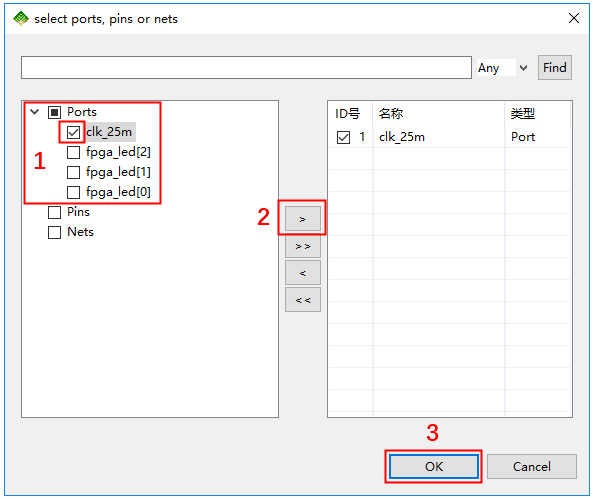

- 点击图1-20中红框内的方框,弹出如下窗口,点击“Ports”前面的“>”,在下拉列表中 点击“clk_25m”前面的框,勾选此信号,然后点击2处的“>”,可以看到在右边信号列表中添加了此信号。然后点击3处的“OK”,完成时钟信号的添加。

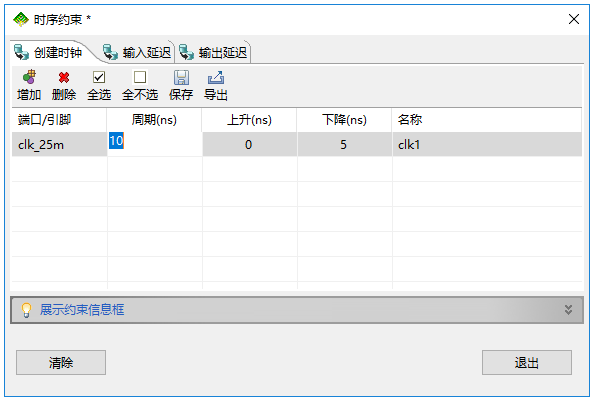

- 添加完成后,可对添加信号的时序约束参数进行调整。输入输出的时序设置与此类似,不再赘述。

10、设置

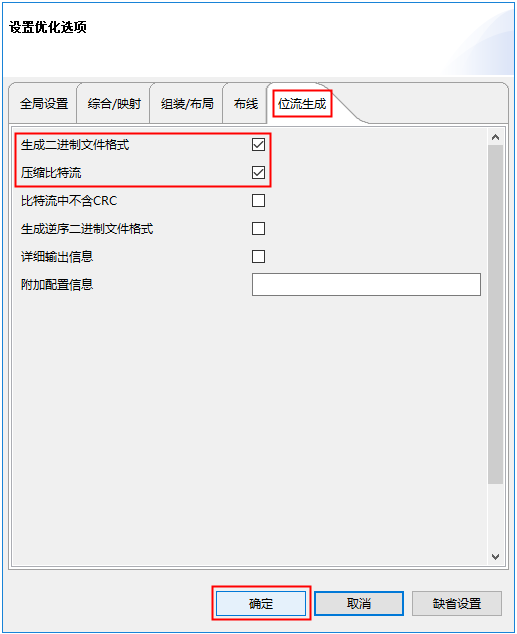

- 设置是对工程优化进行设置,点击主界面左侧栏的“设置(S)”按钮,弹出“设置优化选项”窗口如图1-23,可以进行全局优化设置,可以对综合、布局布线、位流生成等内容进行优化设置。

- 这里特别讲一下“位流生成”页面;HqFpga默认是生成 .bit格式的下载文件,可用于JTAG模式下载;如果在“位流生成”界面勾选了“瑟生成二进制文件格式”和“压缩比特流”两个选项,则HqFpga生成 .bin格式的下载文件,可用于mspi下载模式。

- 至此,整个软件界面基本介绍完毕,“调试模式”会单独作为一个例程来讲解。

- 了解完开发环境,接下来就简述一下使用HqFpga开发环境进行设计的基本步骤:

- 点击左侧边栏的“新建工程”按钮;

- 弹出窗口中设置工作目录、工程名称,选择目标器件,确定设计输入类型,点击“下一步”。

- 弹出“新建工程”页面,如果有源文件,在此界面添加源文件,如果没有源文件,直接点击完成。

- 如果没有源文件,点击“设计管理”按钮,弹出“设计管理”界面;点击新建文件,在编辑区输入代码,然后点击“语法检错”按钮;待无报错后,点击保存,给源文件命名。

- 点击“工程属性”,将新建的源文件添加到工程中。

- 点击“RTL综合”,运行综合工具,查看综合结果。

- 综合通过后,点击“物理约束”,绑定引脚信息。

- 点击“时序约束”按钮,对时钟、输入输出信号进行时序约束。

- 点击“设计实现”按钮,进行布局布线。

- 布局布线完成后,点击“设置(S)”按钮,进行优化设置。

- 点击“DRC/Bitgen”按钮,进行DRC检测以及生成位流文件。

- 点击“DRC/Bitgen”生成活页下半部分里的“下载\编程”按钮。

- 弹出的“HqFpga下载器”界面中,设置下载文件格式,点击“检测器件”按钮;点击“打开”按钮,找到生成的 .bit文件,选中并点击下载。

- 下载成功后“HqFpga 下载器”的信息输出窗口会先向对应的提示。

icore3lfpga_1.txt · 最后更改: 2020/10/10 18:17 由 zgf