icore4tx_fpga_10

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-05-21 | gingko | 初次建立 |

实验十:PWM输出实验——不同PWM输出

一、实验目的与意义

- 掌握输出不同占空比PWM的原理及方法。

- 掌握宏定义、参数变量的使用方法。

- 掌握ISE的使用方法。

二、实验设备及平台

- iCore4TX 双核心板。点击购买

- USB-CABLE(或相同功能)的仿真器。

- Micro USB线缆。

- ISE开发平台。

- 电脑一台。

三、实验原理

- PWM全称是Pulse Width Modulation,是脉冲宽度调制缩写。它是通过对脉冲宽度进行调制,等效输出所需要的波形。在PWM波形属性中频率和占空比是两个非常重要的参数。而本实验的主要目的就是通过FPGA的硬件语言描述实现不同频率、占空比的PWM信号输出。

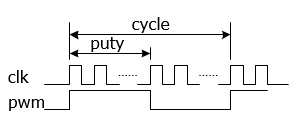

- FPGA产生不同频率不同占空比的的原理是基于计数器实现的,通过对参考时钟进行计数,控制某个信号高低电平输出实现频率和占空比的变化。其实现原理如图10.1所示,通过改变puty的值改变pwm的占空比,通过改变cycle的值改变pwm的频率。

四、代码讲解

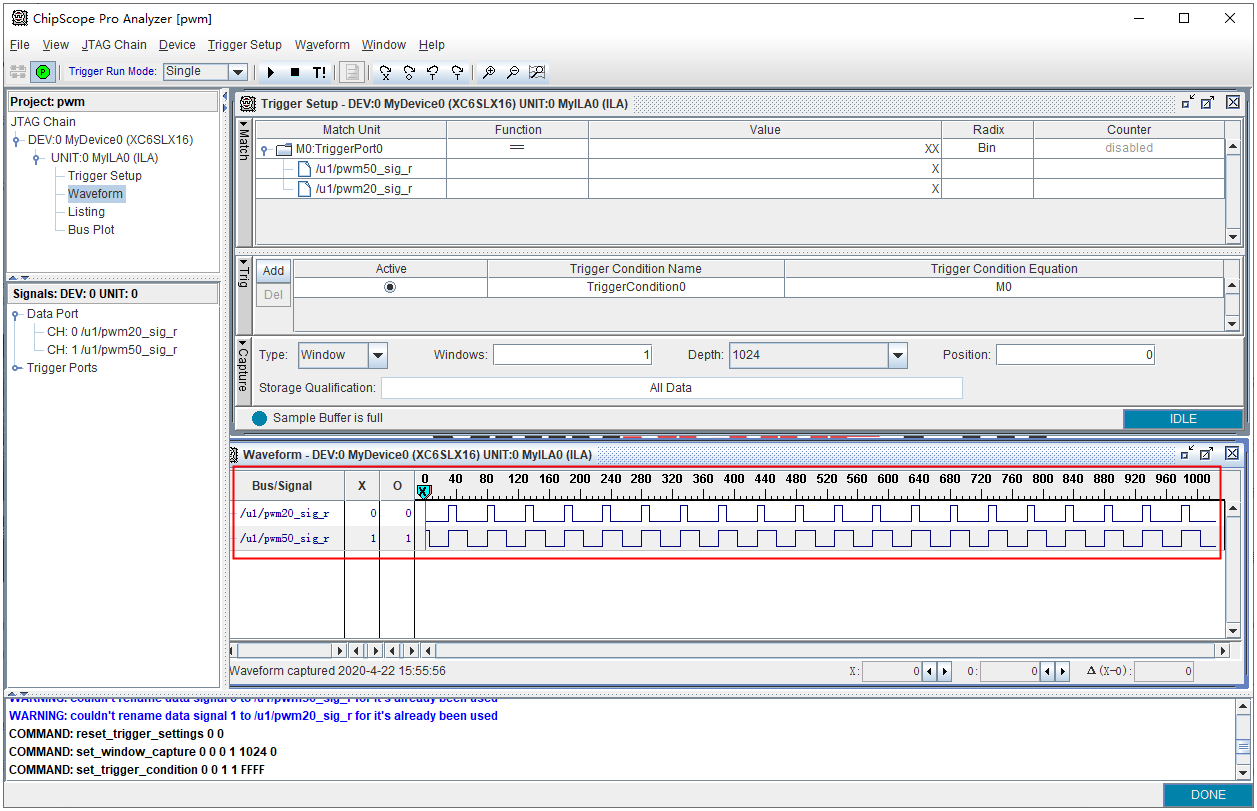

- 本实验原理是通过参考时钟进行计数,并在时钟计数器特定时刻进行高低电平的变换,来改变输出波形的频率和占空比。本实验中参考时钟为clk_25m,频率控制参数为cycle,占空比参数为puty_50和puty_20。频率为500KHz的波形计算方公式为:clk_25m/(cycle-1);

- 占空比为20%的参数计算公式为:puty_20/cycle;

- 占空比为50%的参数计算公式为:puty_50/cycle。

其代码如下:

always@(posedge clk_25m or negedge rst_n) begin if(!rst_n) begin cycle_cnt <= 8'd0; pwm20_sig_r <= 1'd0; pwm50_sig_r <= 1'd0; end else begin if(cycle_cnt==cycle-1'd1)//计数器清零,步两个信号相位 begin cycle_cnt <= 8'd0; pwm20_sig_r <= 1'd1; pwm50_sig_r <= 1'd1; end else if(cycle_cnt==puty_50-1'd1)//变换占空比为50% begin pwm50_sig_r <= 1'd0; cycle_cnt <= cycle_cnt + 8'd1; end else if(cycle_cnt==puty_20-1'd1)//变换占空比为20% begin pwm20_sig_r <= 1'd0; cycle_cnt <= cycle_cnt + 8'd1; end else//计数器自加 begin cycle_cnt <= cycle_cnt + 8'd1; end end end

五、实验步骤及实验结果

六、拓展实验

- 改变cycle和puty参数,观察信号变化。

icore4tx_fpga_10.txt · 最后更改: 2022/04/01 11:37 由 sean