| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-07-01 | gingko | 初次建立 |

实验四:Signaltap II实验——查看LED信号

一、 实验目的与意义

- 掌握QuartusII调试工具Signaltap II的使用方法。

- 掌握QuartusII的使用方法。

- 学习Verilog编程语言的基本语法及相关运算符。

二、 实验设备及平台

三、 实验原理

- 1、以一个三色LED灯交替闪烁程序为例,通过signaltap II工具查看LED信号的状态。使用户掌握signaltapII工具的基本使用方法。

- 2、实现三色LED交替闪烁的程序关键代码讲解如下:

表4-1

| led | 001 | 010 | 100 |

| ~led | 110 | 101 | |

| 三色LED状态 | 蓝灯亮 | 绿灯亮 | 红灯亮 |

reg [2:0]led; //定义一个3位寄存器型变量,led,用来控制三色led的状态 always @(posedge led_clk or negedge rst_n) if (!rst_n) begin led <= 3'd1; //复位后led=001,蓝灯亮 end else //以下代码实现led寄存器最高位为零时,使寄存器内容左移按 001-010-100-001 begin //也就实现了三色led灯按照蓝、绿、红顺序交替闪烁 if (led[2]) begin led <= 3'd1; end else begin led <= led << 1'd1; end end

四、 Signaltap使用方法

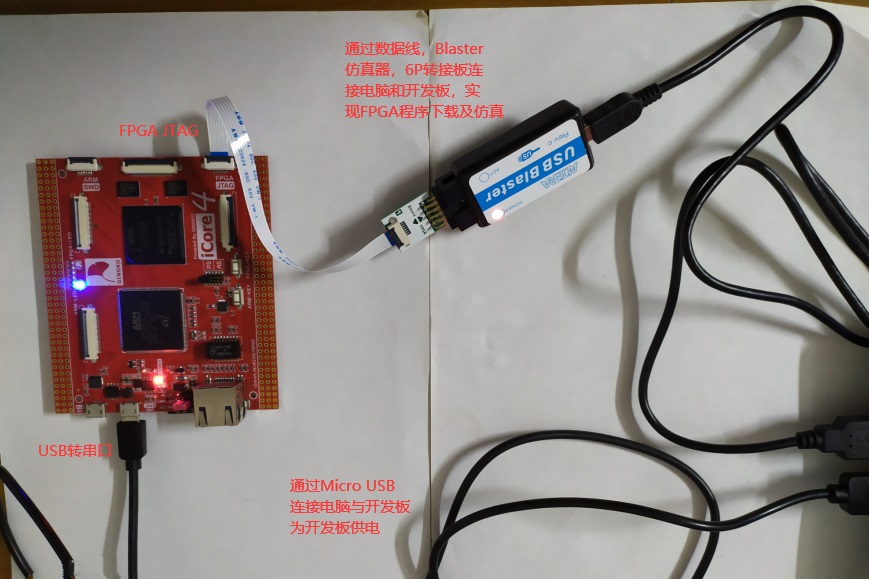

1、将硬件正确连接,如图4-1所示。

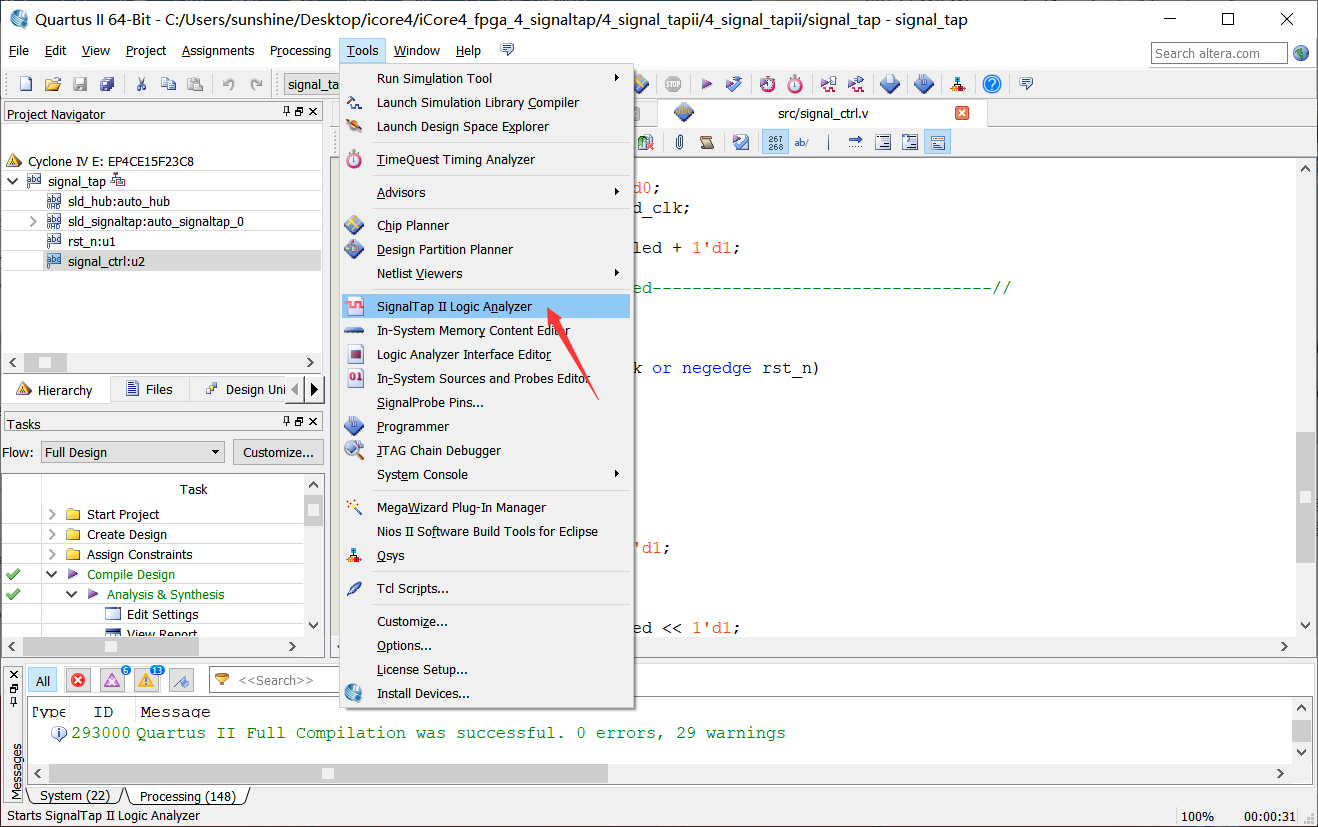

2、打开实验四例程中的QuartusII工程文件(已经完成了相关设置及引脚分配),进行重编译,然后打开Signaltap工具Tool→Signaltap II Logic Analyzer,如图4-2所示。

2、打开实验四例程中的QuartusII工程文件(已经完成了相关设置及引脚分配),进行重编译,然后打开Signaltap工具Tool→Signaltap II Logic Analyzer,如图4-2所示。

3、点击Setup添加仿真器设备,如图4-3所示。

3、点击Setup添加仿真器设备,如图4-3所示。

4、添加目标仿真文件(.sof),一般该文件存放在output file文件夹下,如图4-4所示。

4、添加目标仿真文件(.sof),一般该文件存放在output file文件夹下,如图4-4所示。

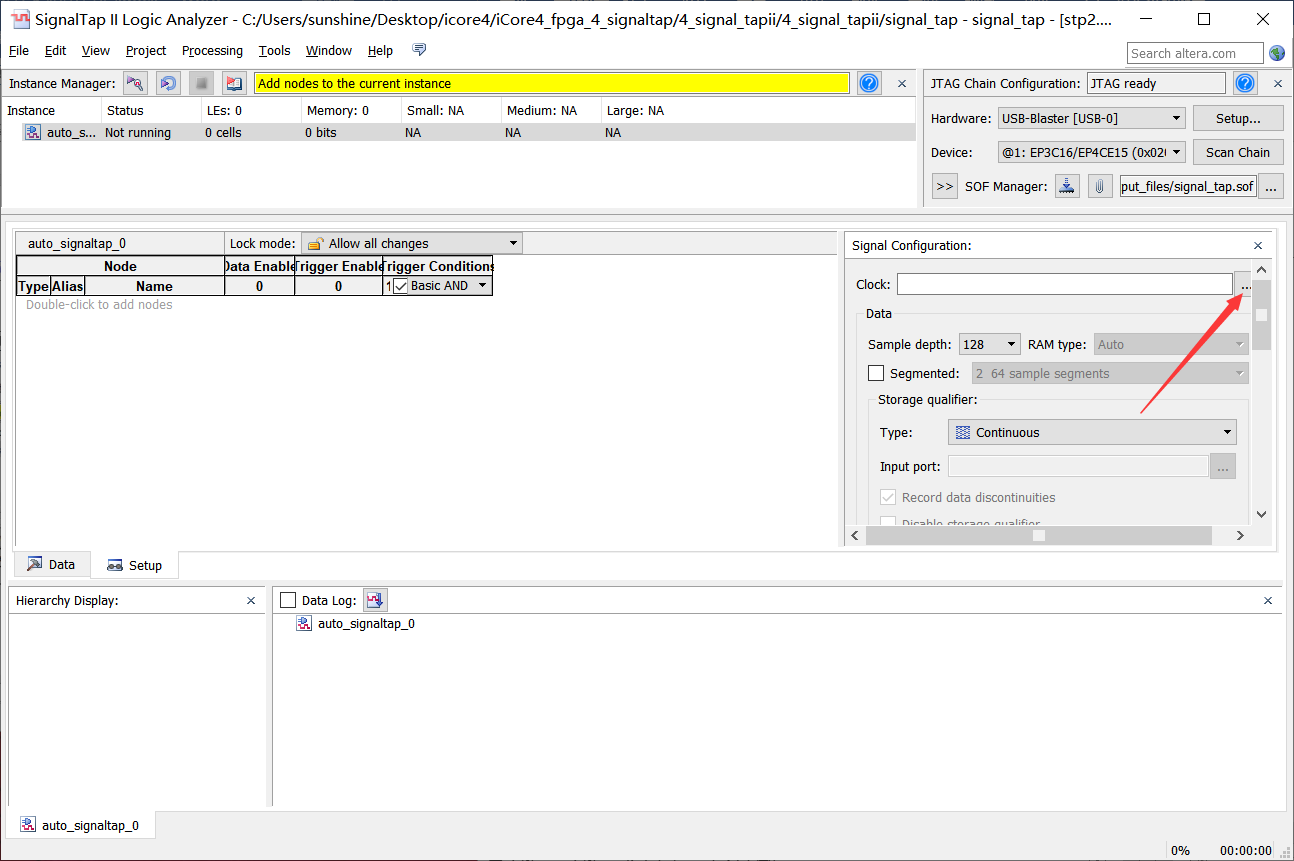

5、添加采样时钟,如图4-5所示。

5、添加采样时钟,如图4-5所示。

- 注意:一般采样时钟不能小于目标信号的2倍。

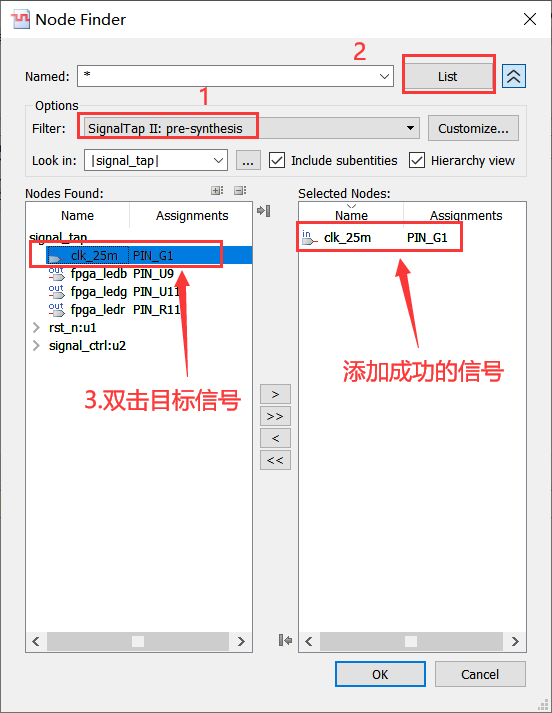

6、选择采样时钟信号,首先设定Filter为SinalTap II:pre-synthesis,然后点击List,在下面信号列表中选择所需的采样时钟信号,如图4-6所示。

6、选择采样时钟信号,首先设定Filter为SinalTap II:pre-synthesis,然后点击List,在下面信号列表中选择所需的采样时钟信号,如图4-6所示。

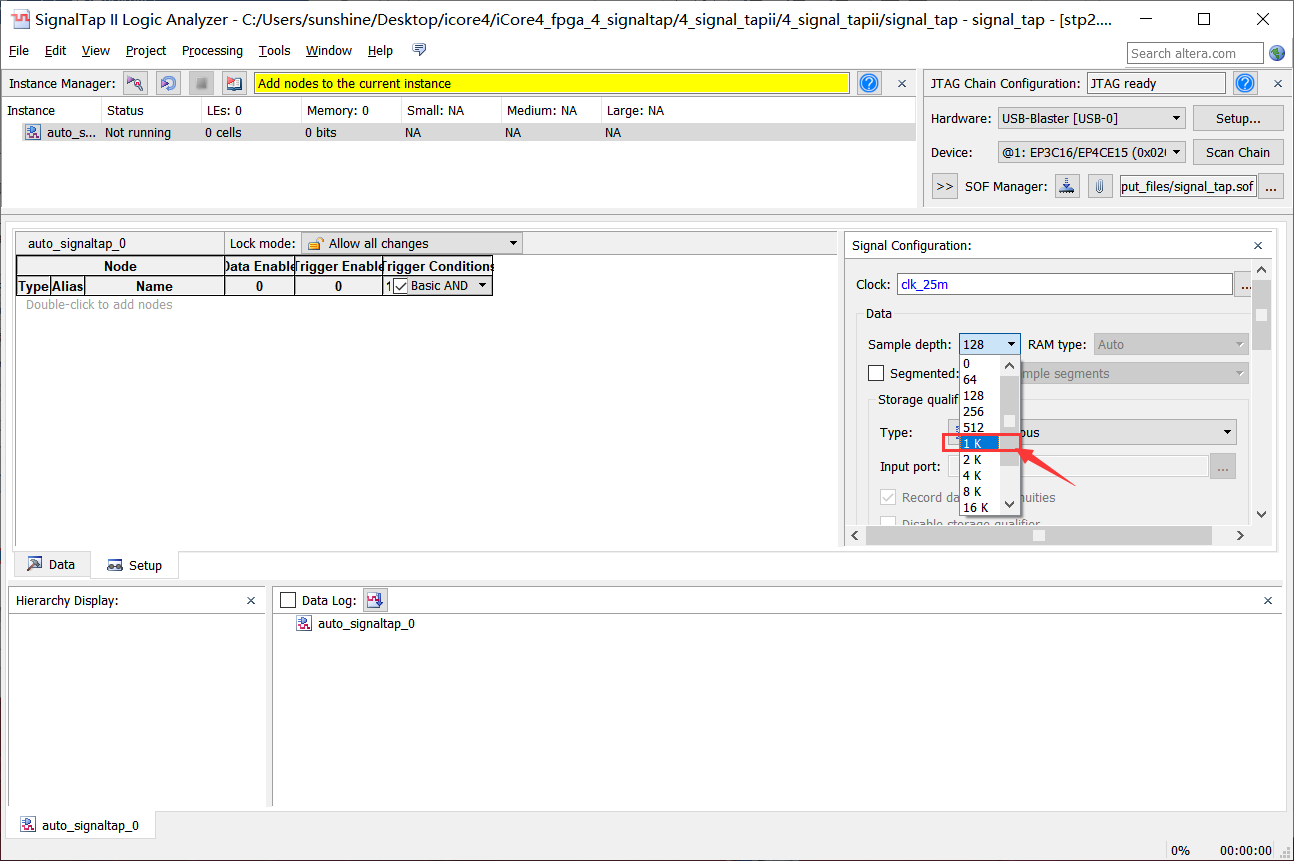

7、配置采样存储空间大小,根据芯片可利用存储空间和采样需要进行确定其大小,本实验选择1k采样存储空间,如图4-7所示。

7、配置采样存储空间大小,根据芯片可利用存储空间和采样需要进行确定其大小,本实验选择1k采样存储空间,如图4-7所示。

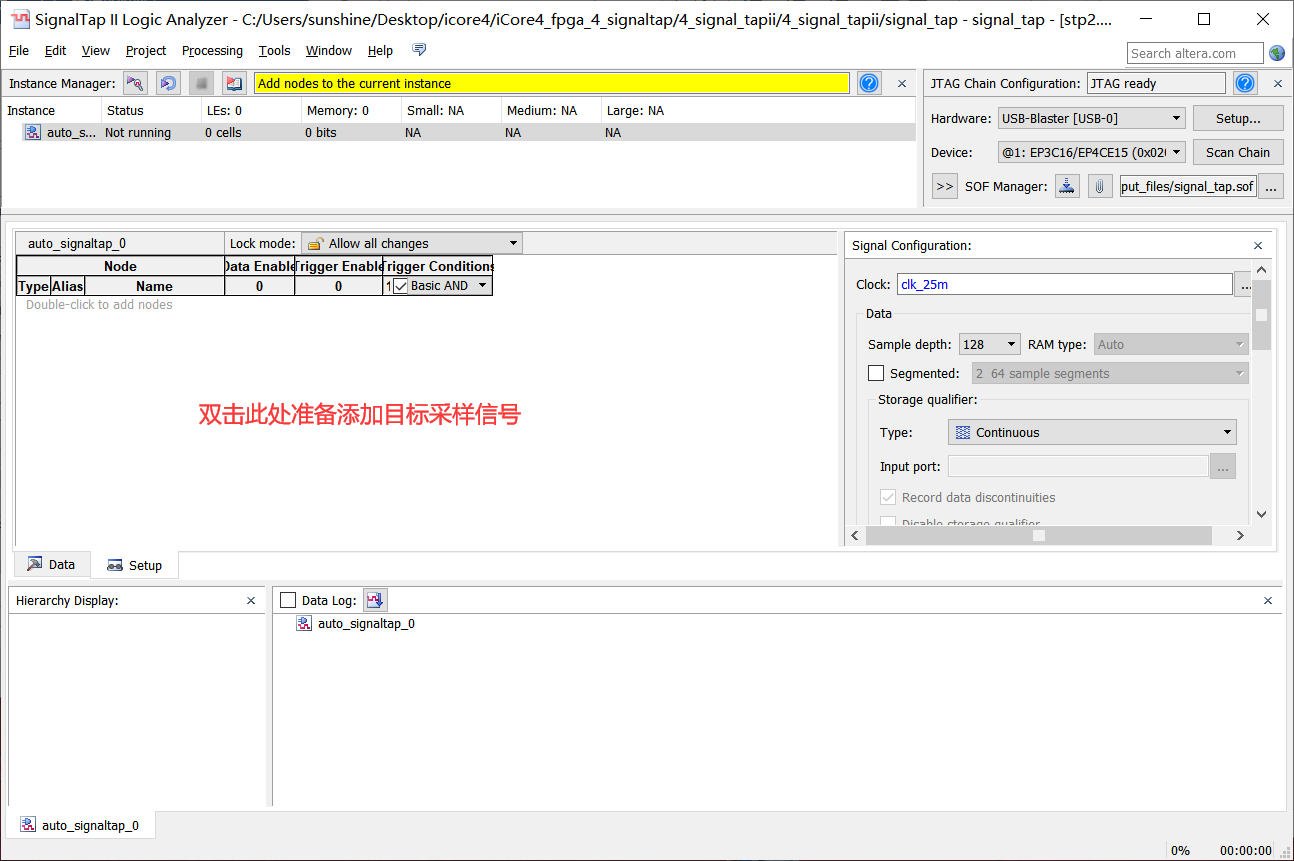

8、双击空白处,添加目标采集信号,如图4-8所示。

8、双击空白处,添加目标采集信号,如图4-8所示。

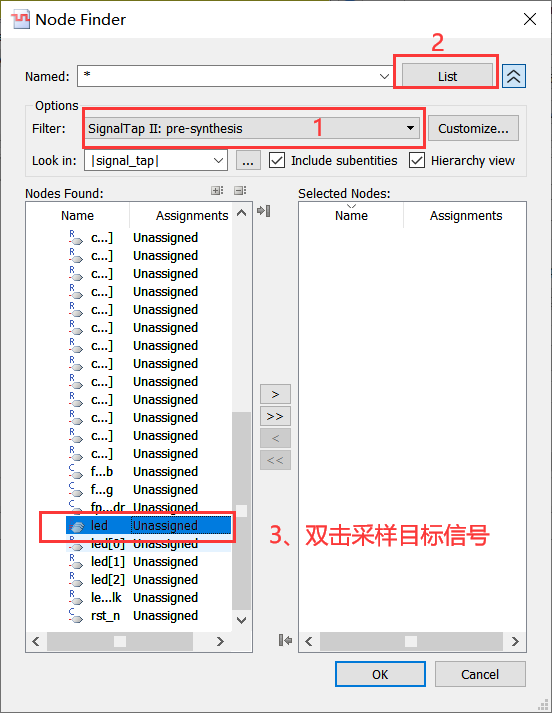

9、选择采样时钟信号,首先设定Filter为SinalTap II:pre-synthesis,然后点击List,在下面信号列表中目标采样信号,如图4-9所示。

9、选择采样时钟信号,首先设定Filter为SinalTap II:pre-synthesis,然后点击List,在下面信号列表中目标采样信号,如图4-9所示。

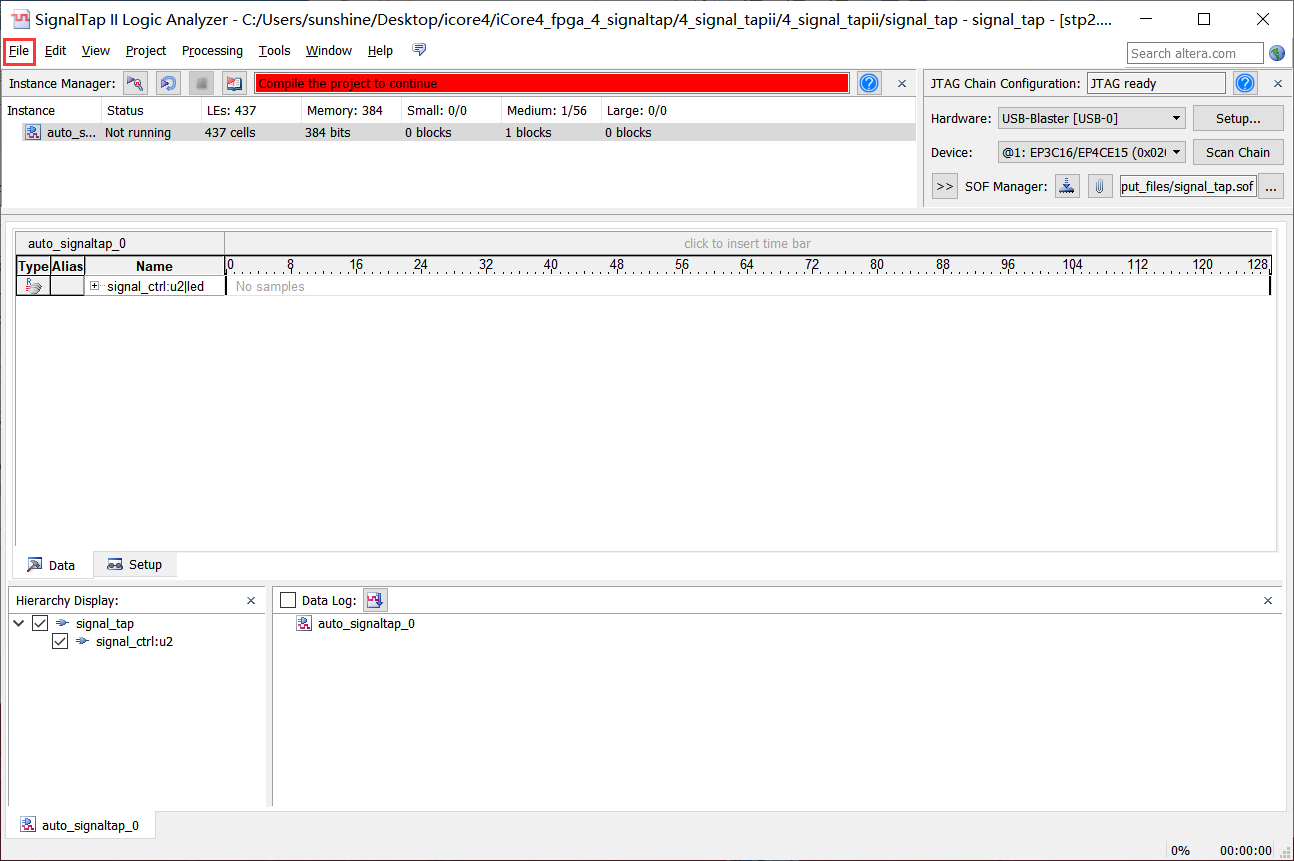

10、点击File→Save as将文件保存,如图4-10所示。

10、点击File→Save as将文件保存,如图4-10所示。

11、设置保存的文件名称(signaltap.stp),路径可以默认也可以自行设定,如图4-11所示。

11、设置保存的文件名称(signaltap.stp),路径可以默认也可以自行设定,如图4-11所示。

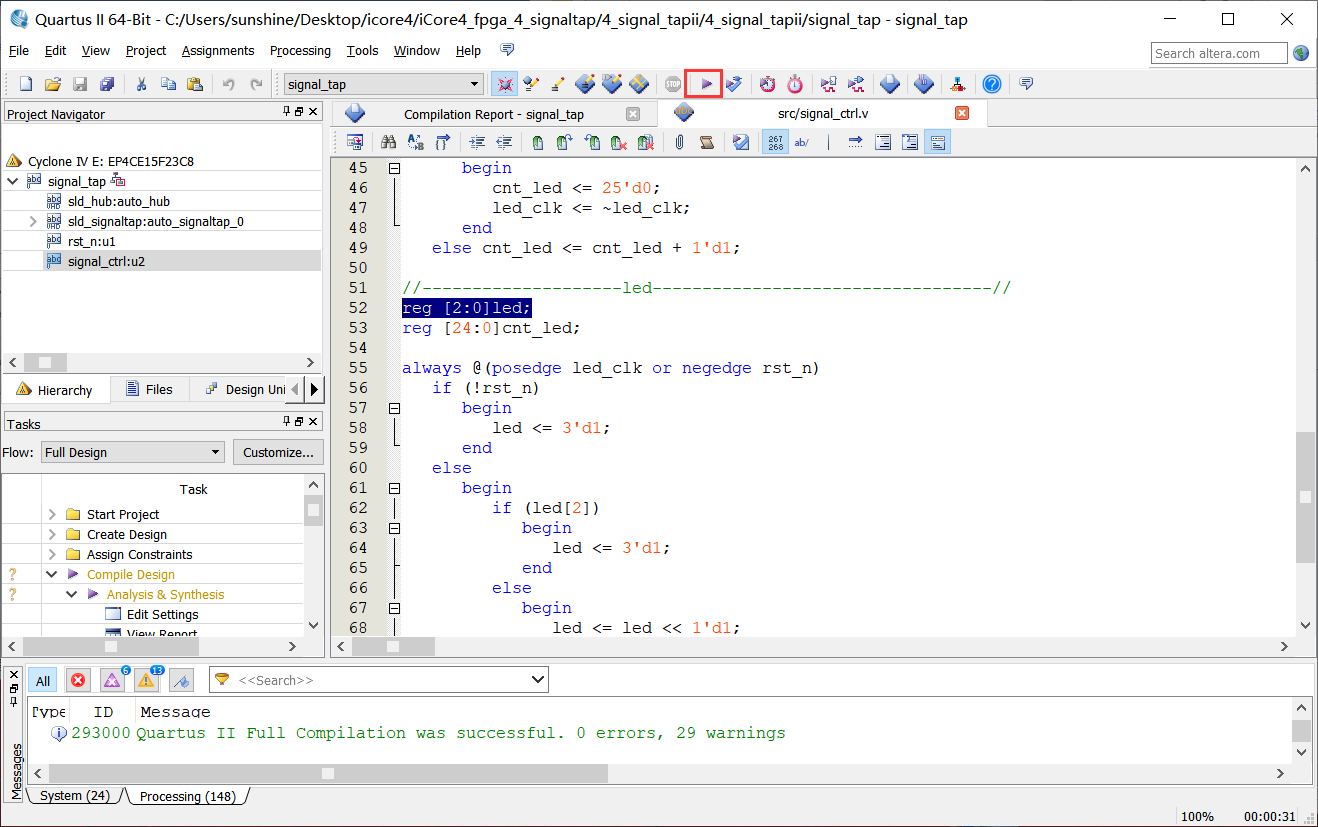

12、回到Quartus主界面,保存工程并重新编译,如图4-12所示。

12、回到Quartus主界面,保存工程并重新编译,如图4-12所示。

13、回到Signaltap界面点击下载按钮下载程序,如图4-13所示。

13、回到Signaltap界面点击下载按钮下载程序,如图4-13所示。

14、点击连续采样按钮进行采样,如图4-14。

14、点击连续采样按钮进行采样,如图4-14。

15、右键单击信号设置信号的显示方式为二进制显示,如图4-15所示。

15、右键单击信号设置信号的显示方式为二进制显示,如图4-15所示。

16、观察采集得到的信号:001b——010b——100b——001b,如图4-16,即对应实验原理部分。此时实验板上与FPGA相连的三色LED按照,蓝、绿、红的顺序交替闪烁。

16、观察采集得到的信号:001b——010b——100b——001b,如图4-16,即对应实验原理部分。此时实验板上与FPGA相连的三色LED按照,蓝、绿、红的顺序交替闪烁。

17、点击Setup对信号进行一些触发条件设置,在此处就不一一说明介绍,如图4-17所示。

17、点击Setup对信号进行一些触发条件设置,在此处就不一一说明介绍,如图4-17所示。

五、 拓展实验

- 操作单次采样按钮和停止按钮;

- 设定信号触发条件,观察采样现象变化。