| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-07-01 | gingko | 初次建立 |

实验一:GPIO输出实验——三色LED交替闪烁

一、 实验目的与意义

- 了解FPGA输出引脚功能。

- 了解三色LED的特征和应用领域。

- 掌握QuartusII集成开发环境使用方法。

- 掌握FPGA引脚配置方法。

二、 实验设备及平台

三、 实验原理

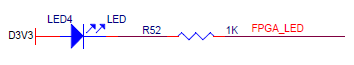

- 本实验根据led的驱动原理编写led控制程序, led的驱动原理是通过程序控制FPGA数字IO的电平变化实现led的亮灭。其硬件原理图如图1-1所示。

- 程序实现的功能为,icore4板上与FPGA芯片相连的三色LED灯快速交替闪烁。本程序程序实现原理为:通过硬件语言描述一个周期为0.2s的时间闸门信号,以该信号作为状态转移的触发信号来实现状态跳转,通过状态跳转实现不同led灯的亮灭。时间闸门信号由以下代码产生:

/*clk_25m上升沿或者rst_n下降沿到来执行always块内容*/ always @ (posedge clk_25m or negedge rst_n) if(!rst_n) //rst_n=0时执行if中内容 begin cnt <= 25'd0; //cnt赋值为0 led_cnt <= 1'd0; // led_cnt赋值为0 end else if(cnt == 25'd5000000) //当cnt=5000000时执行else if中内容 begin cnt <= 25'd0; //cnt赋值为0 if(led_cnt == 3'd2) //当led_cnt=2时执行if中内容 led_cnt <= 3'd0; //led_cnt赋值为0 else led_cnt <= led_cnt + 1'd1; //led_cnt自加1 end else begin cnt <= cnt + 1'd1; //cnt自加1 end

四、 新建工程

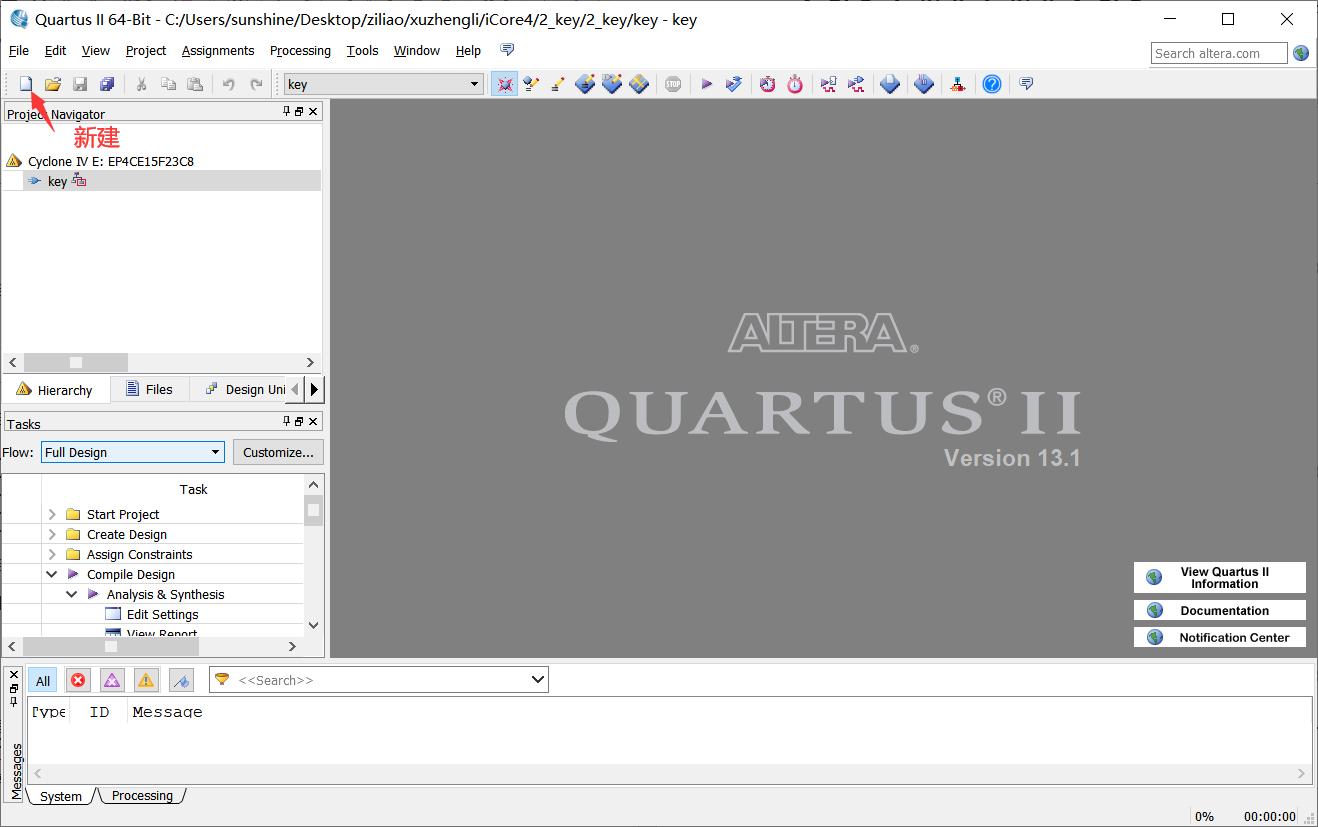

1、双击Quartus桌面图标打开软件,出现下面界面,如图1-2所示。

2、点击新建图标出现下面对话框,选择New Quartus II Project选项,如图1-3所示。

2、点击新建图标出现下面对话框,选择New Quartus II Project选项,如图1-3所示。

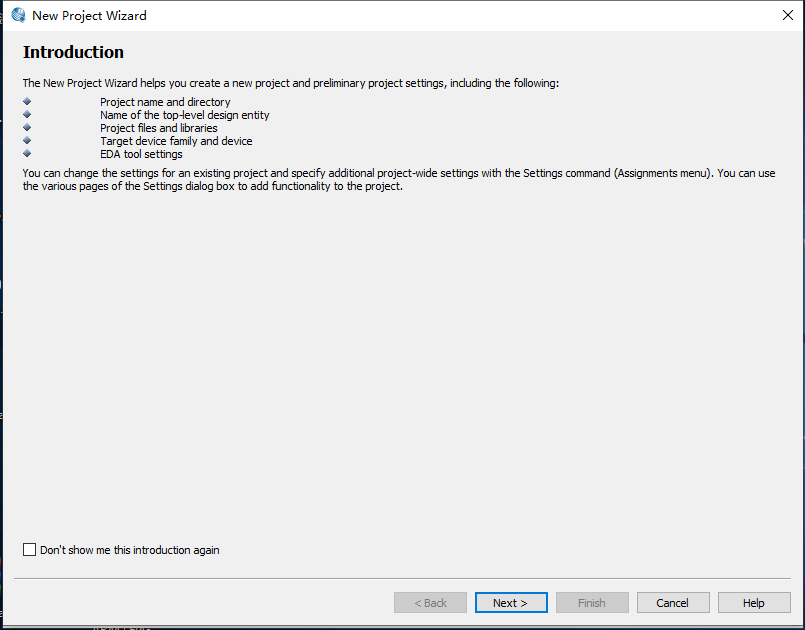

3、直接点击Next,如图1-4所示。

3、直接点击Next,如图1-4所示。

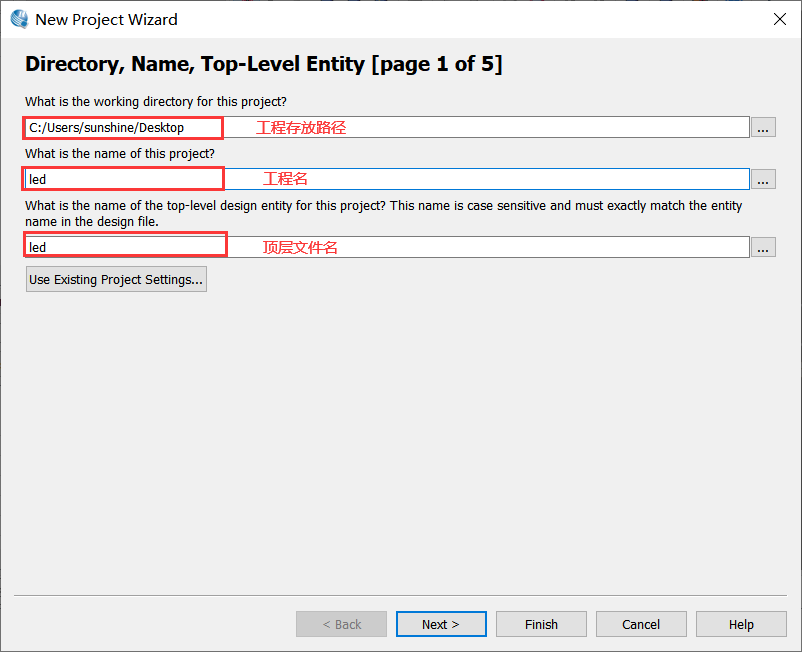

4、在此界面选择工程存放的路径,设置工程名及顶层文件名称,如图1-5所示。

4、在此界面选择工程存放的路径,设置工程名及顶层文件名称,如图1-5所示。

5、此界面主要用来添加已经编辑好的模块文件,若没有直接下一步即可,如图1-6所示。

5、此界面主要用来添加已经编辑好的模块文件,若没有直接下一步即可,如图1-6所示。

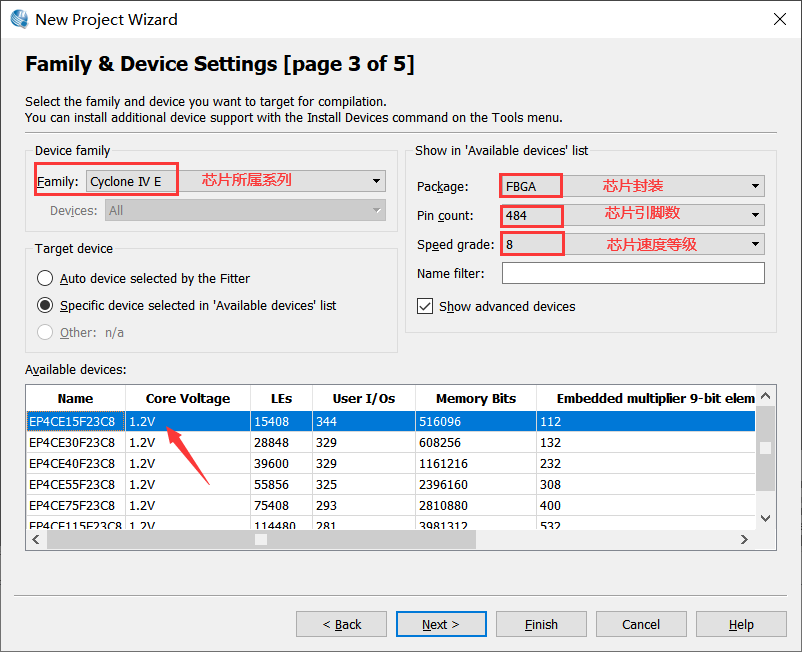

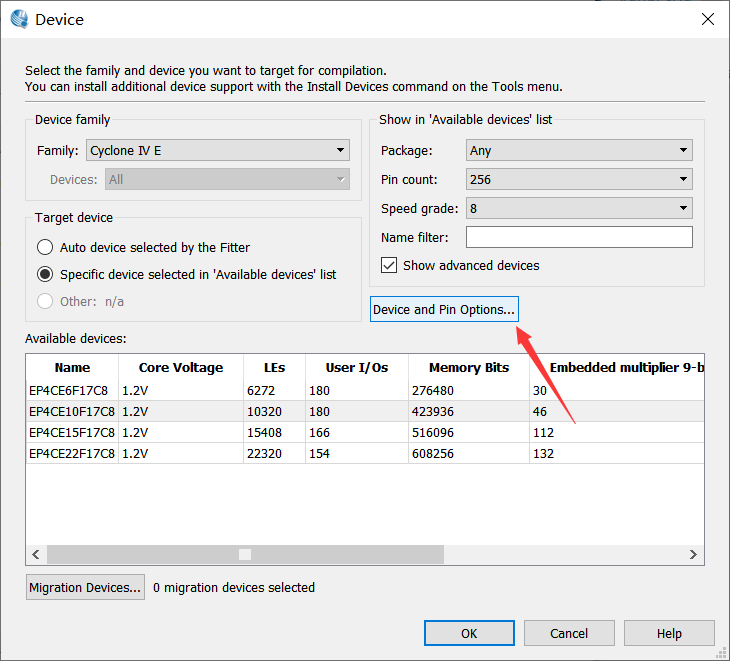

6、选择设备所用的芯片型号,芯片的系列、封装、引脚数、速度等级的选项方便用户更快速精确的找到目标芯片的型号,如图1-7所示。

6、选择设备所用的芯片型号,芯片的系列、封装、引脚数、速度等级的选项方便用户更快速精确的找到目标芯片的型号,如图1-7所示。

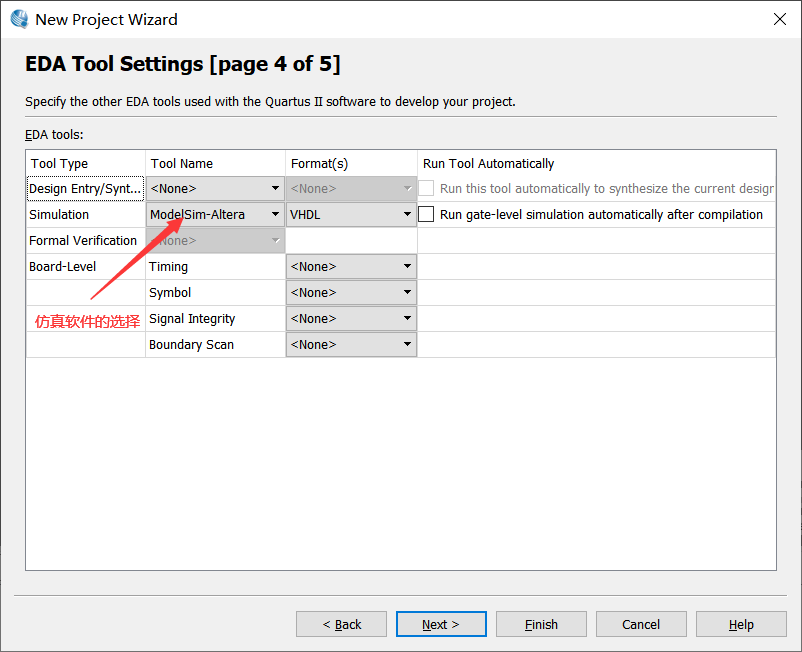

7、进行仿真器的一些设置,可忽略,如图1-8所示。

7、进行仿真器的一些设置,可忽略,如图1-8所示。

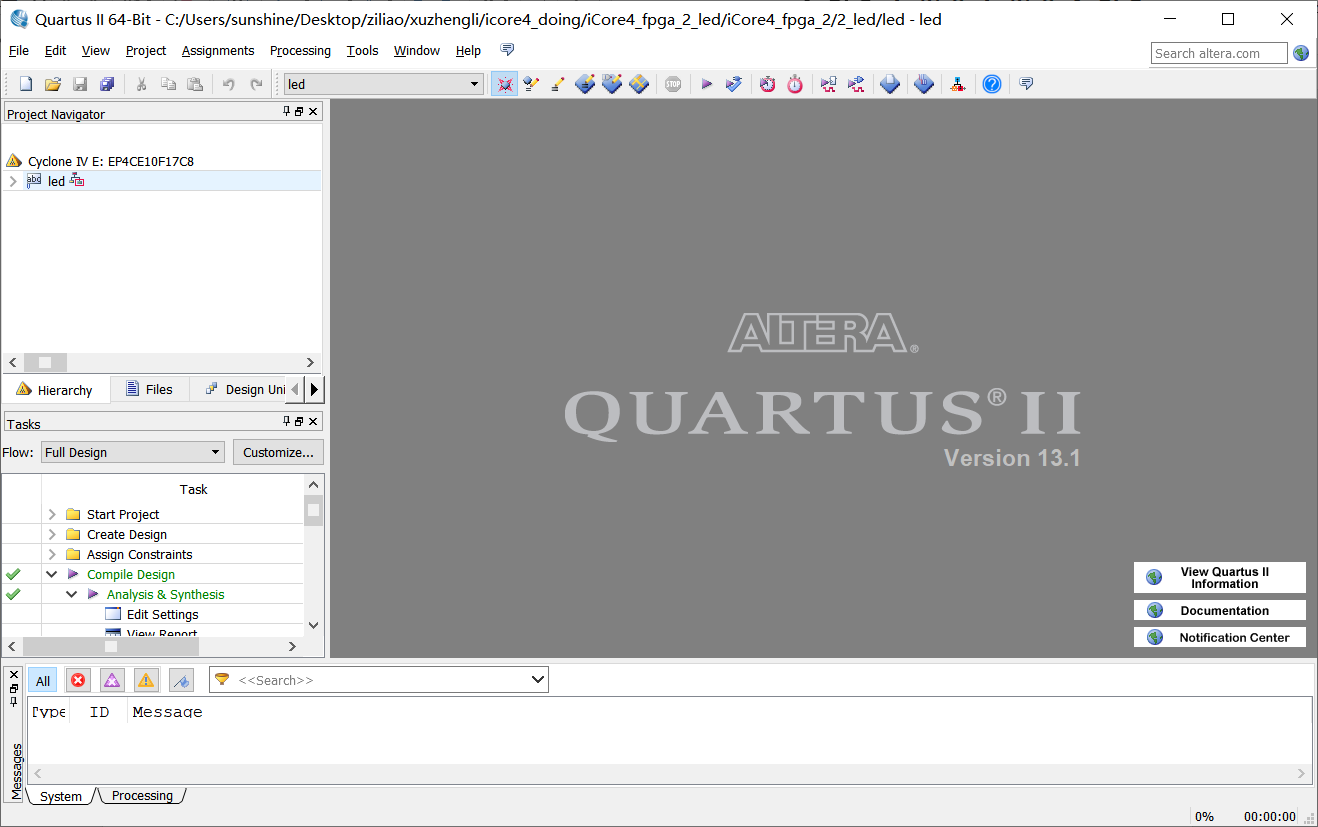

8、至此,工程建立完成,如图1-9所示。

8、至此,工程建立完成,如图1-9所示。

9、回到软件主界面可以看到新建的工程已经显示在左边列表中,如图1-10所示。

9、回到软件主界面可以看到新建的工程已经显示在左边列表中,如图1-10所示。

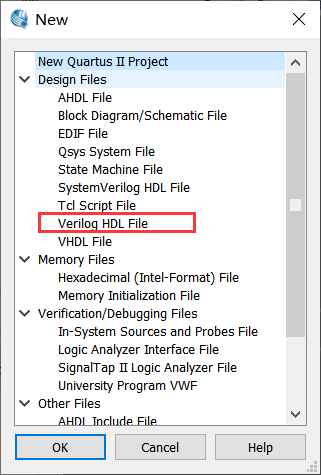

10、重新点击新建图标进入下面界面选择将要编译的文件类型,此处选择Verilog HDL硬件语言描述类型,如图1-11所示。

10、重新点击新建图标进入下面界面选择将要编译的文件类型,此处选择Verilog HDL硬件语言描述类型,如图1-11所示。

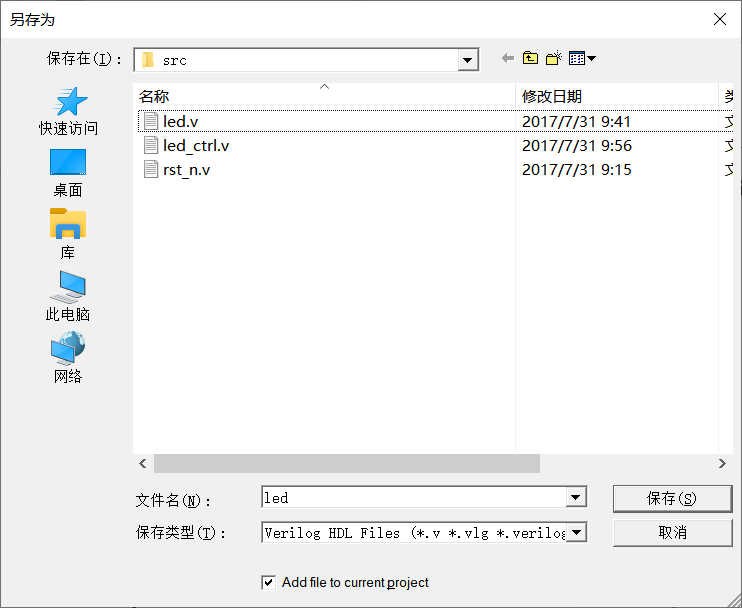

11、一个新的文件就建好了,此时文件时空的,点击file→save as保存文件。常将源文件保存在src文件夹下,且文件名称必须与模块名称一致,如图1-12所示。

11、一个新的文件就建好了,此时文件时空的,点击file→save as保存文件。常将源文件保存在src文件夹下,且文件名称必须与模块名称一致,如图1-12所示。

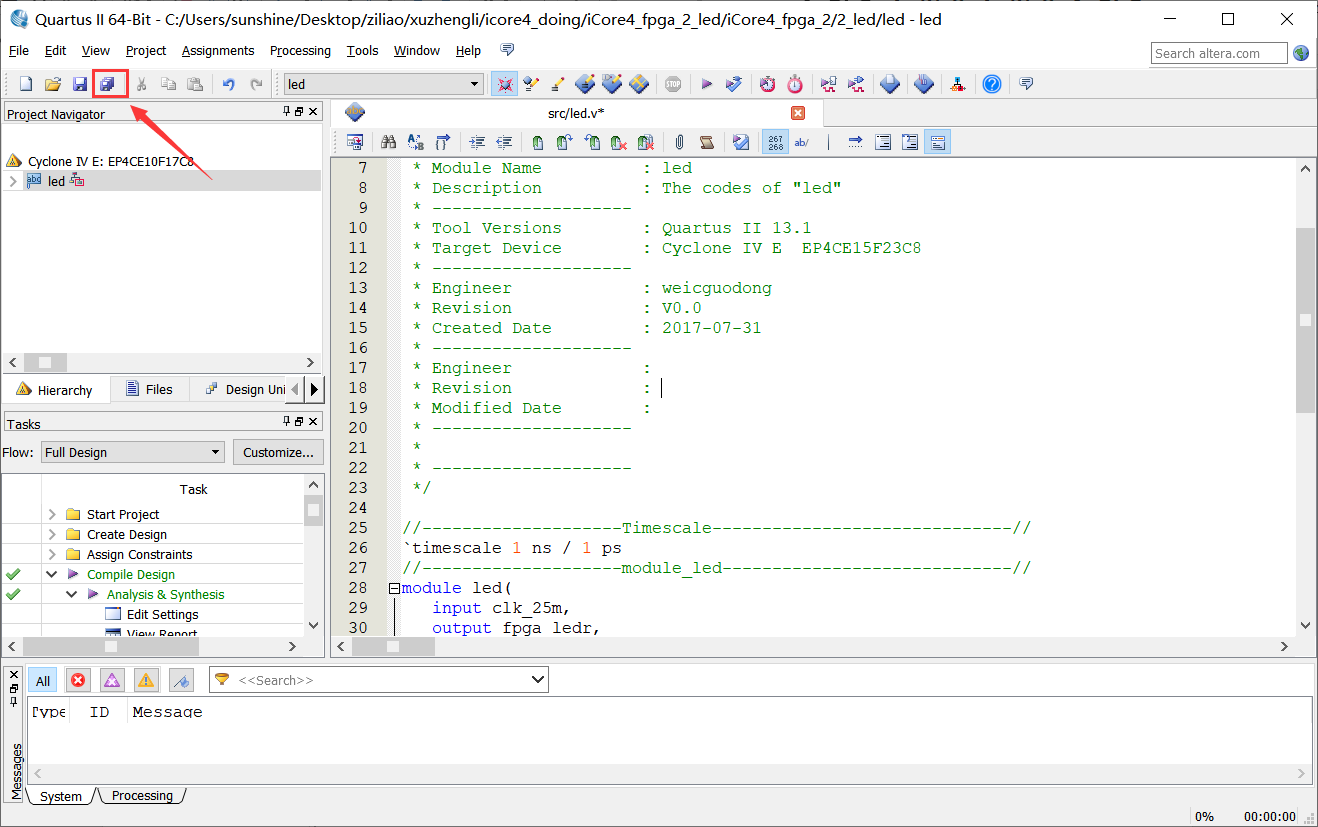

12、此时就可以写代码了,写好以后点击方框处的全部保存,如图1-13。

12、此时就可以写代码了,写好以后点击方框处的全部保存,如图1-13。

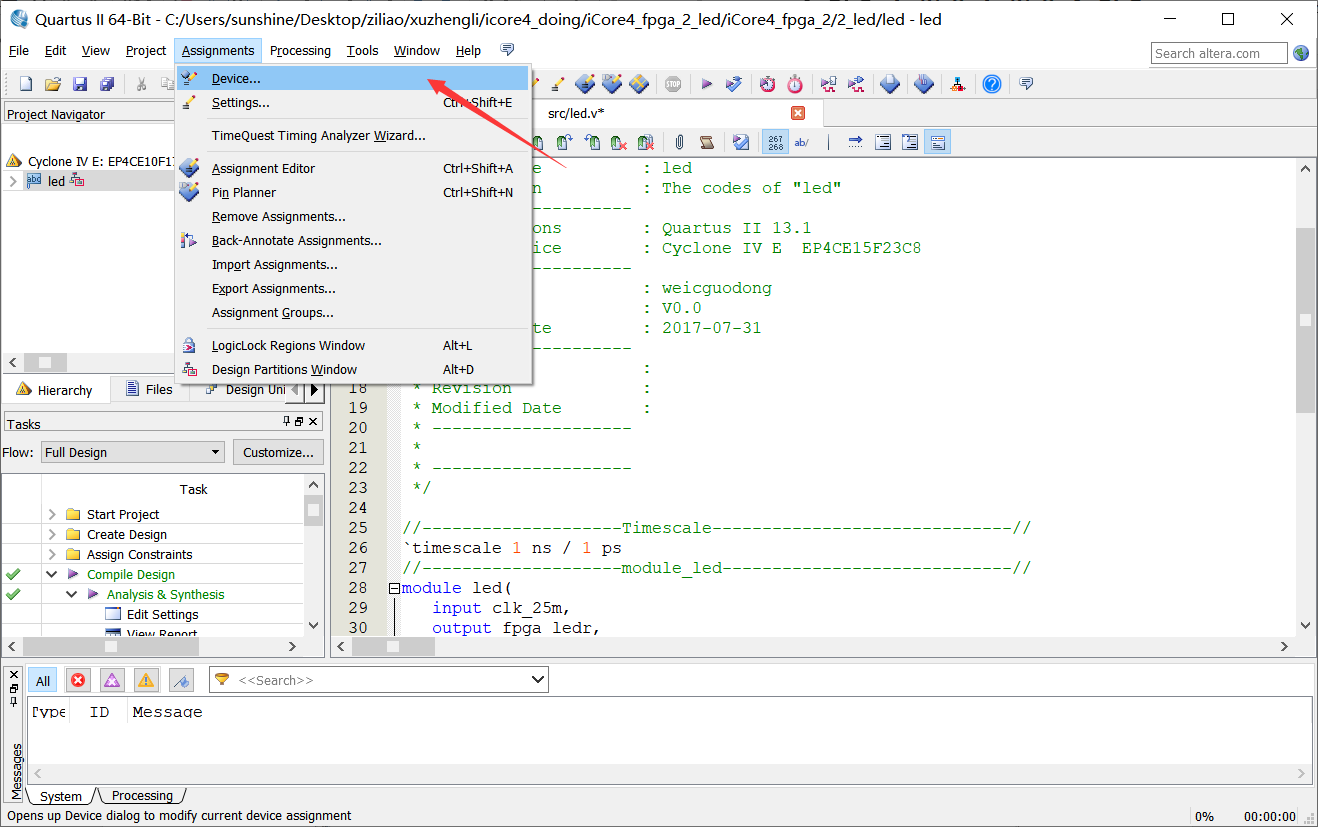

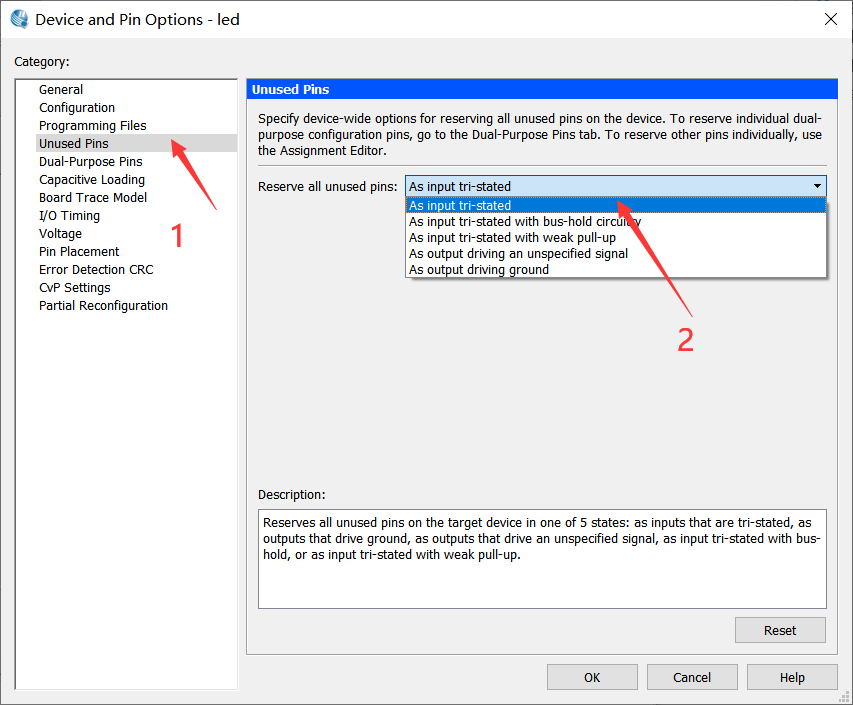

13、点击assignments→device,出现下边窗口,再点击方框处的“devices and pin options”,在弹出的窗口左栏中选择箭头1所示的“unused pins”,在相应的右边栏红框处的下拉菜单中选择“as input ti-stated”。

13、点击assignments→device,出现下边窗口,再点击方框处的“devices and pin options”,在弹出的窗口左栏中选择箭头1所示的“unused pins”,在相应的右边栏红框处的下拉菜单中选择“as input ti-stated”。

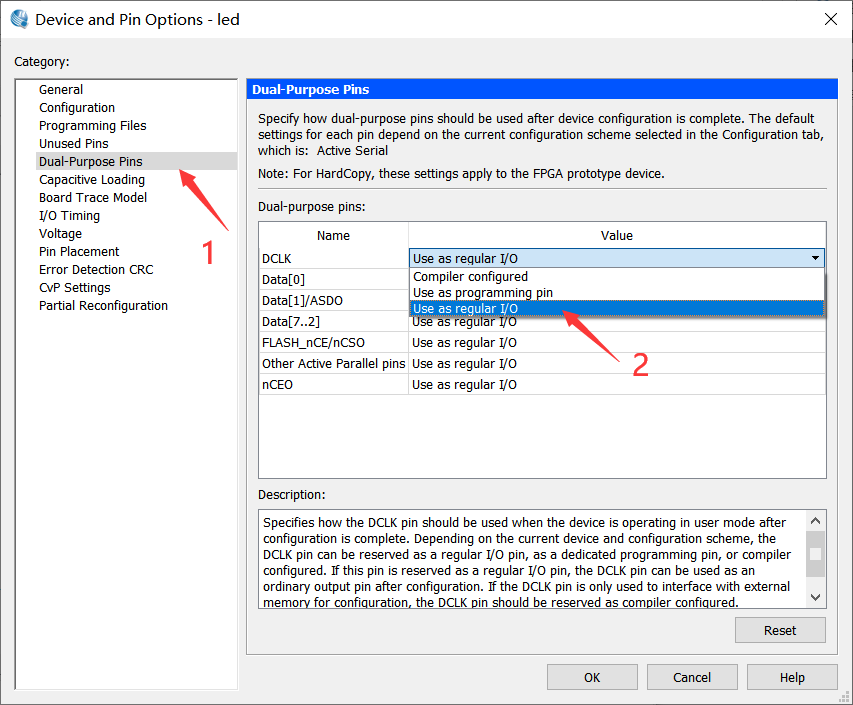

14、然后在左边栏中选择”Dual-purpose pins”,在相应的右边栏中双击图示位置会出现下拉菜单,选择”use as regular I/O”。

14、然后在左边栏中选择”Dual-purpose pins”,在相应的右边栏中双击图示位置会出现下拉菜单,选择”use as regular I/O”。

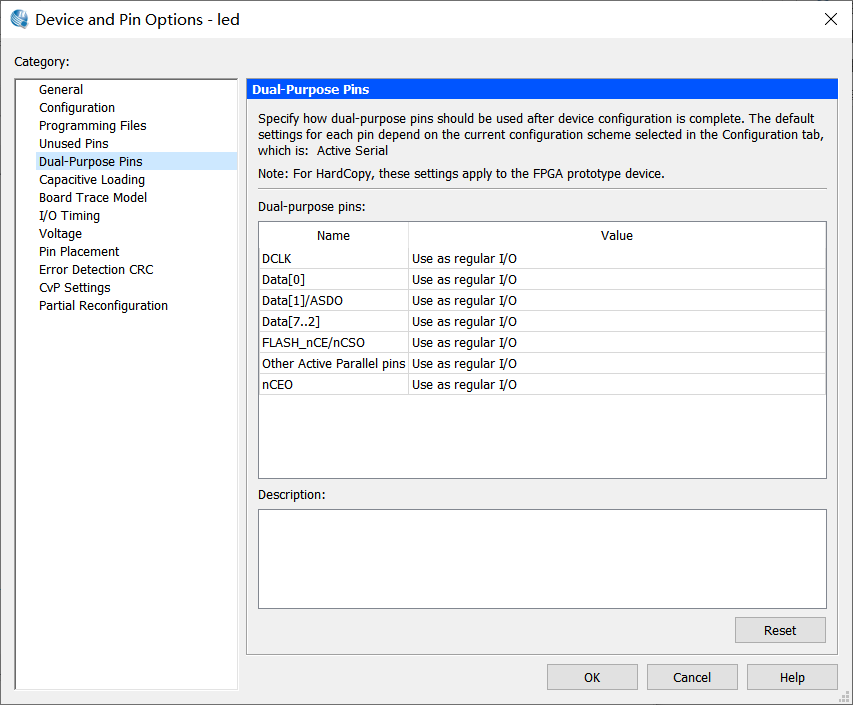

15、这是选择好的界面,点击OK即可。

15、这是选择好的界面,点击OK即可。

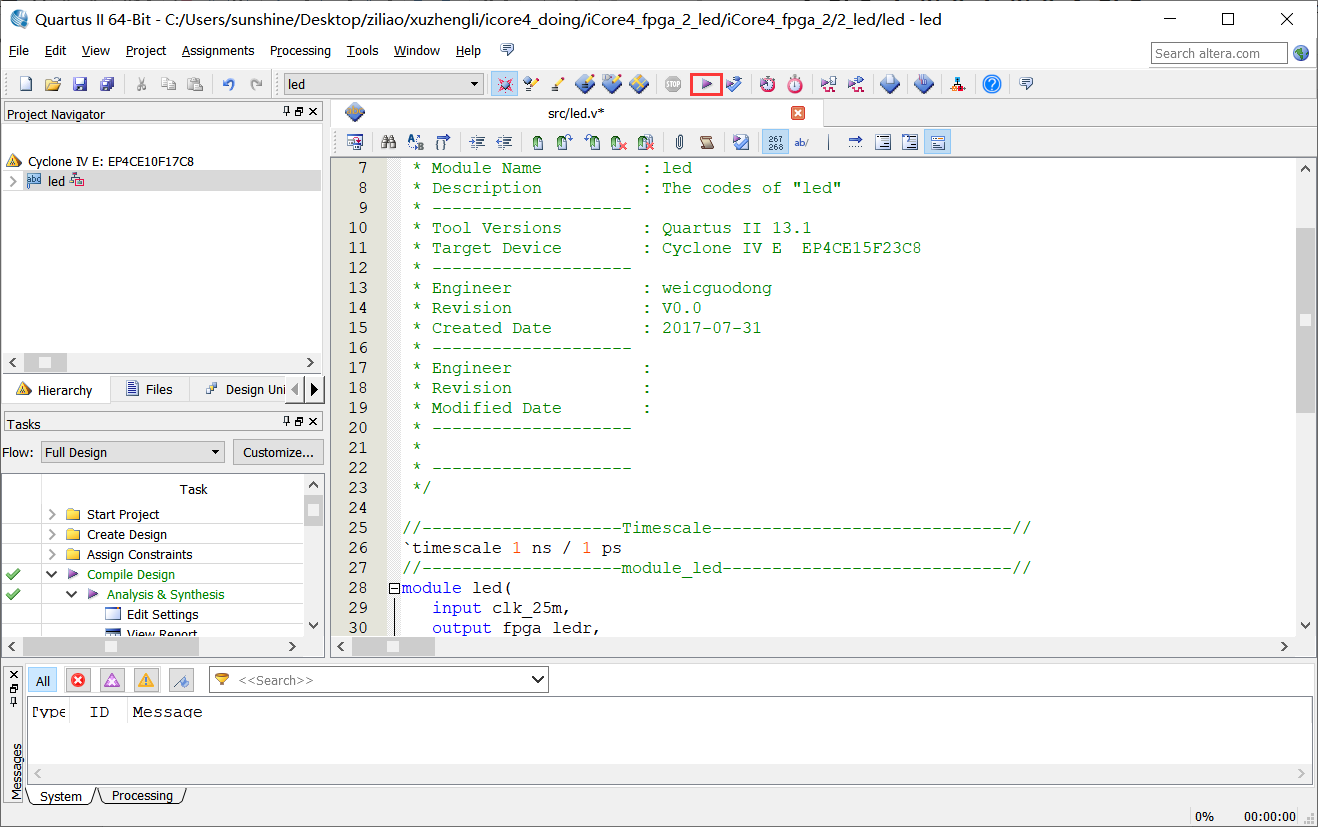

16、点击图示方框中的按钮进行编译。

16、点击图示方框中的按钮进行编译。

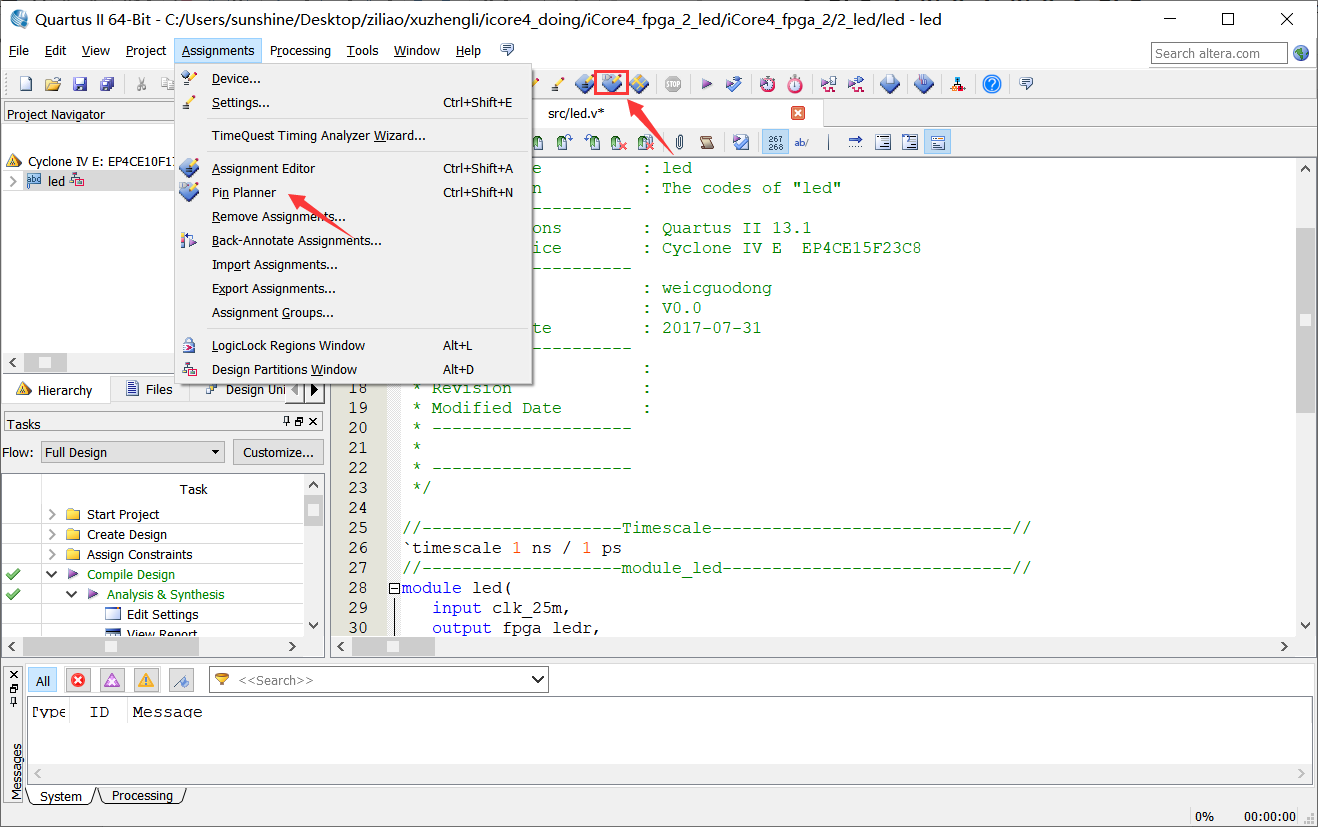

17.编译完成后,点击Assignment→pin planner或直接点击图1-20方框中的按钮,进行引脚分配。

17.编译完成后,点击Assignment→pin planner或直接点击图1-20方框中的按钮,进行引脚分配。

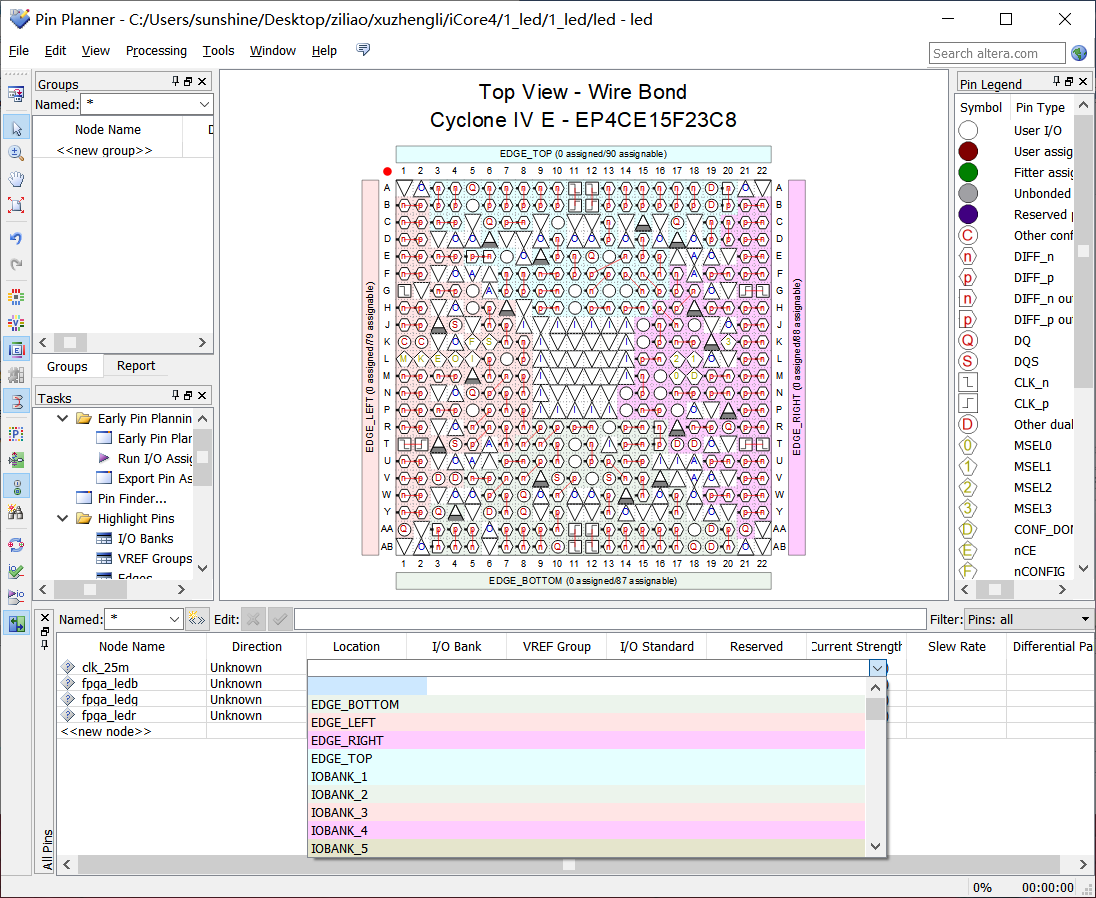

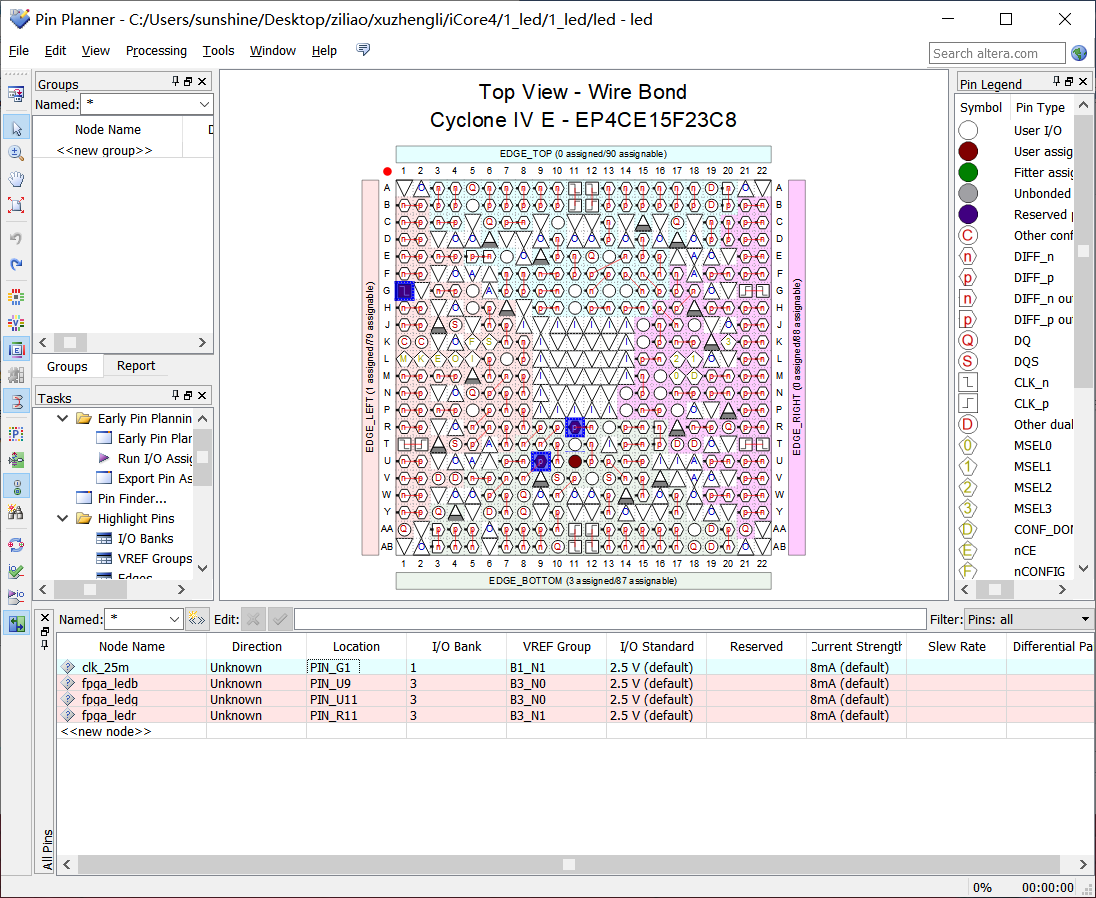

18、在引脚分配窗口下方的列表中显示工程的输入输出引脚,双击location栏下(箭头指示的位置)会出现下拉菜单,根据自己的硬件连接,选择正确的引脚,完成之后关闭窗口即可。

18、在引脚分配窗口下方的列表中显示工程的输入输出引脚,双击location栏下(箭头指示的位置)会出现下拉菜单,根据自己的硬件连接,选择正确的引脚,完成之后关闭窗口即可。

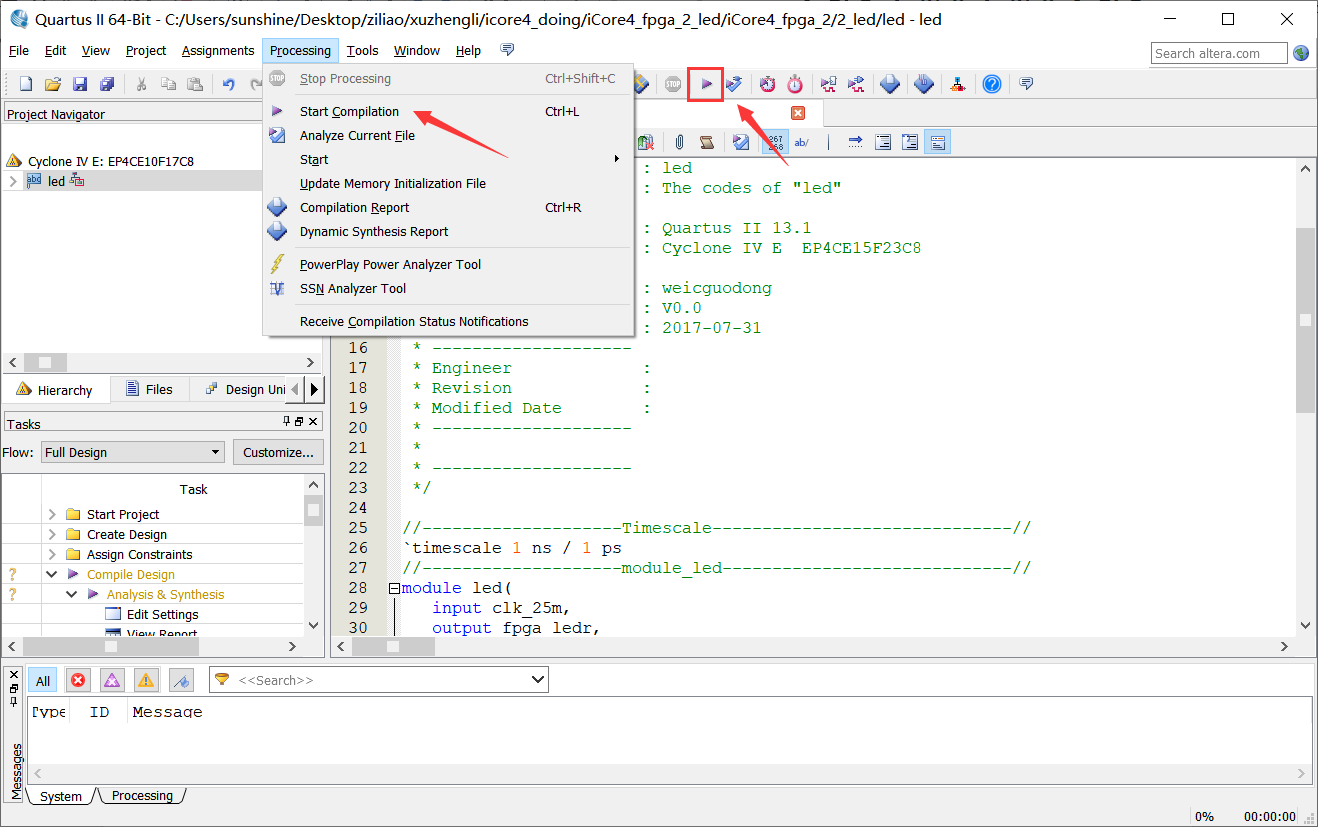

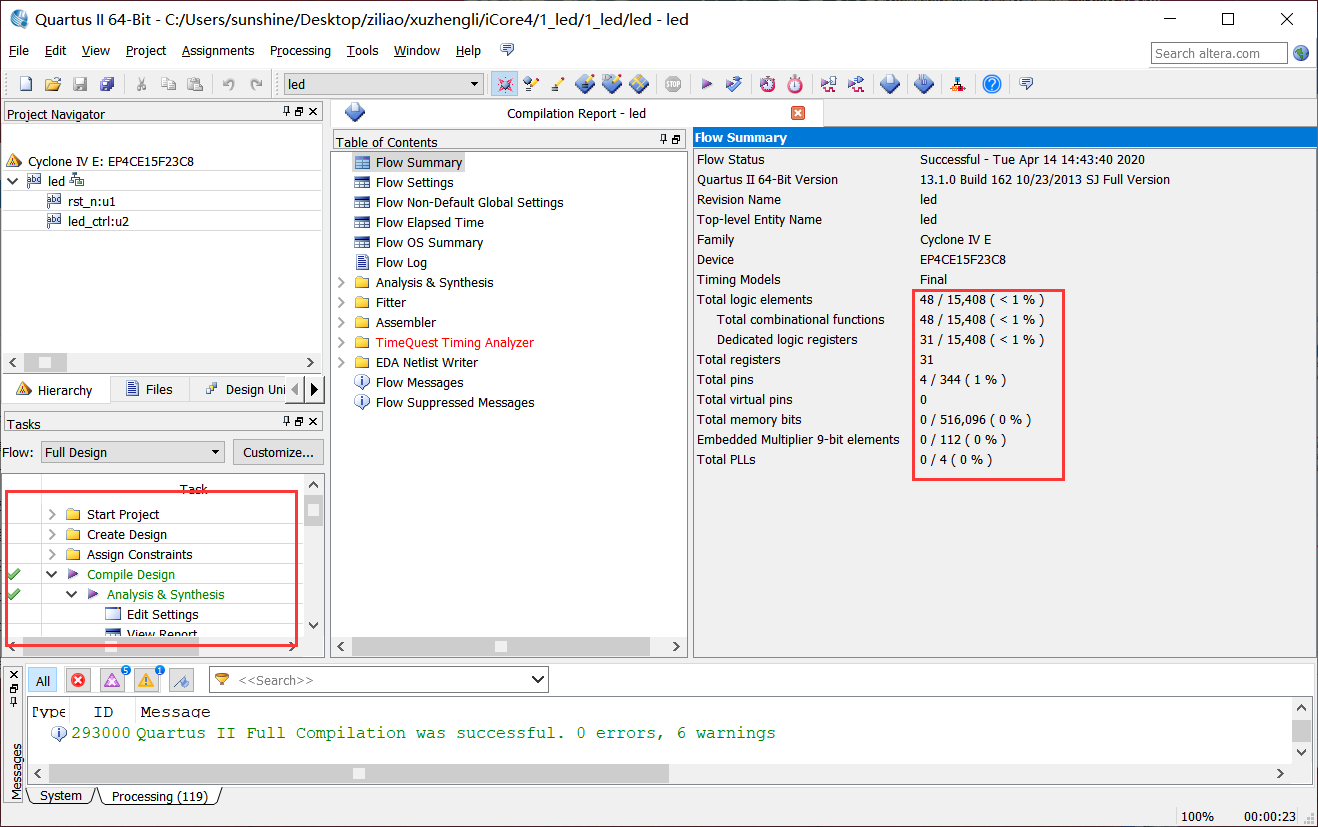

19、接下来再次编译程序,点击processing→start compilation或者直接点击图1-24小方框中的图标。可以在图1-25左侧看到编译进度,图示是编译完成的状态,右侧方框处是生成的报告(工程占用的资源数及引脚数等信息)。

19、接下来再次编译程序,点击processing→start compilation或者直接点击图1-24小方框中的图标。可以在图1-25左侧看到编译进度,图示是编译完成的状态,右侧方框处是生成的报告(工程占用的资源数及引脚数等信息)。

20、按照上一实验中介绍的配置文件下载教程将配置文件下载至硬件,观察实验现象。

20、按照上一实验中介绍的配置文件下载教程将配置文件下载至硬件,观察实验现象。

五、 实验现象

- iCore4双核心板上与FPGA相连的三色LED(PCB上标示为FPGA-LED),红色、绿色、蓝色,快速交替闪烁。