icore3_fpga_13

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-1-21 | gingko | 初次建立 |

实验十三:基于ARM+FPGA的FSMC复用模式通信

一、实验目的与意义

- 了解FSMC的复用模式及时序

- 掌握ARM和FPGA基于FSMC复用模式的通信设计方法

二、实验设备及平台

三、实验原理

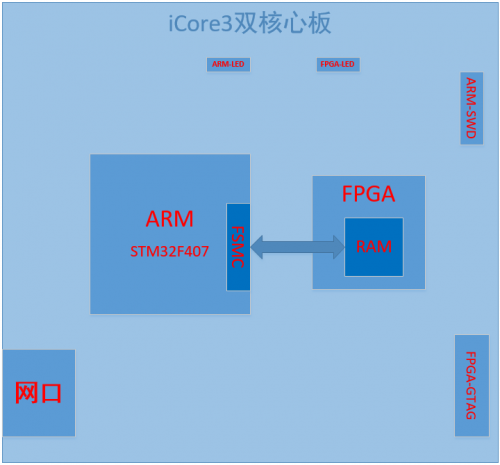

- 本实验要实现的目的是将ARM的FSMC外设连接到FPGA,并实现数据的传输。那么具体实验内容可以设计为将STM32F407连接到FPGA,并通过FSMC外设实现向FPGA发送和接受数据。FPGA并没有FSMC外设,要实现和STM32之间的通信,则必须对FSMC信号进行处理。本实验为了验证ARM和FPGA之间的数据传输是否正确,在STM32程序中自动生成数据,通过FSMC向FPGA写数据并读回进行对比判断。两组数据相同,说明通信正常,点亮绿色LED;不同,则说明通信异常,点亮红色LED。而FPGA除了对FSMC的信号进行处理,用于接收数据之外,还例化了RAM,用于缓存ARM发送的数据。

- 所以整体思路是ARM将FPGA内的RAM当成外挂存储器,通过FSMC向RAM中写入自动生成的数据,并读回进行对比,从而验证ARM和FPGA之间基于FSMC的通信。系统框架如下图所示:

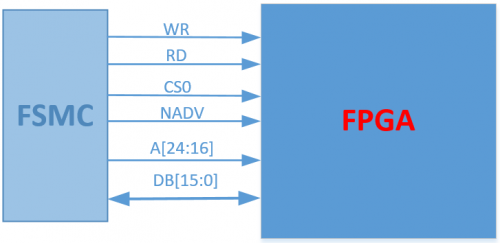

- 这里主要讲一下FPGA对FSMC信号的处理。下图是FPGA和ARM之间的FSMC信号连接。

- WR和RD分别是写使能信号和读使能信号。

- CS0表示片选,低电平有效。

- NADV是地址有效信号,复用模式下区分DB线上传输的是否为地址数据。

- A[24:16]表示存储器地址数据。

- DB[15:0]双向传输IO口,即可双向传输数据,也可复用为地址线的低16位。

FSMC的复用模式

- 从图中可以看出,地址线只用了A[24:16]。ARM通过FSMC发送地址数据的时候,将数据线DB[15:0]和A[24:16] 同时作为了地址线。因为DB[15:0]既做为地址线,又作为数据线,为了区分DB[15:0]传输的是数据还是地址,使用了NADV信号。当NADV信号为低时,表示DB[15:0]被复用为地址线了,这就是FSMC的复用模式。

四、代码讲解

- 整个系统是ARM通过FSMC写和读FPGA内部RAM存储器中的数值。那么,要实现对FPGA内部RAM写和读的功能,FPGA需要要对FSMC信号进行接收和解析,并且要判断出FSMC传输的读写使能信号,并为RAM提供时钟信号。

- 首先是提取读写使能信号,代码如下:

//-------------------------rd_wr ----------------------------// assign rd = (csn | rdn); assign wr = (csn | wrn);

- 其次则是根据FSMC时序,在nadv信号有效时期,接收向存储器RAM中写数据的地址信号。因为本例程采用的是FSMC复用模式,因此,address是由数据线和地址线上的信号拼接而成的。代码如下:

//-------------------------ab ------------------------------// reg [24:0]address; always @ (posedge nadv or negedge RST_n) begin if(!RST_n) begin address <= 25'd0; end else begin address <= {ab,db}; end end

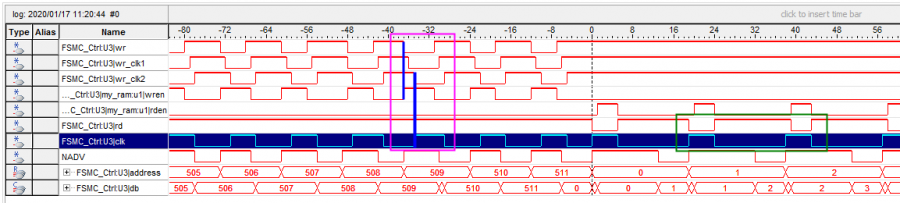

- 下面这段代码中,先是对wr信号做了100MHz时钟延两拍处理,然后取反,结合(!rd)信号控制clk。wr信号延两拍取反是为了向RAM写数据时,clk的上升沿在数据的稳定期。取反是因为两个信号都是低电平有效,而RAM是高电平有效。或操作是将两个信号合成一个clk信号。因为wr和rd信号并不冲突,因此,读RAM和写RAM都可以通过这个clk来驱动。

//-------------------------clk ----------------------------// reg wr_clk1,wr_clk2; always @(posedge PLL_100M or negedge RST_n) begin if(!RST_n) begin wr_clk1 <= 1'd1; wr_clk2 <= 1'd1; end else {wr_clk2,wr_clk1} <= {wr_clk1,wr}; //提取读写时钟 end wire clk = (!wr_clk2 | !rd); //将rd和wr信号结合起来,读写RAM操作都用此信号 //取反是因为两个信号都是低电平有效,wr延后2个100M时钟周期,是为了保证存储数据的时候,时钟的上升沿在数据的稳定期。

- 结合时序图理解可能更为清晰,下图是相关信号的波形图,可以参考此图对代码进行理解。

- 通过上图可以看到,wr信号和rd信号分别处于不同的时期,clk信号和(!rd)信号同步,和wr_clk2同步。且地址寄存器address的值和数据db的值符合程序设置。说明ARM成功通过FSMC读写RAM内的数据。

五、操作流程和测试结果

1.操作步骤

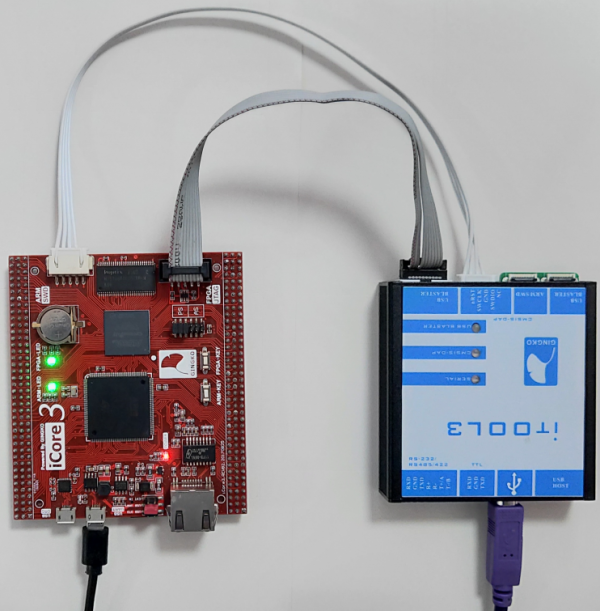

- 将仿真器和iCore3双核心板连接。

- 给开发板供电。

- 将编译成功的FPGA代码和ARM代码分别下载到开发板。

- 观察现象,亦可通过signalTap查看相关信号,判断时序和逻辑是否有误。

2.实验结果

icore3_fpga_13.txt · 最后更改: 2022/03/18 15:41 由 sean