icore4tfpga_22

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-03-13 | gingko | 初次建立 |

实验二十二:FIFO实验——基于FIFO的ARM与FPGA数据存取

一、 实验目的与意义

- 掌握FIFO IP核的调用及例化方法。

- 掌握FIFO存储器的读写时序。

- 掌握QuartusII的使用方法。

二、 实验设备及平台

- iCore4T 双核心板。

- iTool A(或相同功能)仿真器。

- USB Type C 线缆。

- Keil MDK 开发平台。

- Quartus开发平台。

- 电脑一台。

三、 实验原理

- FIFO(First Input First Output)是一种先进先出的存储器。与之前的RAM相比较而言,FIFO存储器没有地址线,操作起来更加的简单,但其缺点就在于,只能顺序读写数据,不能随意指定读写数据的地址单元。根据读写时钟的相同与否,FIFO可分为异步FIFO和同步FIFO两种,本实验讲的是异步FIFO。

- FIFO的读写时钟在每个时钟上升沿到来时对数据进行操作;读写请求信号为高电平有效,低电平失能。

- FIFO读写操作的工作原理:在FIFO内部有读写指针,其中,读指针指向下一个将要读取数据的地址,复位时指针指向0地址;写指针指向下一个将要写入数据的地址,服为止指针指向0地址。

- FIFO的空/满检测是FIFO应用中的一个重要参数,不过在应用过程中,这两项参数不是必须使用的,可以通过控制读写时钟及读写请求信号来避免溢出,即通过人为的控制数据长度避免读写溢出(本实验即使如此)。

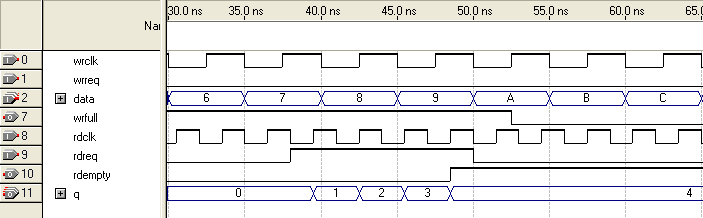

- 根据上面的介绍可知,FIFO的读写操作时序如图22.1所示。

- 本实验基于ARM+FPGA构架,通过SPI实现ARM与FPGA之间通信,以FIFO作为FPGA内部的数据存储器,实现ARM对数据的读写功能。ARM通过SPI将数据发送到FPGA,FPGA顺序的将数据写入FIFO中,再顺序读出,实现数据的交互,实验流程较为简单,重点是掌握FIFO IP核的调用及时序的描述。

四、 FIFO IP核调用

1.新建一个工程名为pll的工程,然后点击Tool →Megawizard Plug-In Manager,如图22.2所示。

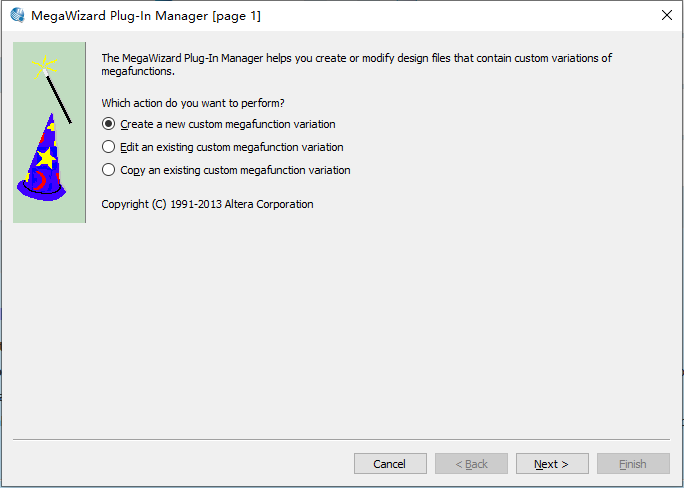

2.在下面界面中保持默认,直接Next即可,如图22.3所示。

2.在下面界面中保持默认,直接Next即可,如图22.3所示。

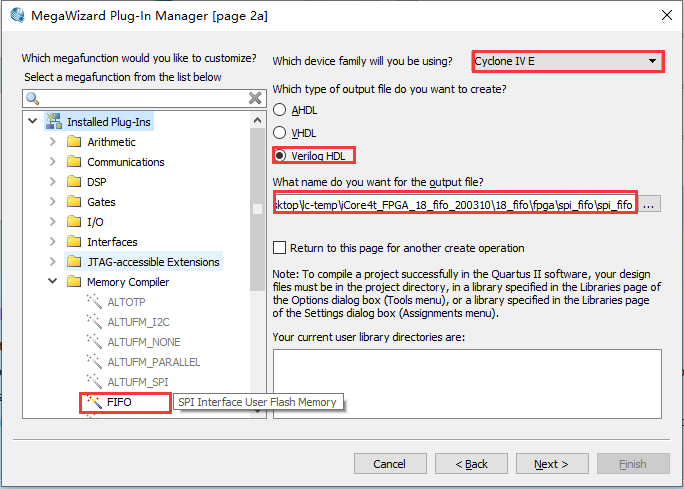

3.在该界面中选择FIFO IP核、芯片类型、硬件描述语言类型及IP核相关文件存储位置,如图22.4所示。

3.在该界面中选择FIFO IP核、芯片类型、硬件描述语言类型及IP核相关文件存储位置,如图22.4所示。

4.在该对话框中设置FIFO的位宽、存储深度,并选择同步还是异步FIFO(一般选择异步),如图22.5所示。

4.在该对话框中设置FIFO的位宽、存储深度,并选择同步还是异步FIFO(一般选择异步),如图22.5所示。

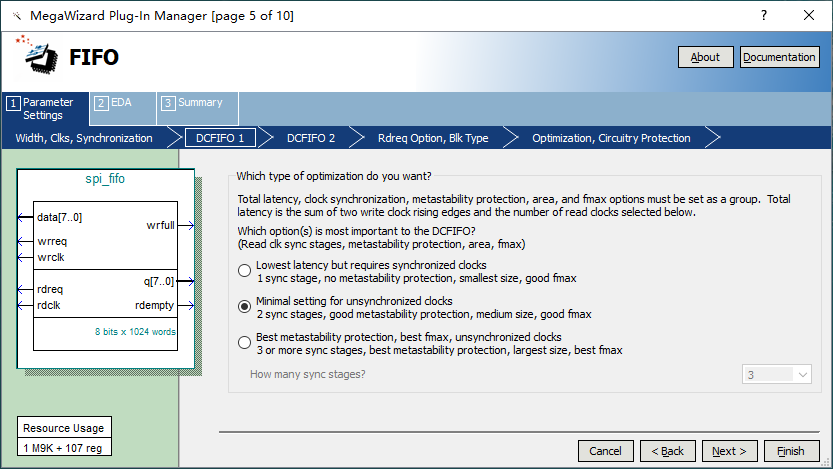

5.该对话框保持默认直接Next即可,如图22.6所示。

5.该对话框保持默认直接Next即可,如图22.6所示。

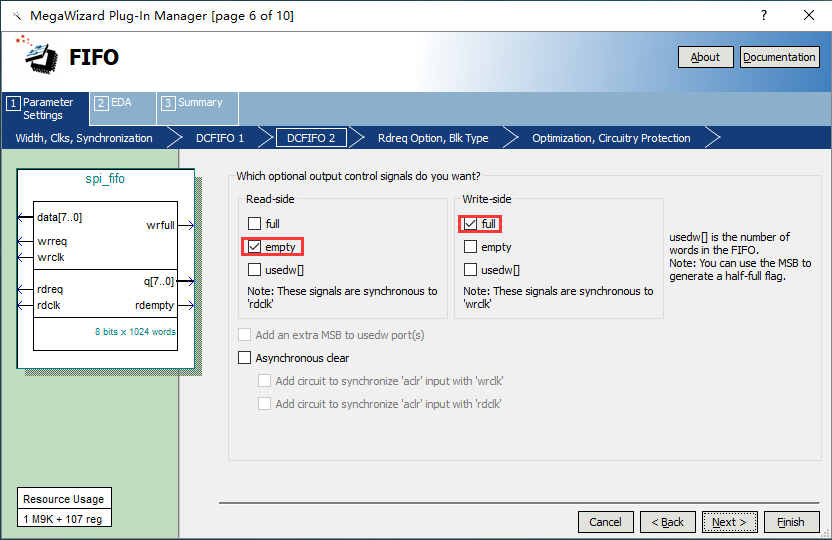

6.在此对话框选择空满标志信号及信号的输出方式(一般空信号选择读方向,满标志选择写方向),如图22.7所示。

6.在此对话框选择空满标志信号及信号的输出方式(一般空信号选择读方向,满标志选择写方向),如图22.7所示。

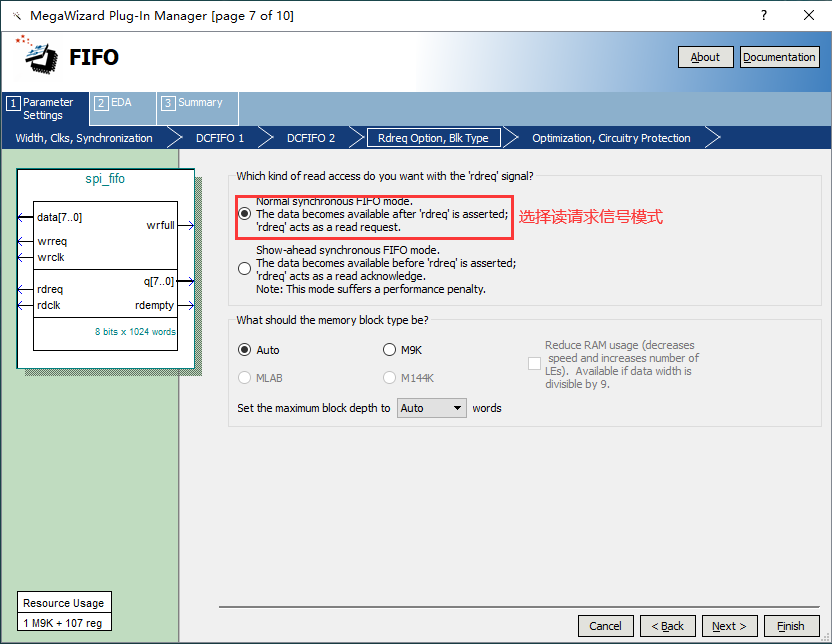

7.选择读请求的模式,一般选择常规模式,如图22.8所示。

7.选择读请求的模式,一般选择常规模式,如图22.8所示。

8.该对话框选择是否禁用“上溢”和“下溢”检测,一般选择禁用,如图22.9所示。

8.该对话框选择是否禁用“上溢”和“下溢”检测,一般选择禁用,如图22.9所示。

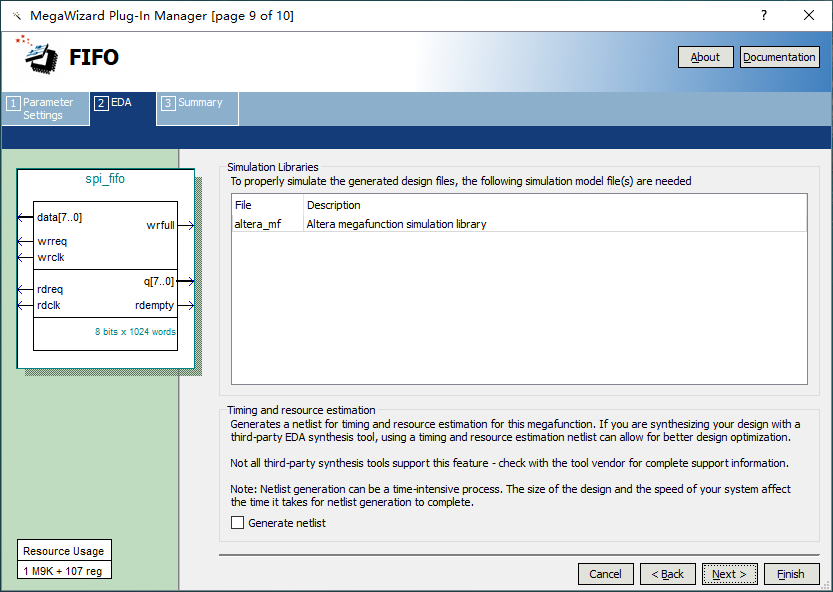

9.保持默认值,直接Next即可,如图22.10所示。

9.保持默认值,直接Next即可,如图22.10所示。

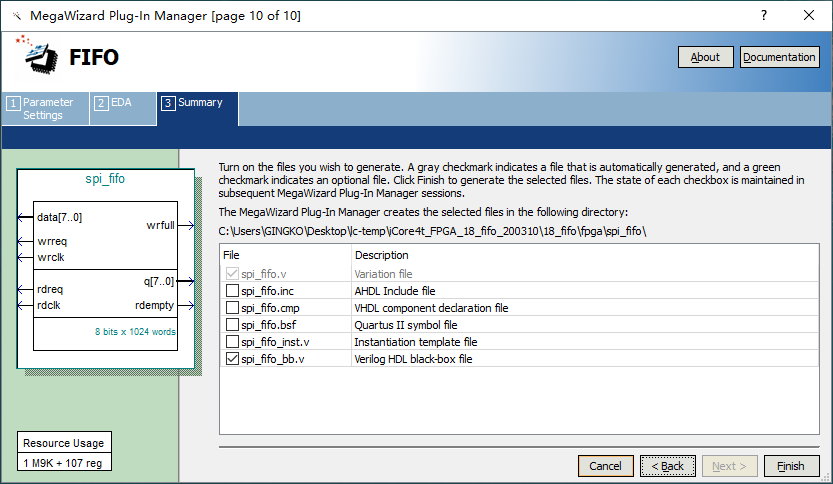

10.该对话框选择要生成的FIFO相关文件,一般保持默认即可,如图22.11所示

10.该对话框选择要生成的FIFO相关文件,一般保持默认即可,如图22.11所示

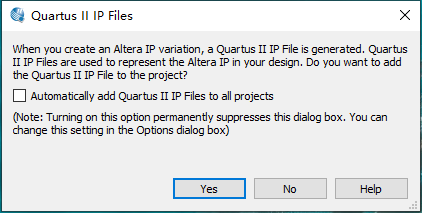

11.IP核设置完成后出现下面对话框,点击Yes,否则将无法正常调用FIFO,如图22.12所示。

11.IP核设置完成后出现下面对话框,点击Yes,否则将无法正常调用FIFO,如图22.12所示。

五、 代码讲解

IP核调用只是生成相关的模块文件,在应用中要实现存储、读写功能,还需要对IP核进行实例化操作,FIFO IP核例化代码如下:

//------------------------------------------------// //spi_fifo //负责存储SPI通信的数据 //FIFO:先进先出,主要用于缓存数据。 spi_fifo u0( .data(receive_byte), .wrclk(wrclk), .wrreq(wrreq), .wrfull(), .rdclk(rdclk), .rdreq(rdreq), .rdempty(), .q(data_out) );

六、 实验步骤及实验结果

- 将硬件正确连接,如图22.13所示。

- 打开putty串口调试工具,打开设备管理器查看对应的端口信息,在putty中打开对应的端口,用于打印串口信息及控制FIFO读写;

- 将编写好的FPGA代码进行编译,并下载到开发板中;

- 将编写好的ARM代码编译,并下载到开发板中,putty工具中会打印相应的SPI通信相关信息(若想多次测试,查看结果在putty中输入“test”即可);

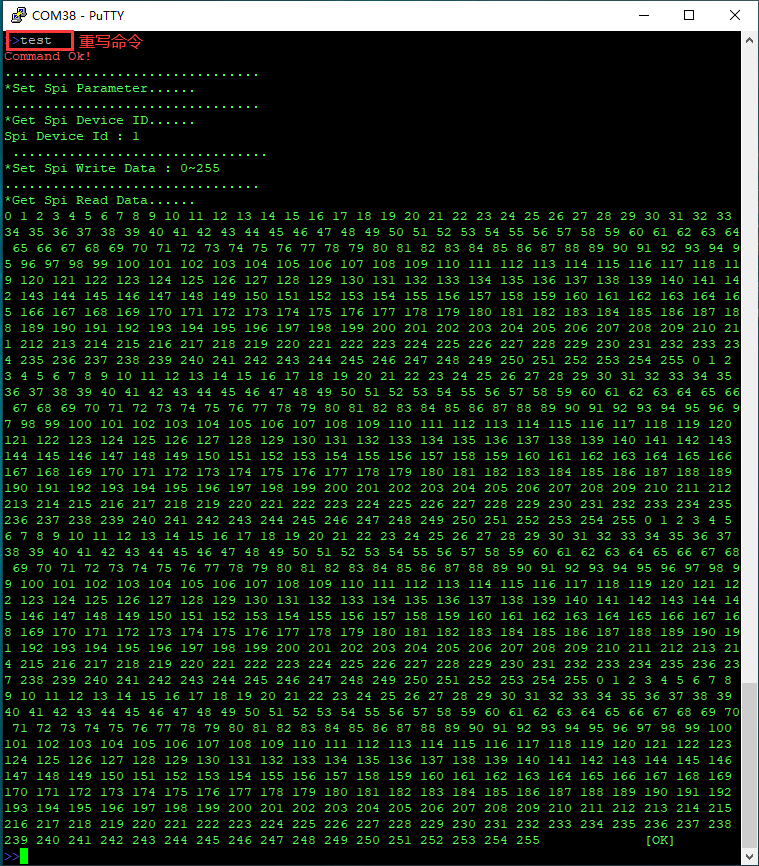

- 观察实验现象及putty终端打印信息——FPGA_LED闪烁,putty终端打印如图22.14所示。

七、 拓展实验

1.通过Signaltap观察FIFO读写时序是否和参考时序一致。

icore4tfpga_22.txt · 最后更改: 2024/04/10 11:28 由 zhaowenzhe