icore4tx_fpga_12

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-05-22 | gingko | 初次建立 |

实验十二:Modelsim 仿真实验

一、实验目的与意义

- 安装Modelsim软件。

- 学习建立Modelsim工程并对Xilinx FPGA工程进行仿真。

二、实验设备

- ISE开发软件。

- 64位WIN10系统的PC(本例程是以64位系统为例)。

- Modelsim 10.1版本安装包。

三、Modelsim 安装及破解

- Modelsim 仿真工具是Model公司开发的,支持Verilog、VHDL 以及他们的混合仿真。通过Modelsim软件,可以对Xilinx FPGA工程文件进行仿真,观察工程内变量的值和信号逻辑的变化,从而直观的分析设计中存在的逻辑错误和设计上的缺陷。

1、安装步骤:

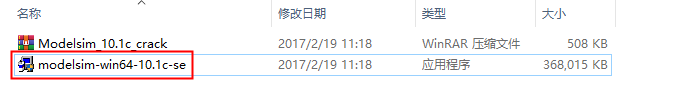

- 1. 双击 modelsim-win64-10.1a-se.exe 文件开始安装。

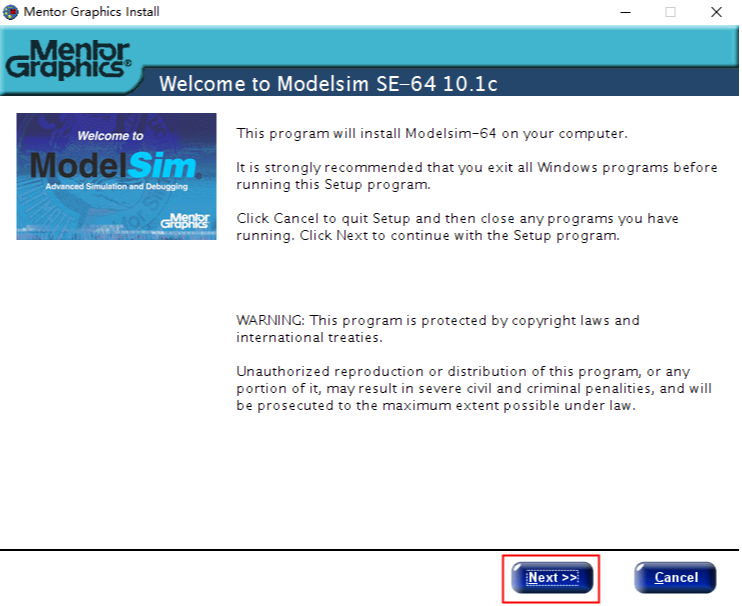

- 2. 双击.exe 文件后进入如下界面,点击 Next。

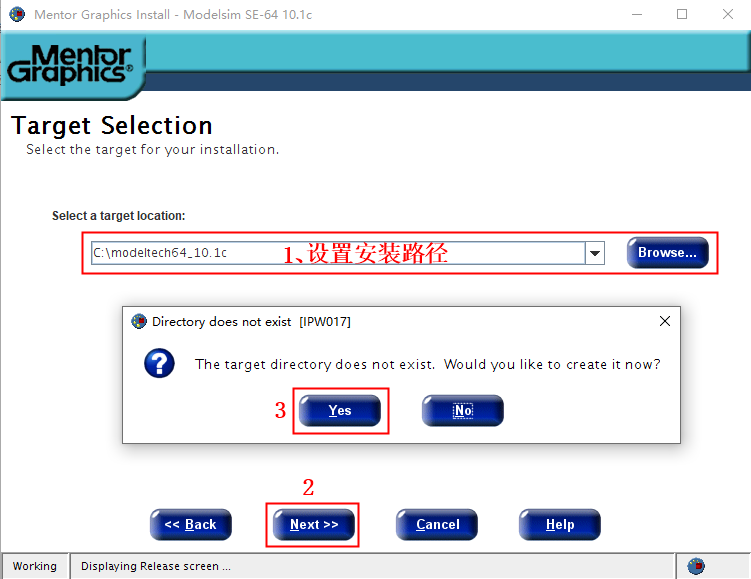

- 3. 红框1处选择安装路径,然后点击 Next。弹出窗口询问是否建立文件夹,选择Yes.

- 4. 此界面点击 Agree 即可进入下一步的安装

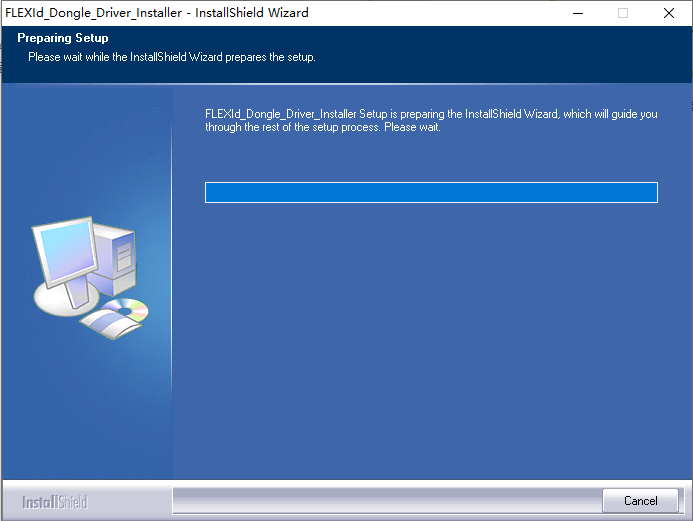

- 5. 接下来进入进度条界面,此过程中弹出的界面全部点击 Yes。

- 6. 此界面点击 Cancel, 进入下一个安装步骤。

- 7. 点击Yes,电脑立即重启;点击 No,空闲时手动重启,大家自行选择。至此安装结束。

- 1.接下来进行破解。

- 1) 首先将MentorKG.exe和patch_dll.bat文件复制到安装目录的win64 文件夹下。

- 2) 然后将Win64文件夹中的mgls64.dll和mgls.dll文件的只读属性去掉,运行patch_dll.bat,等待生成TXT格式的license文件,另存为到安装目录下,命名为LICENSE.TXT。

- 3) 恢复,mgls.dll和mgls64.dll两个文件的只读属性。

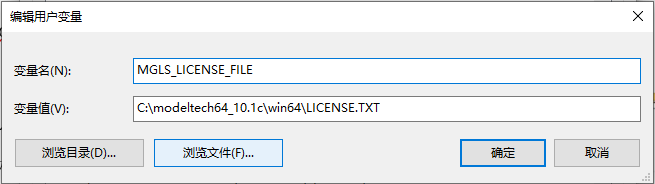

- 2.接下来添加系统环境变量,控制面板→系统和安全→系统→高级系统设置→环境变量→新建。变量名MGLS_LICENSE_FILE,变量值为 License.txt 的路径(点击浏览文件,找到License.txt文件,选中即可),然后点击“确定”结束。

四、Modelsim 仿真工具调用

- 作为modelsim讲解示例,本实验以实验八的呼吸灯实验为基础进行。实验目的是通过Modelsim软件仿真,在Modelsim上直观查看计数器变量值的变化和控制LED亮灭的信号电平变化。下面讲解如何在Modelsim工程以及如何对呼吸灯实验进行仿真。

- 1.在正式建立Modelsim仿真工程之前,将实验八呼吸灯的工程复制过来,然后建立一个文件夹,用于存放Modelsim工程,本实验建立的文件夹名为counter_sim。

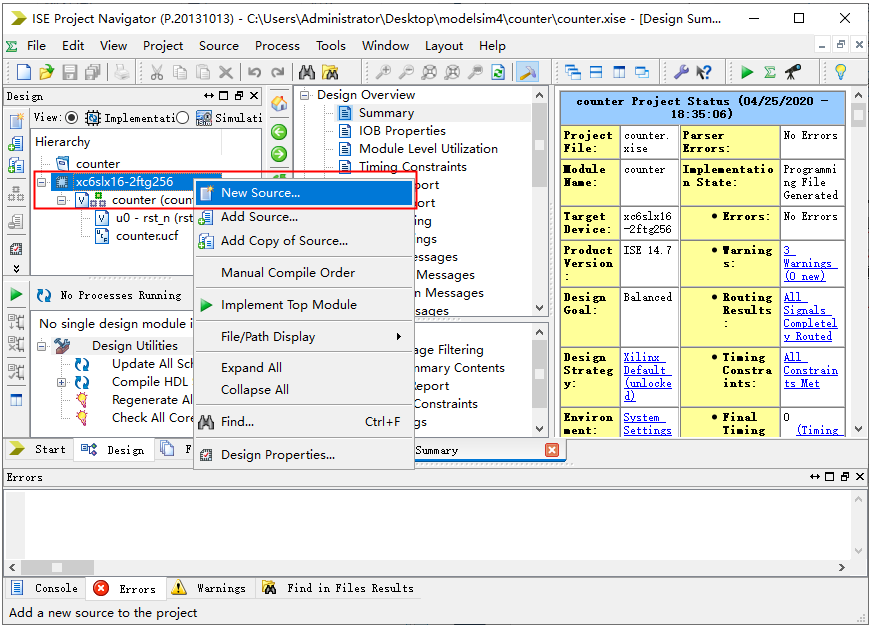

- 2.打开FPGA工程,右击,点击New Source。

- 3. 选择新建文件类型为Verilog Test Fixture,File name命名为counter_tb,然后点击Next。注意测试文件的存放路径,本实验将其和FPGA工程的源文件放到一起。

- 4. 点击Next。

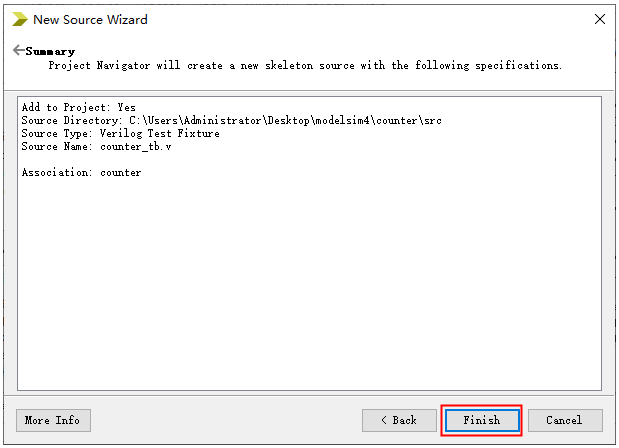

- 5. 点击Finish

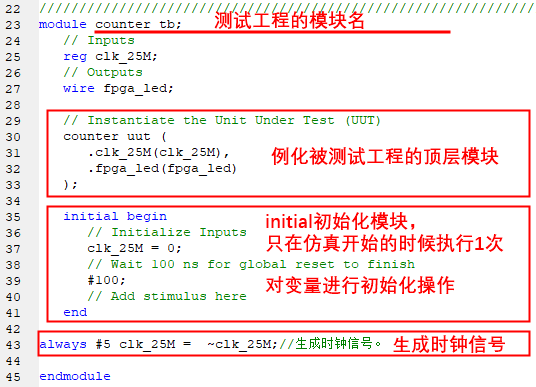

- 6. 在工程代码编辑区可以看到下图所示内容,为ISE自动生成的测试文件代码。可以看到,测试文件例化了工程文件的顶层模块,并设置了仿真的时间单位和精度。并对时钟状态进行了初始化。如下图所示:

- 7.向测试文件中添加代码:always #5 clk_25M = ~clk_25M;生成时钟信号。产生模拟的时钟信号,测试文件主要包含内容如下图所示。可以看到,测试工程是将FPGA工程的顶层模块作为Modelsim工程的一个子模块,例化到测试工程中,并给予时钟等外部激励信号,并通过initial语句对激励信号赋初值。

- a) Initial语句是顺序执行的,且仿真开始阶段只执行一次。Initial块内可以通过“# 数字”的方式实现延时控制。如“# 100”即等待100个时间单位后再执行下一条语句。因此可以通过延时控制模拟外部激励信号或者复位信号等。

- b) Always 块内的语句是循环执行的,如添加的“always #5 clk_25M = ~clk_25M;”语句,即等待5个时间单位后clk_25M信号进行翻转,并循环执行,以此产生周期10个时间单位的模拟时钟信号。

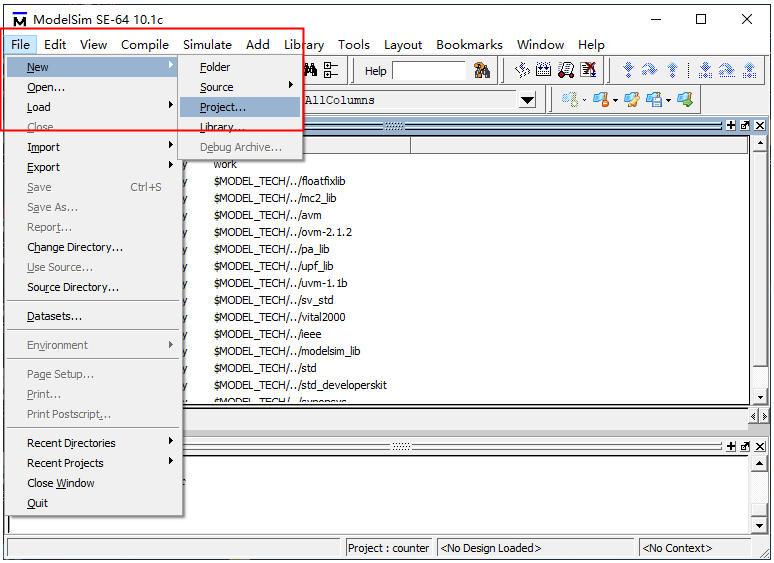

- 8.双击打开Modelsim软件,点击File New Project…,新建modelsim工程。

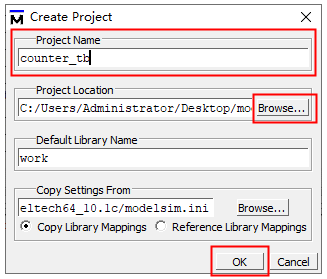

- 9.弹出窗中填写工程名字,最好和顶层文件名字一致。Project Location 是工作目录,通过点击Brose按钮,将目录选择为前面建立的文件夹cnt_sim。Default Library Name采用工具默认的work,然后点击OK。

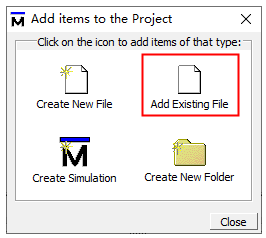

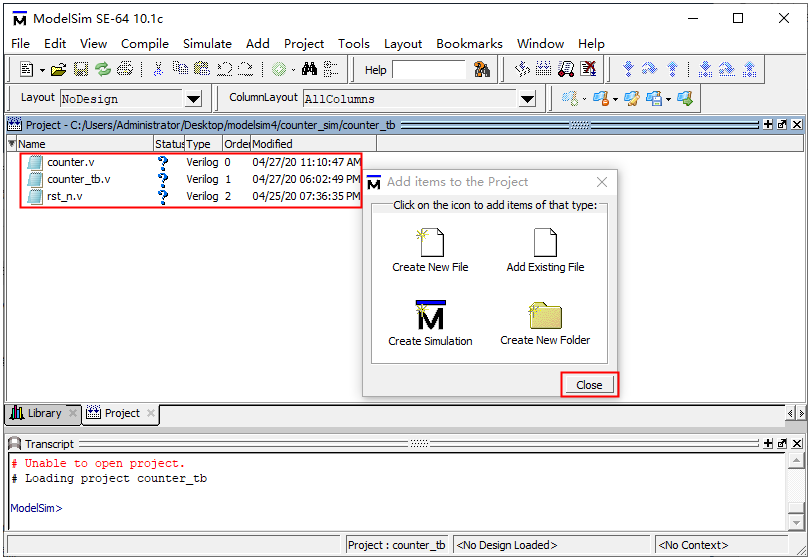

- 10.弹出如下窗口,询问是建立新文件还是添加新文件;本实验是在实验八的基础上进行的,由已经编写完成的工程文件,因此这里点击Add Existing File,即添加文件。

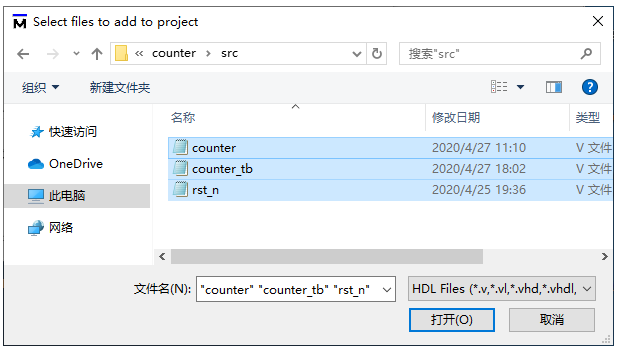

- 11.弹出窗口点击Browse,找到FPGA工程的源文件,选中后点击打开。

- 12.点击下图中OK。

- 13.Project界面里可以看到源文件已经添加进去,点击Close关闭Add items to the Project界面。

- 14.点击工具栏的编译按钮进行编译,编译完成无报错之后,如下图所示。

- 15.在Library中work目录下,选中测试文件counter_tb.v,双击或者右键点击Simulate。

- 16.然后点击工具栏的SimulateStart Simulation…。

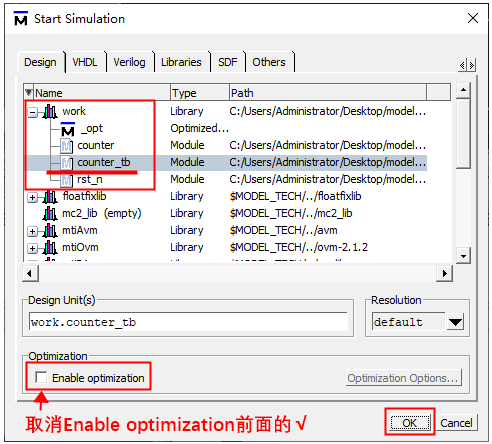

- 17.点击work前面的“+”,选中测试文件counter_tb,取消Enable optimization前面的“√”,然后点击OK。

- 18. Sim页面选中counter_tb下的uut模块,可以看到Objects窗口出现counter模块的信号列表,选中该列表中需要观察的信号,右键点击Add Wave

- 19. 可以看到Wave界面已经添加了需要观察的信号,选中cnt1信号,右键点击,选择RadixUnsigned,将cnt1变量的值调整成无符号十进制显示。同样的操作将cnt2也调整成无符号十进制数显示。

- 20. 点击Run-all,运行仿真。

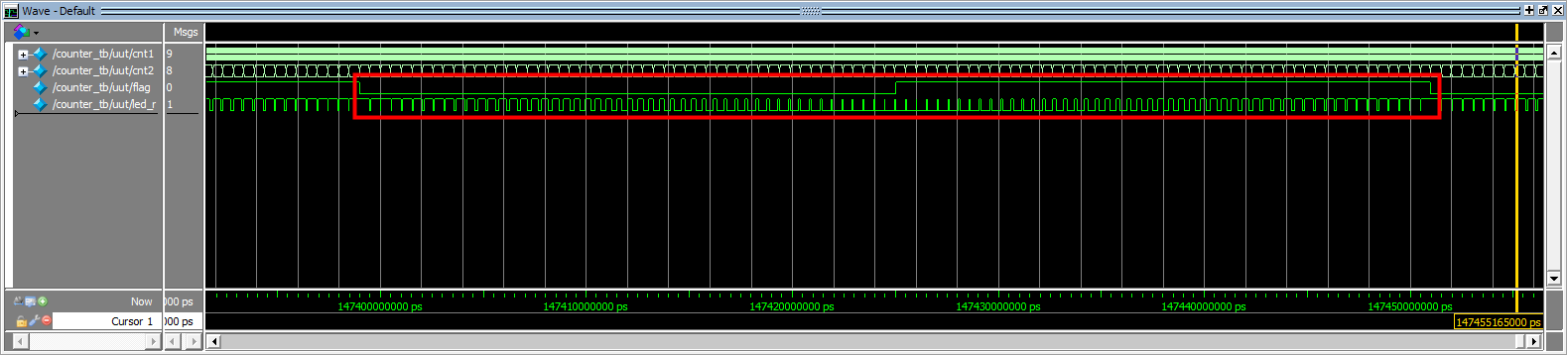

- 21. 可以直观的看到,led的控制信号的周期性变化,如下图所示(为了直观展示信号的周期变化,将counter文件中cnt1和cnt2的值累加到50后进行清零)。

五、实验现象

- 通过仿真波形,可以清晰的看到所添加信号波形的变化与程序所写的一致。

icore4tx_fpga_12.txt · 最后更改: 2022/04/01 11:37 由 sean