| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-04-28 | gingko | 初次建立 |

实验七:锁相环实验——锁相环IP核调用

一、实验目的与意义

- 掌握锁相环IP核的调用方法。

- 掌握ISE开发软件的使用方法。

二、实验设备及平台

- iCore4TX 双核心板。点击购买

- USB-CABLE(或相同功能)的仿真器。

- Micro USB线缆。

- ISE开发平台。

- 电脑一台。

三、实验原理

- 锁相环全称是锁相环路,是一种反馈控制电路,其主要特点是利用外部输入的参考信号控制环路内部振荡信号和相位。锁相环通常由鉴相器、环路滤波器和压控震荡器三部分组成。

- FPGA内部锁相环的工作原理主要是通过调用内部IP核,改变IP核内部分频、倍频及相位差等参数,以此改变输入参考时钟的输出频率和相位,从而产生用户所需要的时钟信号以驱动程序的运行。

- SPARTAN-6内部带有PLL硬件资源,通过ISE软件在工程中调用PLL软核,例化到FPGA工程内,从而调用FPGA的PLL硬件资源。本实验通过调用PLL软核,实现不同频率的时钟信号输出效果,以此讲解PLL模块在Xilinx FPGA 工程中调用的方法。

四、锁相环IP核调用步骤

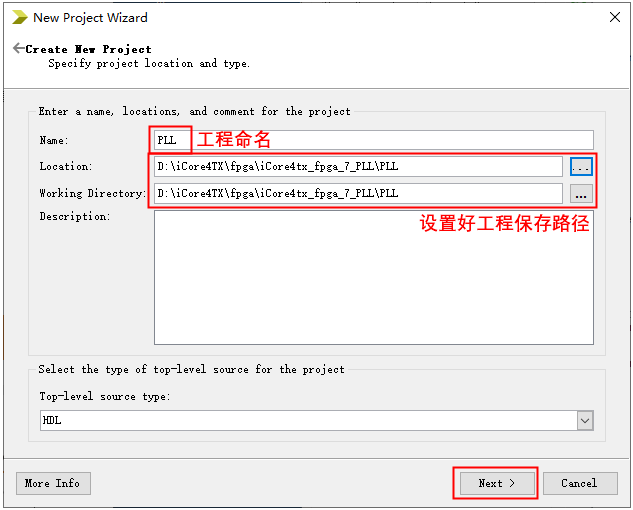

1、新建工程,命名为PLL。

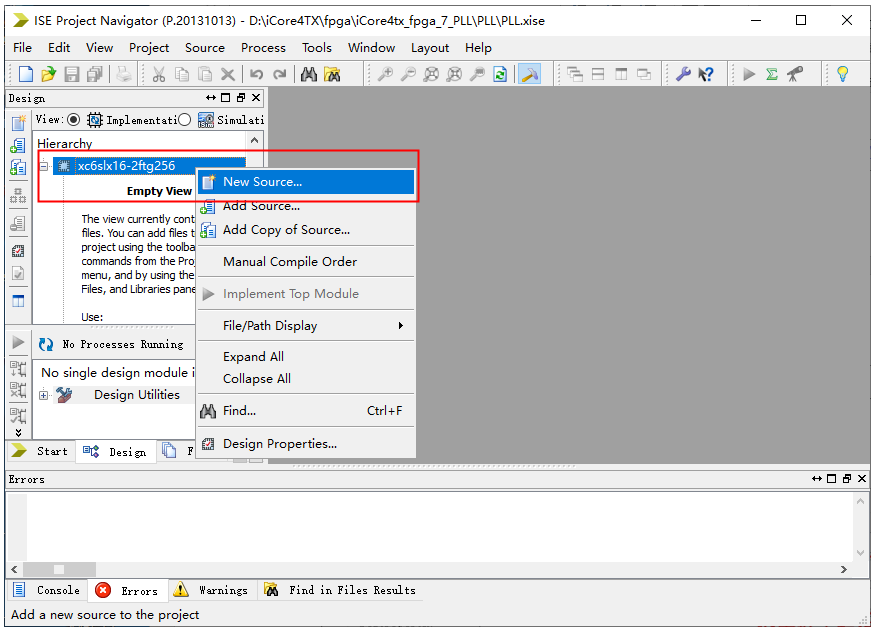

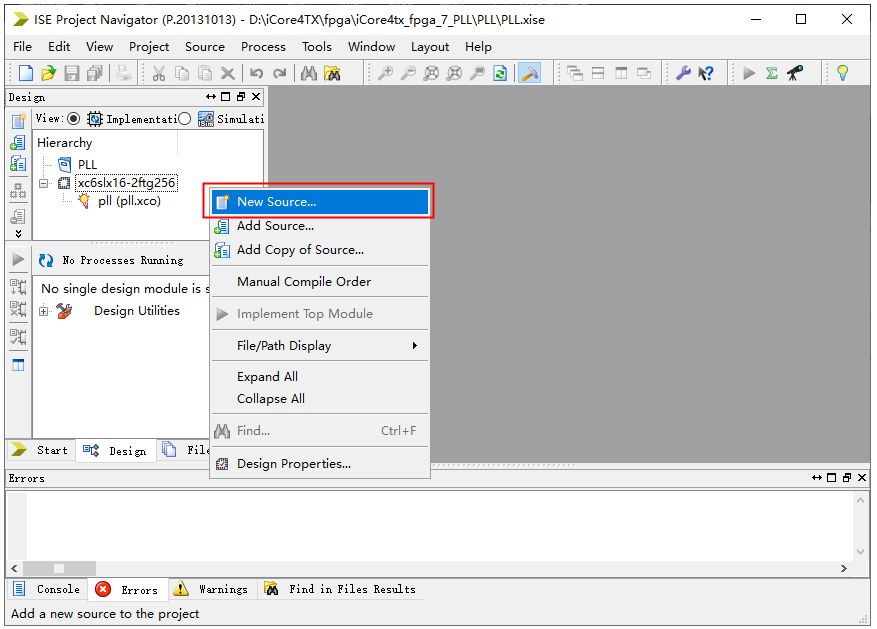

2、添加PLL核文件,在工程目录区右键单击,选则New Source…。

2、添加PLL核文件,在工程目录区右键单击,选则New Source…。

3、窗口左侧栏选中“IP(CORE Generator & Arichitecture Wizard)”右侧栏给文件命名为pll,点击Next。

3、窗口左侧栏选中“IP(CORE Generator & Arichitecture Wizard)”右侧栏给文件命名为pll,点击Next。

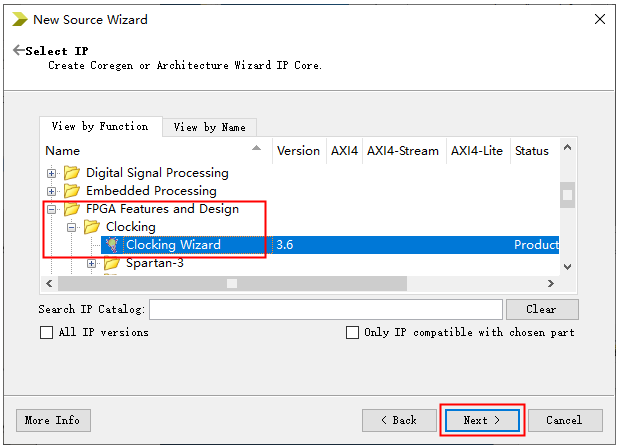

4、弹出的New Source Wizard 窗口中点击“FPGA Features and Design”前面的“+”,然后点击“Clocking”前面的“+”,点击选中“Clocking Wizard”。然后点击Next。

4、弹出的New Source Wizard 窗口中点击“FPGA Features and Design”前面的“+”,然后点击“Clocking”前面的“+”,点击选中“Clocking Wizard”。然后点击Next。

5、点击Finish进入PLL软核参数设置界面,Clocking Features里面勾选Frequency Synthesis(可以让PLL有多个不同的输出时钟)和Phase alignment(相位校准);Input Clock Information里输入时钟的值设置为25MHz(iCore4tx的外部晶振输入时钟是25MHz),其他保持默认,然后点击Next。

5、点击Finish进入PLL软核参数设置界面,Clocking Features里面勾选Frequency Synthesis(可以让PLL有多个不同的输出时钟)和Phase alignment(相位校准);Input Clock Information里输入时钟的值设置为25MHz(iCore4tx的外部晶振输入时钟是25MHz),其他保持默认,然后点击Next。

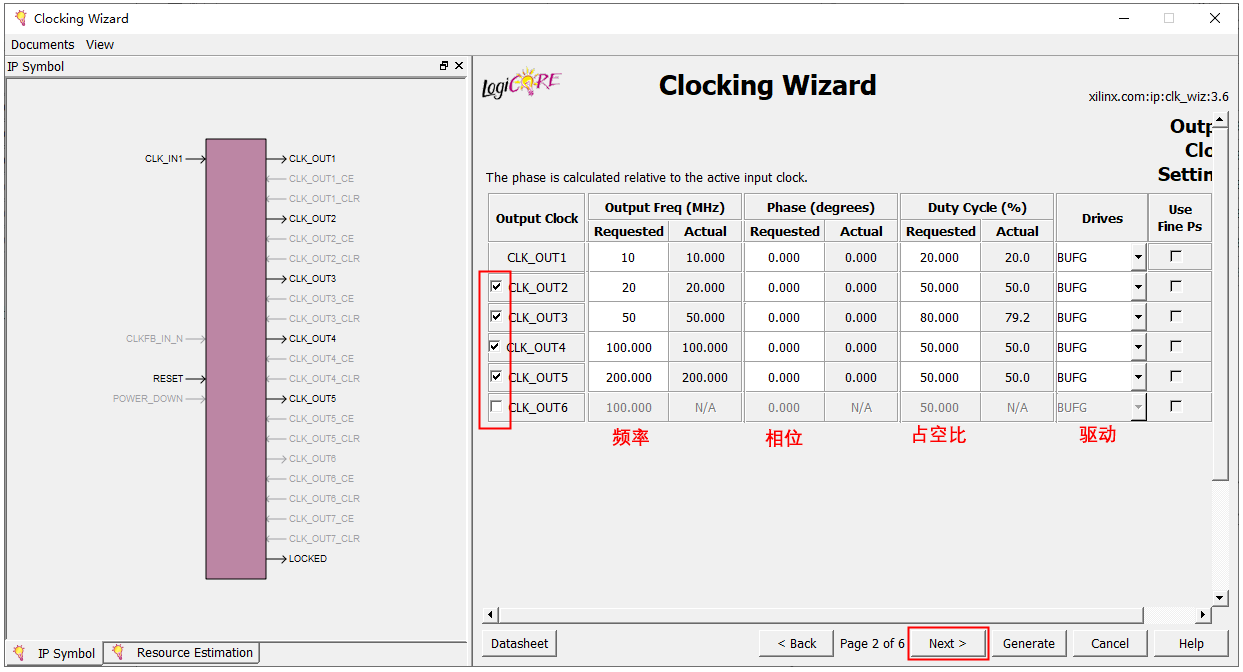

6、 输出时钟设置界面,默认1个输出时钟,总共可以设置6个输出时钟信号,只需在时钟信号前面打勾,即可使能输出时钟信号,还可以设置每个输出时钟的频率、相位、占空比、驱动等信息。这里我们设置如下图所示,然后点击Next。

6、 输出时钟设置界面,默认1个输出时钟,总共可以设置6个输出时钟信号,只需在时钟信号前面打勾,即可使能输出时钟信号,还可以设置每个输出时钟的频率、相位、占空比、驱动等信息。这里我们设置如下图所示,然后点击Next。

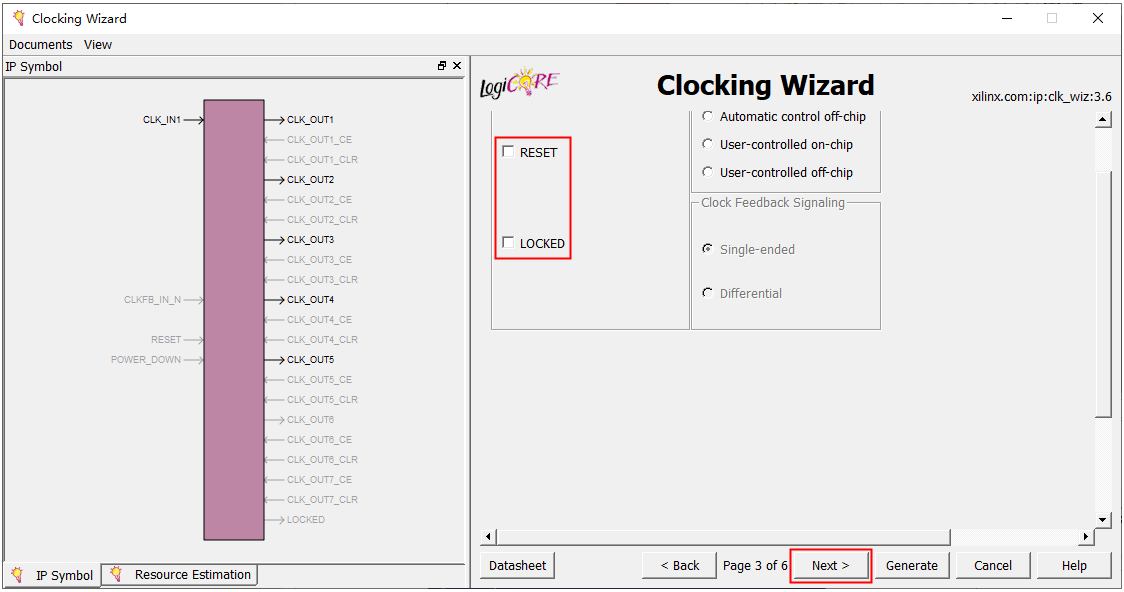

7、 RESET表示异步复位信号,LOCKED是PLL输出时钟稳定工作的指示信号,iCore4tx没有外部复位信号,这里两个选项可以不同勾选,直接点击Next。

7、 RESET表示异步复位信号,LOCKED是PLL输出时钟稳定工作的指示信号,iCore4tx没有外部复位信号,这里两个选项可以不同勾选,直接点击Next。

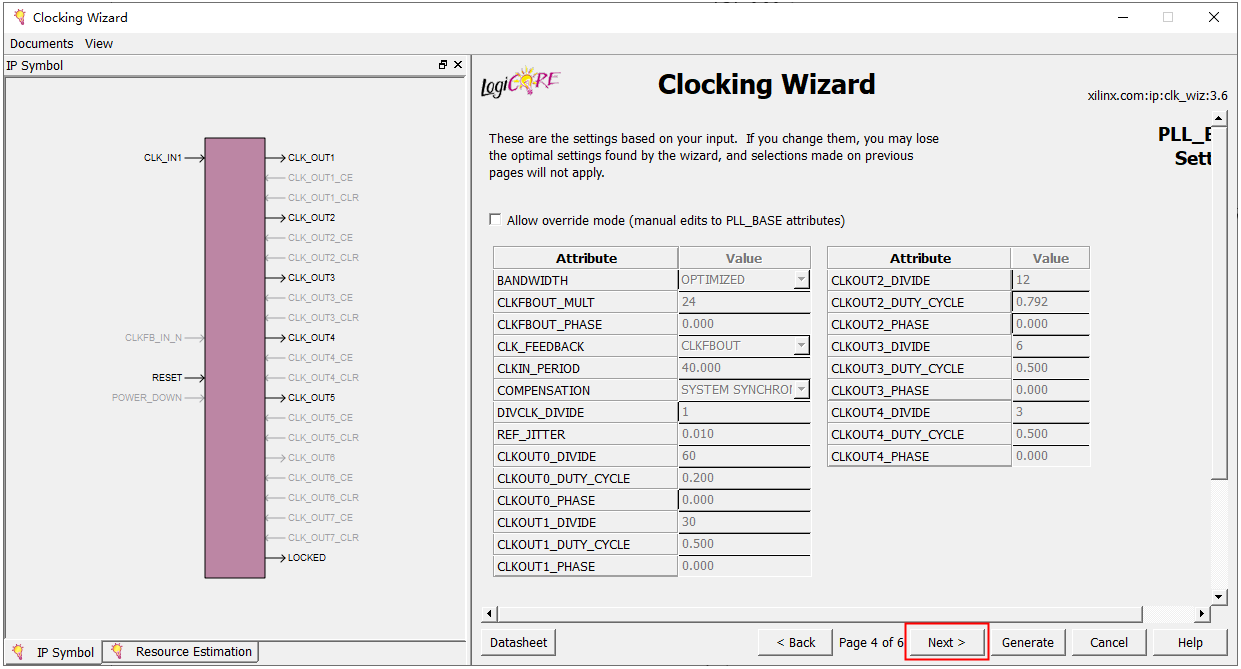

8、 对输入时钟的相关设置,保持默认,直接点击Next。

8、 对输入时钟的相关设置,保持默认,直接点击Next。

9、 本页对输入输出时钟进行命名,可以不做修改, 点击Next;本实验中将名字修改如下图中所示:

9、 本页对输入输出时钟进行命名,可以不做修改, 点击Next;本实验中将名字修改如下图中所示:

10、 点击Genarate生成PLL IP核。

10、 点击Genarate生成PLL IP核。

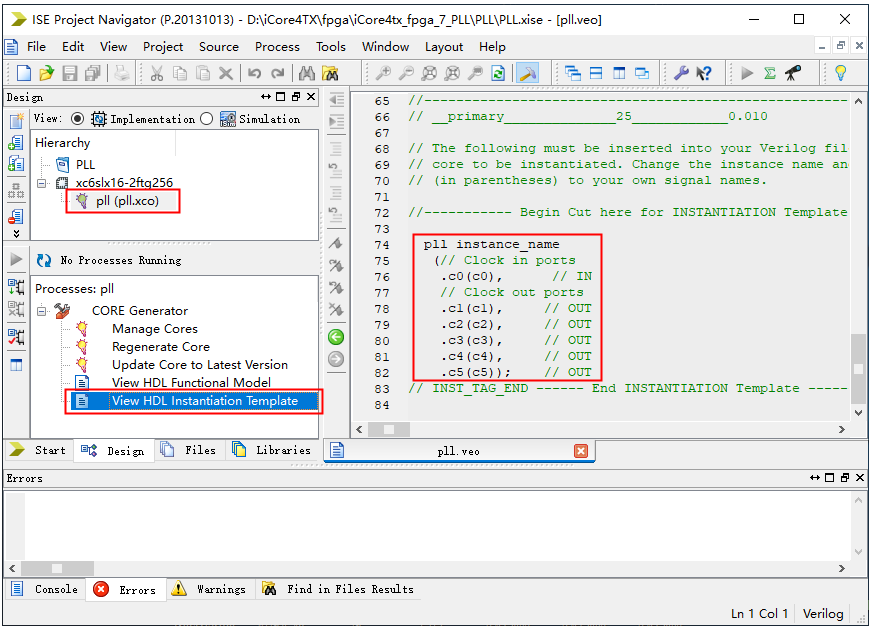

11、 可以看到工程目录里已经添加了PLL IP核文件,点击选中PLL IP核文件,再双击CORE Generator下的View HDL Instantiationtemplate,可以在编辑区看到PLL IP核的例化模板。

11、 可以看到工程目录里已经添加了PLL IP核文件,点击选中PLL IP核文件,再双击CORE Generator下的View HDL Instantiationtemplate,可以在编辑区看到PLL IP核的例化模板。

12、 新建顶层文件;在工程目录栏右键单击,选择New Source…。

12、 新建顶层文件;在工程目录栏右键单击,选择New Source…。

13、 弹出窗口左侧点击选中Verilog Module,右侧输入顶层模块的文件名:pll_top。

13、 弹出窗口左侧点击选中Verilog Module,右侧输入顶层模块的文件名:pll_top。

14、 设置顶层模块名字和输入输出信号,然后点击Next,之后点击Finish。

14、 设置顶层模块名字和输入输出信号,然后点击Next,之后点击Finish。

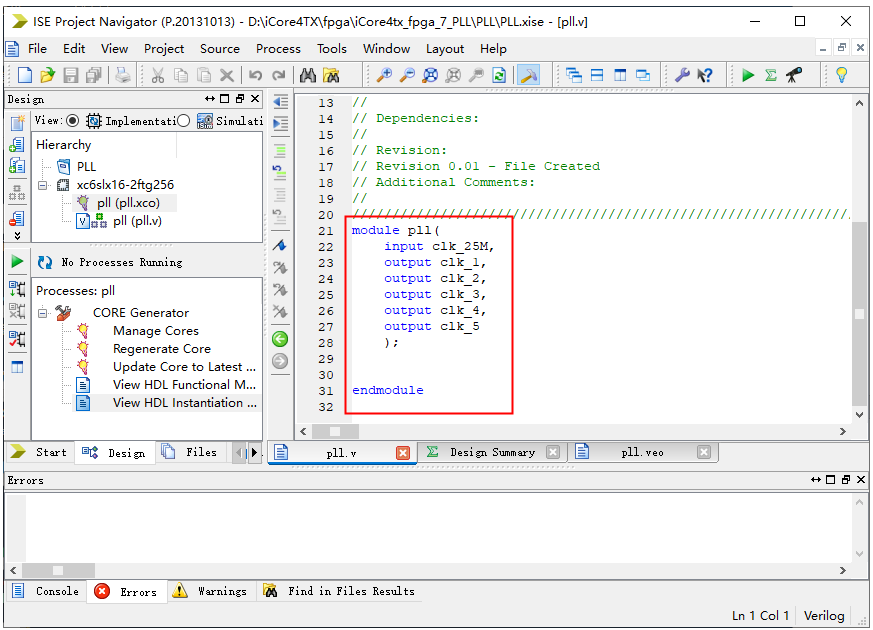

15、 可以在编辑区看到生成的顶层文件的内容。

15、 可以在编辑区看到生成的顶层文件的内容。

16、 给工程分配引脚,引脚绑定信息如下。

16、 给工程分配引脚,引脚绑定信息如下。

# PlanAhead Generated physical constraints NET "clk_25M" LOC = P8; NET "clk_1" LOC = F13; //普通IO引脚 NET "clk_2" LOC = G11; //普通IO引脚 NET "clk_3" LOC = F14; //普通IO引脚

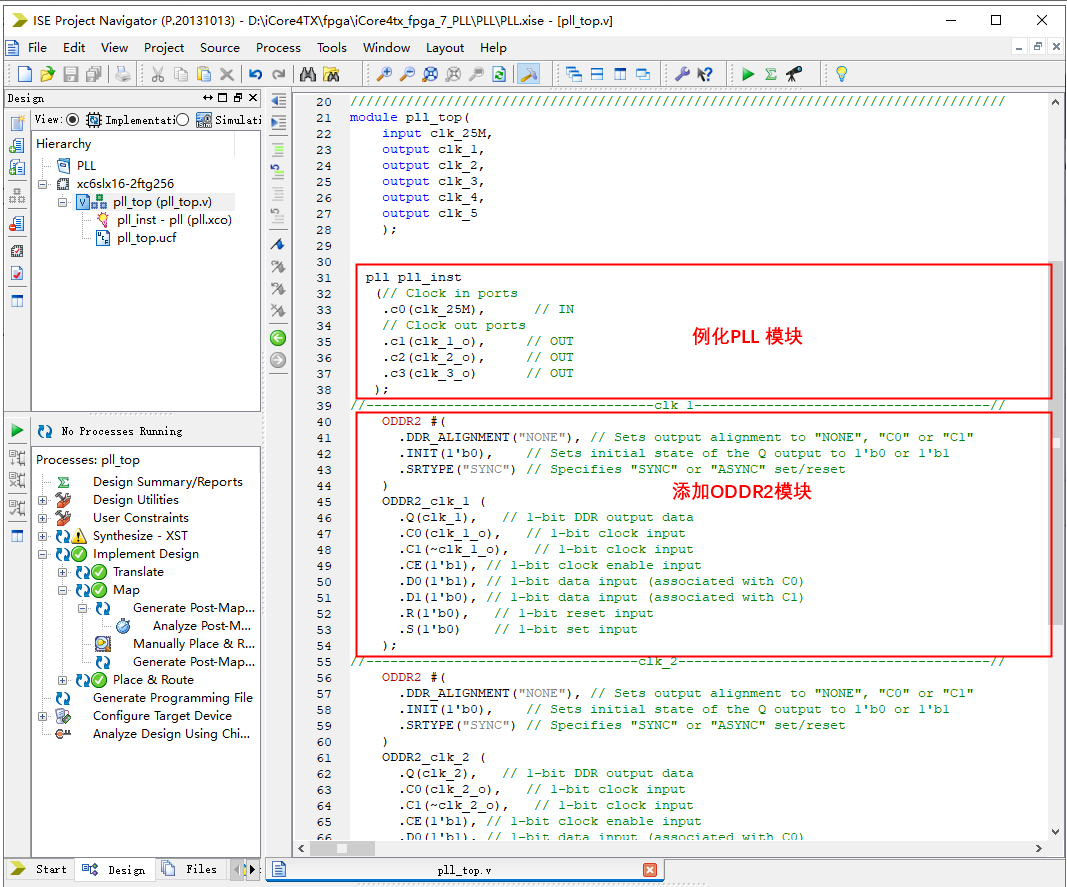

17、 Spartan6 FPGA中PLL产生的时钟是不能直接连接到FPGA的普通IO的,不过可以通过在PLL输出时钟信号和普通IO之间增加ODDR2模块缓冲的方式解决。

- 在顶层文件中添加如下内容,并修改引脚信息即可:

ODDR2 #( .DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_PLL输出时钟名 ( .Q(oddr2_I/O管脚名), // 1-bit DDR output data .C0(PLL输出时钟名), // 1-bit clock input .C1(~PLL输出时钟名), // 1-bit clock input .CE(1'b1), // 1-bit clock enable input .D0(1'b1), // 1-bit data input (associated with C0) .D1(1'b0), // 1-bit data input (associated with C1) .R(1'b0), // 1-bit reset input .S(1'b0) // 1-bit set input );

18、 将PLL IP核例化到顶层文件中,并修改信号名称;由于PLL的输出时钟信号有三个,所以这里要调用三个ODDR2模块,每个输出信号引脚都需要一个ODDR2模块缓冲。编辑后点击保存并编译,完成后如下图所示:

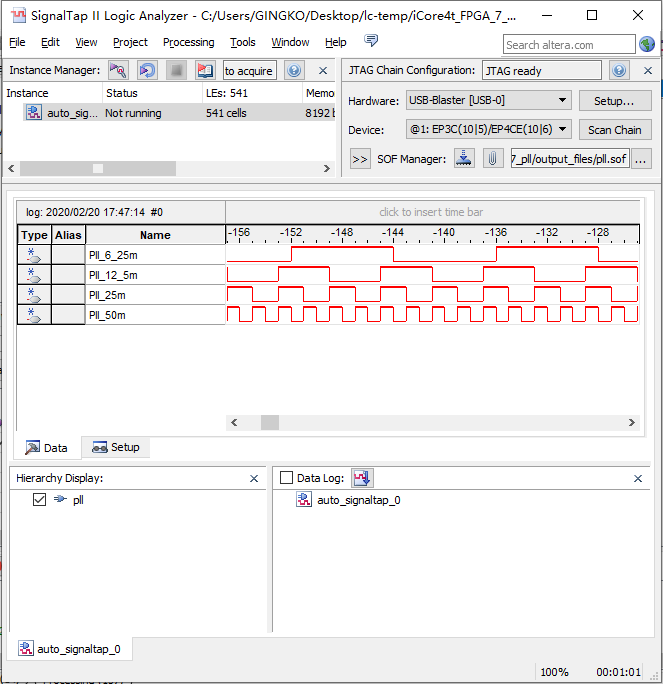

五、实验步骤及实验结果

六、拓展实验

- 思考下为什么6.25MHz输出时钟的相位与其他相位不一样;

- 更改相位和占空比,观察Signaltap采样结果由何不同。