| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-04-28 | gingko | 初次建立 |

实验二:新建FPGA工程——驱动LED

一、实验目的与意义

- 了解Xilinx FPGA开发软件ISE新建工程的方法和步骤。

- 了解Verilog语言描述功能模块的基本语法。

- 学习FPGA的GPIO引脚的定义和配置。

- 学习GPIO驱动外设的控制原理。

二、实验设备及平台

- iCore4TX 双核心板。点击购买

- USB-CABLE(或相同功能)的仿真器。

- Micro USB线缆。

- ISE开发平台。

- 电脑一台。

三、实验原理

- 本实验以点亮FPGA_LED,并控制其闪烁作为主要目标,在此基础上根据led的驱动原理,建立工程、编写led控制程序、配置GPIO。通过本实验,学习零基础构建FPGA工程并驱动LED闪烁的过程。

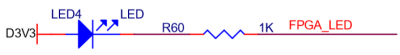

- led的驱动原理是通过程序,控制FPGA引脚IO的电平,从而实现对led的控制。led的硬件原理图如图2.1所示。从图中可以看出,led正极接3.3V电平,负极接到FPGA的引脚上。当FPGA_LED引脚为高电平时LED灭,为低电平时LED亮。

四、工程建立和编译

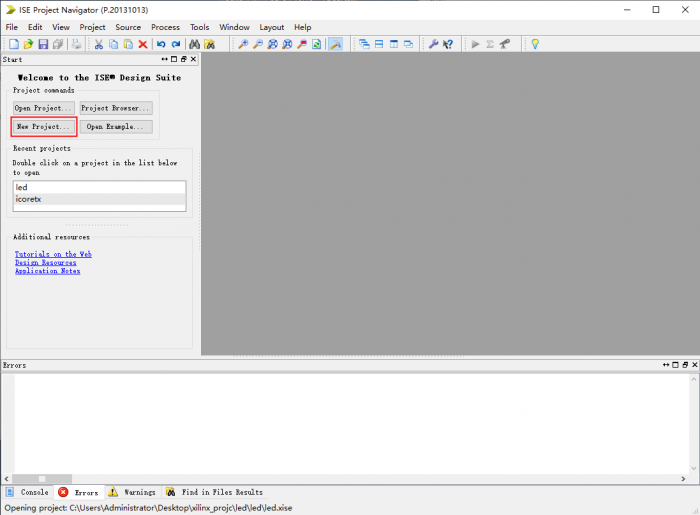

1、双击Xilinx FPGA 开发软件图标打开软件,出现下面界面,如图2.2所示,点击红框中New Project…。

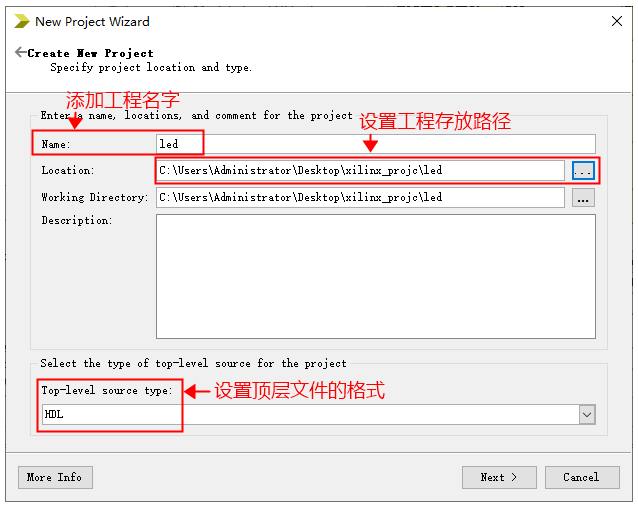

2、点击新建图标出现下面对话框,给新工程命名led,并选择好工程存放路径;顶层文件是Verilog HDL 语言编写的,因此这里将顶层文件的格式选为HDL,具体如下图所示。

2、点击新建图标出现下面对话框,给新工程命名led,并选择好工程存放路径;顶层文件是Verilog HDL 语言编写的,因此这里将顶层文件的格式选为HDL,具体如下图所示。

3、弹出窗口中选择对应的FPGA器件,iCore4TX双核心板的FPGA型号为Xilinx的XC6SLX16-2FTG256。则在下面界面选择FPGA器件时按照图中所示设置即可。然后点击Next。

3、弹出窗口中选择对应的FPGA器件,iCore4TX双核心板的FPGA型号为Xilinx的XC6SLX16-2FTG256。则在下面界面选择FPGA器件时按照图中所示设置即可。然后点击Next。

4、直接点击Next,弹出新建工程信息汇总,如下图,直接点击Finish。

4、直接点击Next,弹出新建工程信息汇总,如下图,直接点击Finish。

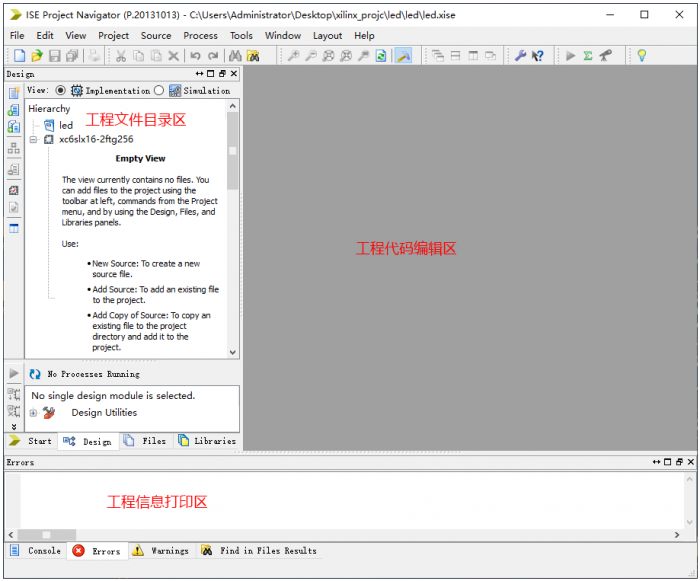

5、进入工程编辑界面,可以看到左边的工程文件目录区、右边的代码编辑区以及下边栏的工程信息打印区,如图2.6所示。

5、进入工程编辑界面,可以看到左边的工程文件目录区、右边的代码编辑区以及下边栏的工程信息打印区,如图2.6所示。

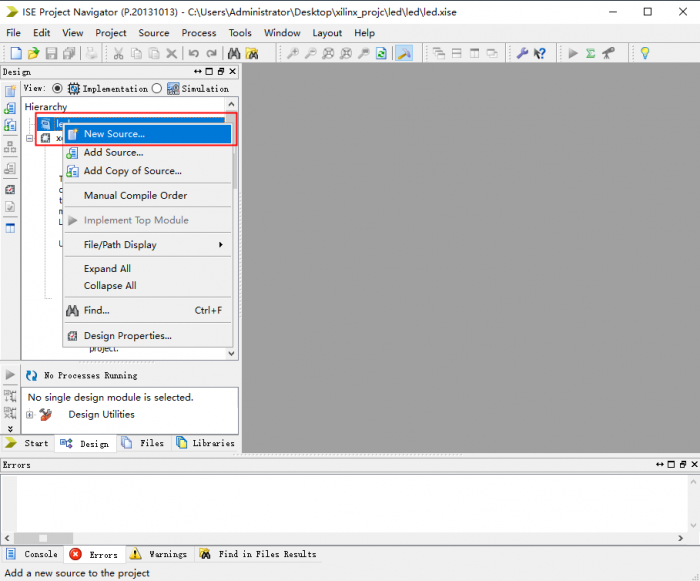

6、在工程文件目录区可以看到刚刚建立的新工程led,选中led工程,右键弹出下拉栏中点击New Source,新建Verilog文件。

6、在工程文件目录区可以看到刚刚建立的新工程led,选中led工程,右键弹出下拉栏中点击New Source,新建Verilog文件。

7、弹出窗口中,在左侧栏中选中Verilog Module,并将Verilog 文件命名为led;文件命名栏下面是新建文件的保存路径。这里选择保存路径时可以在工程文件夹下新建一个src文件夹,专门用于存储Verilog Source 文件。各项都设置好以后,点击Next。

7、弹出窗口中,在左侧栏中选中Verilog Module,并将Verilog 文件命名为led;文件命名栏下面是新建文件的保存路径。这里选择保存路径时可以在工程文件夹下新建一个src文件夹,专门用于存储Verilog Source 文件。各项都设置好以后,点击Next。

8、弹出窗口中设置led模块的端口信号,这里点击Next。

8、弹出窗口中设置led模块的端口信号,这里点击Next。

9、弹出窗口是新建的源文件led.v的信息提示,点击Finish。

9、弹出窗口是新建的源文件led.v的信息提示,点击Finish。

10、在主界面可以看到左边工程目录区多了led模块文件,右边代码编辑区是软件自动生成的模块信息。如下图所示。

10、在主界面可以看到左边工程目录区多了led模块文件,右边代码编辑区是软件自动生成的模块信息。如下图所示。

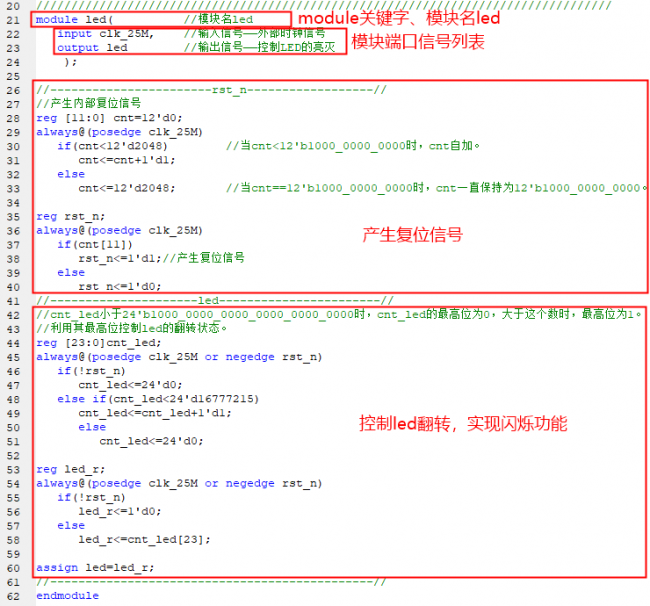

11、向led 模块module led中添加工程代码,通常一个完整的模块由module和endmodule为开始和结尾,除此外还包括模块名、端口变量及类型的定义、硬件语言描述、内部变量定义等信息,如此组成一个完整的功能模块,如图2.12所示。

11、向led 模块module led中添加工程代码,通常一个完整的模块由module和endmodule为开始和结尾,除此外还包括模块名、端口变量及类型的定义、硬件语言描述、内部变量定义等信息,如此组成一个完整的功能模块,如图2.12所示。

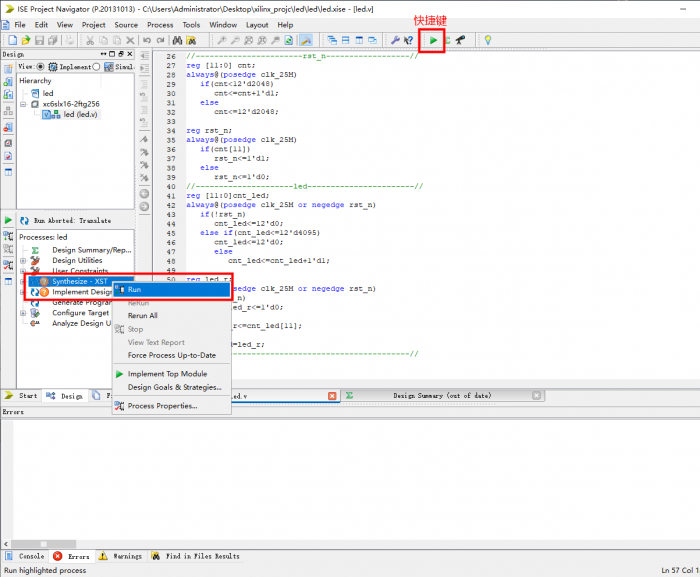

12、程序编写完成后进行编译,检查语法错误;首先在工程目录文件区选中顶层模块led,然后在工程目录区下边的Design栏,找到Synthesize – XST,右键点击Run,如图2.13所示。

12、程序编写完成后进行编译,检查语法错误;首先在工程目录文件区选中顶层模块led,然后在工程目录区下边的Design栏,找到Synthesize – XST,右键点击Run,如图2.13所示。

13、编译通过会在Synthesize – XST前面出现一个对号,表示没有语法错误。同时在工程编辑区会显示编译信息,如寄存器和逻辑门等的资源消耗情况。

13、编译通过会在Synthesize – XST前面出现一个对号,表示没有语法错误。同时在工程编辑区会显示编译信息,如寄存器和逻辑门等的资源消耗情况。

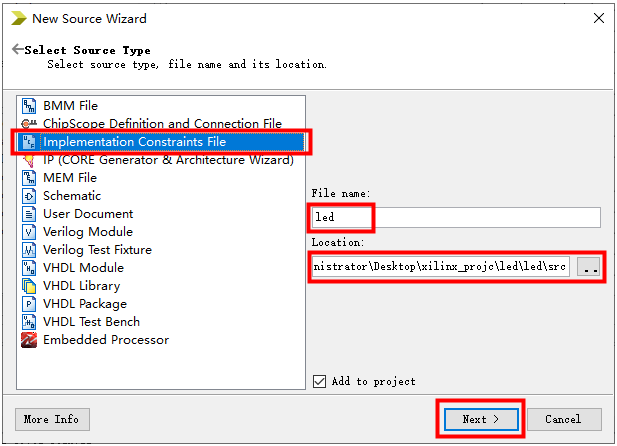

14、接下来是给模块端口列表里的输入输出信号分配引脚,采用ucf文件绑定引脚信息。首先在工程文件目录区右键选择New Source … 选项。弹出窗口中,文件格式选择Implementation Constraints File选项,左边分别输入文件名和保存路径,点击Next。

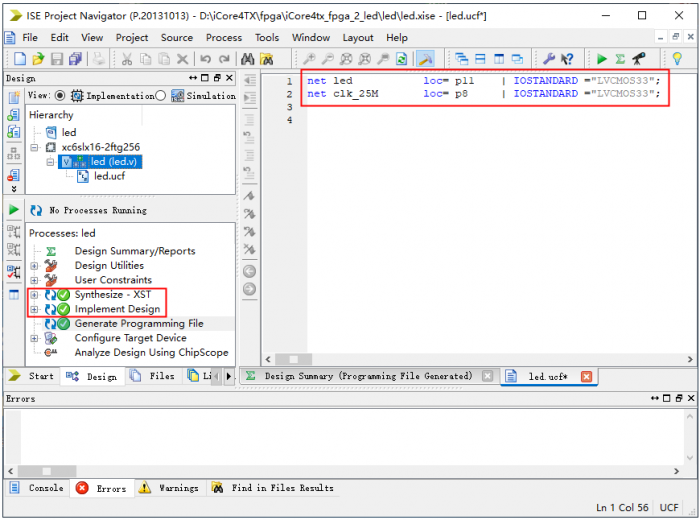

15、弹出的窗口直接点击Finish,完成引脚分配文件led.ucf文件的建立。在右边编辑区输入引脚绑定信息,格式为:

15、弹出的窗口直接点击Finish,完成引脚分配文件led.ucf文件的建立。在右边编辑区输入引脚绑定信息,格式为:

net 端口名称 LOC = 引脚编号| IOSTANDARD = “电压” ;

- 例如:

- net clk LOC = p4 | IOSTANDARD = “LVCMOS33”

led模块只有时钟输入信号clk_25M 和输出信号led。只需在ucf文件中添加这两个引脚的绑定信息即可。然后选中Design栏下的Implement Design,右键点击,然后点击Run,进行布局布线编译。完成后如下图所示。

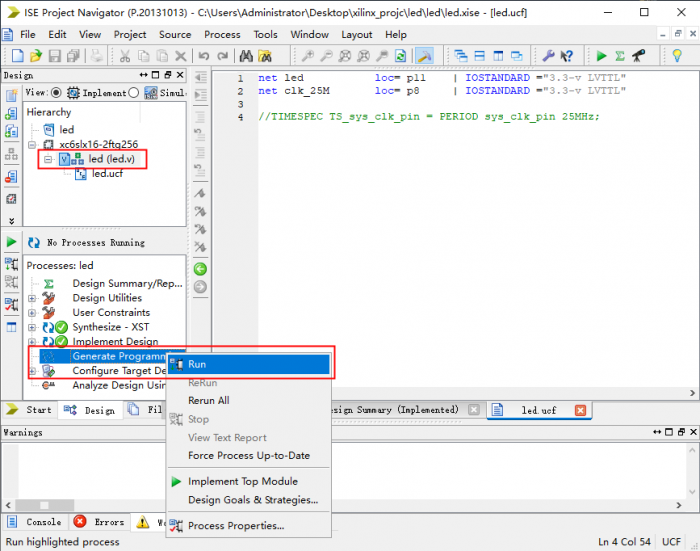

16、接下来生成可执行文件,可执行文件是ISE编译软件根据编写的程序和管教信息以及约束信息等生成的.bit文件。通过JTAG方式可下载到FPGA运行,但是不能直接固化到Flash中。在左侧Design栏下,右键选中Generate Programming File,点击Run。待编译成功,Generate Programming File 前面也会变成绿色对号。

16、接下来生成可执行文件,可执行文件是ISE编译软件根据编写的程序和管教信息以及约束信息等生成的.bit文件。通过JTAG方式可下载到FPGA运行,但是不能直接固化到Flash中。在左侧Design栏下,右键选中Generate Programming File,点击Run。待编译成功,Generate Programming File 前面也会变成绿色对号。

五、程序下载

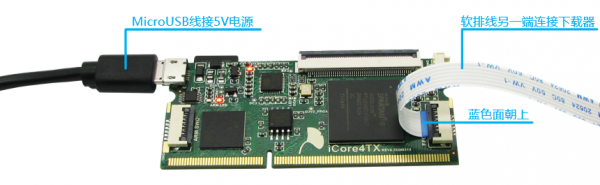

1、首先将下载器连接到iCore4TX核心板的JTAG接口,和MicroUSB 线连接到连接到iCore4TX 的核心板上,并给板子供电。

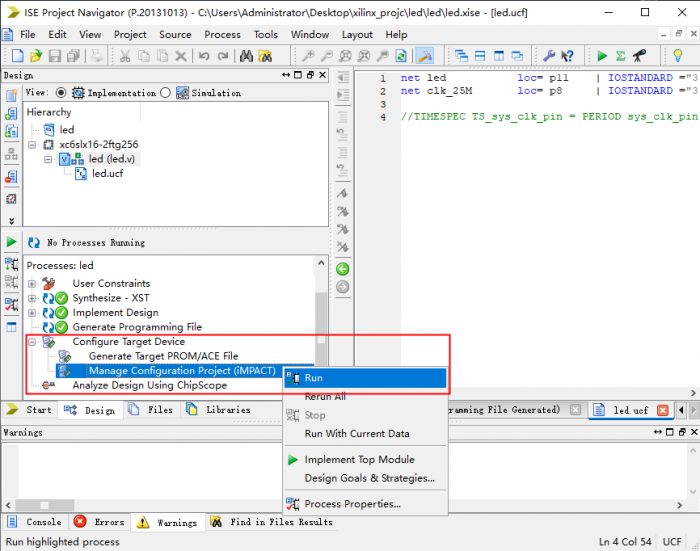

2、本例程采用iMPACT的下载方式。点击Configure Target Device 前面的“+”,然后选中“Manage Configuration Project(iMPACT)”,双击运行或者右键单击Run。如图所示。

2、本例程采用iMPACT的下载方式。点击Configure Target Device 前面的“+”,然后选中“Manage Configuration Project(iMPACT)”,双击运行或者右键单击Run。如图所示。

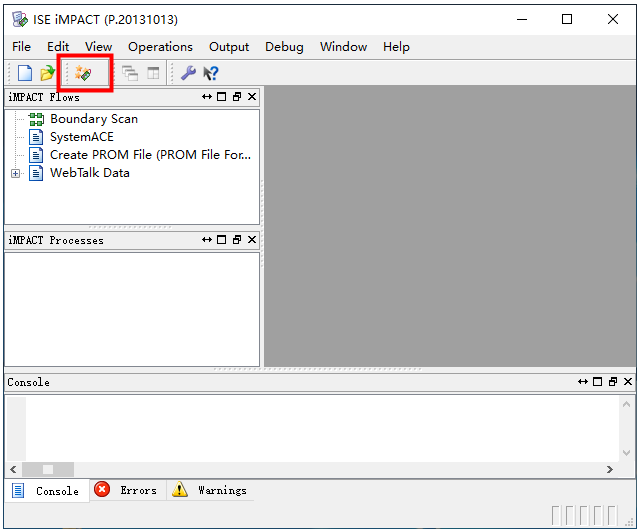

3、然后在弹出窗口中点击左上角的Launch Wizard。

3、然后在弹出窗口中点击左上角的Launch Wizard。

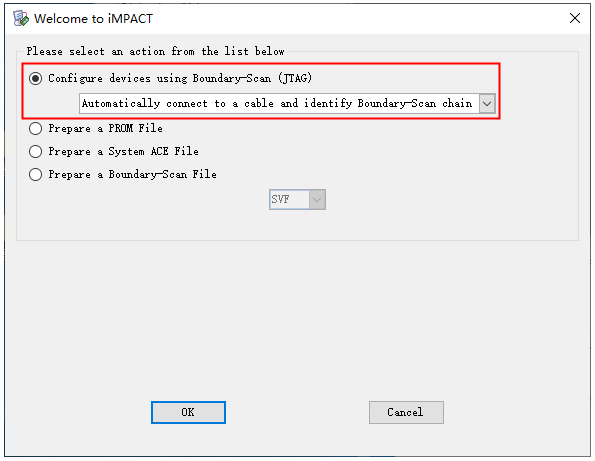

4、出现如下界面,直接点击OK,默认选择JTAG。

4、出现如下界面,直接点击OK,默认选择JTAG。

5、弹出提示中点击Yes,添加“.bit”文件。

5、弹出提示中点击Yes,添加“.bit”文件。

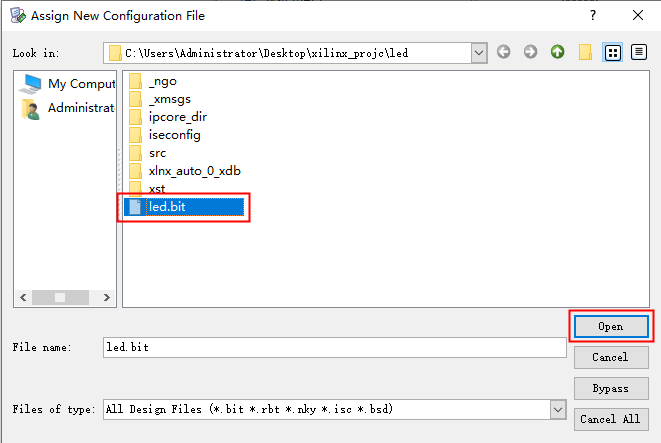

6、在弹出的文件路径窗口中,找到前面生成的“.bit”文件,选中后点击Open。

6、在弹出的文件路径窗口中,找到前面生成的“.bit”文件,选中后点击Open。

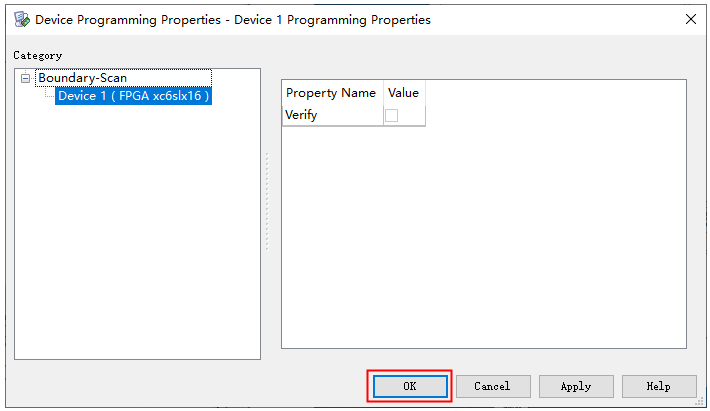

7、此窗口中点击OK。

7、此窗口中点击OK。

8、弹出的对话框中选择No。

8、弹出的对话框中选择No。

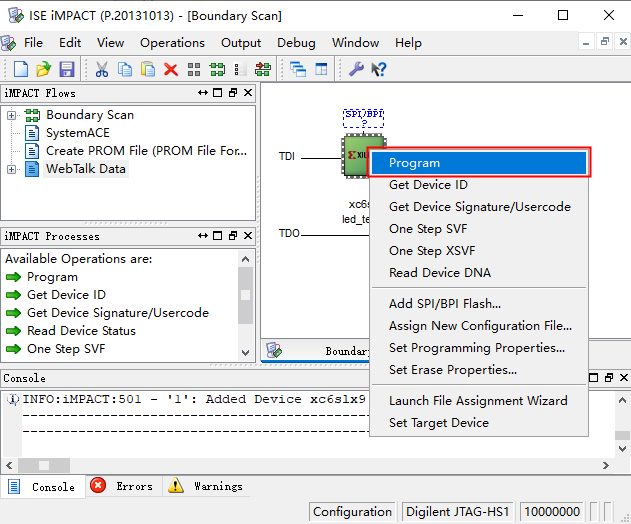

9、返回到ISE的iMPACT界面;选中芯片图标,单击右键选择Program;

9、返回到ISE的iMPACT界面;选中芯片图标,单击右键选择Program;

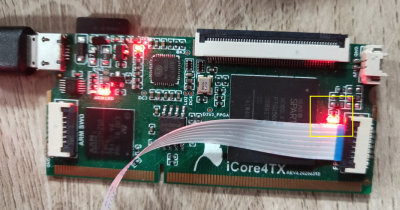

10、弹出的提示窗口中单击OK,如果一切正常下载成功,iMPACT界面会出现蓝色的Program Succeeded提示字样。表明程序已经下载至FPGA。此时可以观察到FPGA_LED闪烁。

10、弹出的提示窗口中单击OK,如果一切正常下载成功,iMPACT界面会出现蓝色的Program Succeeded提示字样。表明程序已经下载至FPGA。此时可以观察到FPGA_LED闪烁。

- 注意:

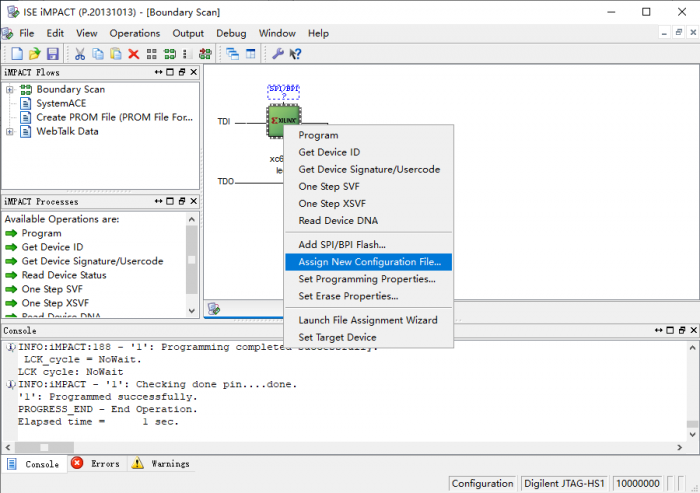

添加“.bit”文件时,还可以在iMPACT界面,点击芯片图标,右键选择Assign New Configuration File…。后面的操作步骤不变。

六、实验结果:

七、备注:闪退问题

如果遇到“open Project”闪退,或者编译时闪退,可网上搜索关键字“ISE 14.7 闪退”,解决办法基本一致。下面是解决步骤:

1、第一步

- 找到ISE安装目录下的文件夹:

- C:\Xilinx\14.7\ISE_DS\ISE\lib\nt64 (如果在其他盘安装,切换盘符,找到ISE的安装目录)

- 对文件夹下的两个文件作如下操作:

- 将libPortability.dll重名为libPortability.dll.orig

- 将 libPortabilityNOSH.dll 复制一份,然后将这个复制重命名为libPortability.dll

2、第二步

- 寻找安装Xilinx_ISE的安装目录下的文件夹:

- C:\Xilinx\14.7\ISE_DS\common\lib\nt64 (如果在其他盘安装,切换盘符,找到ISE的安装目录)

- 对文件夹下的两个文件作如下操作:

- 将libPortability.dll重名为libPortability.dll.orig

- 然后将已经复制好的libPortabilityNOSH.dll文件复制到该文件夹下,并重命名为libPortability.dll