这是本文档旧的修订版!

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 购买链接 | 点击购买 | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V0.1 | 20200103 | XiaomaGee | 初次建立 |

iCore3异构双核心板

0 基础资料下载

| 序 号 | 名 称 | 下载链接 |

| 1 | 原理图: | iCore3原理图.pdf |

| 2 | 扩展引脚分布: | iCore3扩展引脚分布v1.1.pdf |

| 3 | 机械尺寸: | iCore3机械尺寸图.pdf |

| 4 | 用户手册: | iCore3硬件手册v1.0.pdf |

| 5 | 出厂测试说明 | iCore3_demov1.0说明.pdf |

| 6 | 测试demo | iCore3_demo.zip |

| 7 | PCB库: | 购买后提供 |

| 8 | PCB图: | 购买后提供 |

| 9 | 原理图符号: | 购买后提供 |

| 10 | iCore3封装库及使用说明V1.0: | 购买后提供 |

| 11 | iCore3二次开发硬件手册: | 购买后提供 |

| 12 | iCore3_ADM资料包: | 购买后提供 |

| 13 | ARM实验例程: | 购买后提供 |

| 14 | FPGA实验例程: | 购买后提供 |

ARM实验例程预览(标准外设库)

ARM实验例程预览(基于HAL库)

MicroPython ARM 例程

| 例程一 | MicroPython 固件烧录 |

| 例程二 | MicorPython 驱动三色LED |

| 例程三 | MicorPython 读取按键状态 |

| 例程四 | MicorPython EXTI外部中断 |

| 例程五 | MicorPython UART串口通讯 |

| 例程六 | MicorPython 定时器实验 |

| 例程七 | MicorPython 看门狗实验 |

| 例程八 | MicorPython PWM呼吸灯 |

| 例程九 | MicorPython DAC实验 |

| 例程十 | MicorPython RTC实时时钟实验 |

| 例程十一 | MicorPython SDIO实验 |

| 例程十二 | MicorPython 文件操作实验 |

| 例程十三 | MicorPython 导入自写Python模块 |

| 例程十四 | MicorPython USB_VCP虚拟串口 |

| 例程十五 | MicorPython 多线程实验 |

| 例程十六 | MicorPython TF卡虚拟成U盘 |

| 例程十七 | MicorPython ADC实验 |

| 例程十八 | MicorPython TCP客户端实验 |

| 例程十九 | MicorPython TCP服务器实验 |

| 例程二十 | MicorPython UDP通信实验 |

| 例程二十一 | MicorPython RAM-FPGA SPI通信 |

| 例程二十二 | MicorPython RAM-FPGA I2C通信 |

| 例程二十三 | MicorPython 等待更新 |

| 例程二十四 | MicorPython 等待更新 |

| 例程二十五 | MicorPython 等待更新 |

FPGA实验例程预览

| 例程一 | 认识FPGA——环境搭建与调试下载 |

| 例程二 | GPIO输出实验——点亮三色LED |

| 例程三 | GPIO输入实验——识别按键输入 |

| 例程四 | Tcl脚本实验——配置引脚 |

| 例程五 | Signal Tapll实验——逻辑分析仪 |

| 例程六 | 计数器实验——计数器使用 |

| 例程七 | 基础逻辑门实验——逻辑门使用 |

| 例程八 | 触发器实验——触发器的使用 |

| 例程九 | 状态机实验——状态机使用 |

| 例程十 | 锁相环实验——锁相环使用 |

| 例程十一 | 乘法器实验——乘法器使用 |

| 例程十二 | Modelsim仿真实验 |

| 例程十三 | FSMC总线通信实验——复用地址模式 |

| 例程十四 | FSMC总线通信实验——独立地址模式 |

| 例程十五 | 基于USART的ARM与FPGA通信实验 |

| 例程十六 | 基于SPI总线的ARM与FPGA通信实验 |

| 例程十七 | 基于I2C总线的ARM与FPGA通信实验 |

| 例程十八 | 基于单口RAM的ARM+FPGA数据存取实验 |

| 例程十九 | 基于双口RAM的ARM+FPGA数据存取实验 |

| 例程二十 | 基于FIFO的ARM+FPGA数据存取实验 |

| 例程二十一 | Niosii——基于内部RAM建立第一个软核 |

| 例程二十二 | Niosii——固化程序到 EPCS 里 |

| 例程二十三 | 使用JTAG UART终端打印信息 |

| 例程二十四 | Niosii——SDRAM读写实验 |

| 例程二十五 | NIOS II之UART串口通信实验 |

| 例程二十六 | SDRAM读写测试实验 |

| 例程二十七 | 基于SDRAM的TFT驱动器的设计 |

| 例程二十八 | 基于SDRAM 的VGA 驱动器的设计 |

| 例程二十九 | VGA驱动器的设计 |

| 例程三十 | TFT_LCD彩条显示实验 |

| 例程三十一 | TFT_LCD触摸屏实验 |

| 例程三十二 | 千兆以太网实验 |

| 例程三十三 | 基于ARM+FPGA的高速AD采集传输实验(AD9226) |

1 介绍

- iCore3双核心工控板是银杏公司推出的第三代iCore系列双核心板;由于其独特的ARM+FPGA的“万金油”式双核心结构,使得其能用于诸多测试测量及控制领域。“ARM”核心采用Coretex-M4内核的STM32F407IGT6,负责功能实现、事件处理及接口等 功能。“FPGA”核心采用AlteraCyclone系列第四代产品EP4CE10F17C8N,作为“逻辑器件”角 色(亦可以说成“并行”执行角色),负责并行处理、实时性处理及逻辑管理等功能。两个核心数据交换的便利性及实时性,使得两个核心“拧成一股绳”,以应对越来越高的测试测量 及自动控制类产品功能、性能的需求。

2 资源特性

2.1 电源特性:

- 1、采用USB_OTG、USB_UART 和EXT_IN三种供电方式;

- 2、数字电源输出为3.3V,采用高效率的BUCK电路,为ARM/FPGA/SDRAM 等供电;

- 2、FPGA PLL内部含有大量模拟电路,为了保证PLL的性能,我们采用LDO为PLL提供模拟电源;

- 3、STM32F407IGT6提供独立的模拟电压基准,为片上ADC/DAC提供基准电压;

- 4、提供电源监控和基准;

2.2 ARM 特性:

- 1、采用主频168M的高性能STM32F407IG;

- 2、多达68个高性能I/O扩展;

- 3、与I/O复用,包括ARM内置的SPI/I2C/UART/TIMER/ADC/DAC等功能;

- 4、包括100M以太网、高速USB-OTG接口及用于调试的USB转UART功能;

- 5、包括TF卡接口,USB-OTG接口(可接U盘);

- 6、5P简化后的SWD调试接口,可以选配转接器以适应通用的20p接口;

- 7、采用16位并行总线通信;

2.3 FPGA 特性:

- 1、采用Altera公司第四代Cyclone系列FPGA EP4CE10F17C8N;

- 2、多达105个高性能I/O扩展;

- 3、FPGA外扩SDRAM,容量为8M字节;

- 4、配置模式:支持JTAG、AS、PS模式;

- 5、支持通过ARM配置加载FPGA;AS PS功能需通过跳线冒选择;

- 6、采用16位并行总线通信;

2.4 其他特性:

- 1、USB有三种工作模式:DEVICE模式、HOST模式和OTG模式;

- 2、以太网接口类型为100M全双工;

- 3、可跳线选择供电模式,USB接口直接供电,或通过排针供电(5V电源);

- 4、两个独立按键分别由ARM和FPGA控制;

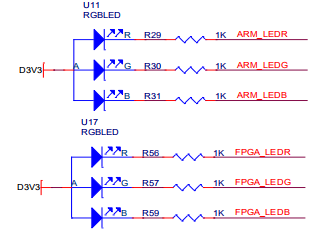

- 5、两颗三色LED用作指示;分别接于ARM和FPGA上;

- 6、含25M和24M两个独立的有源晶振时钟,和一个32.768K的无源晶振;

其他特性、资料待加入…

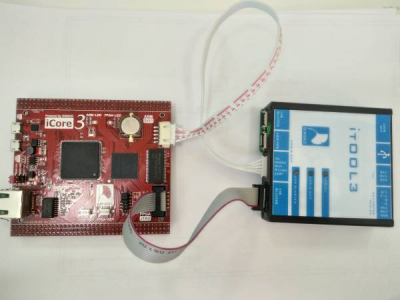

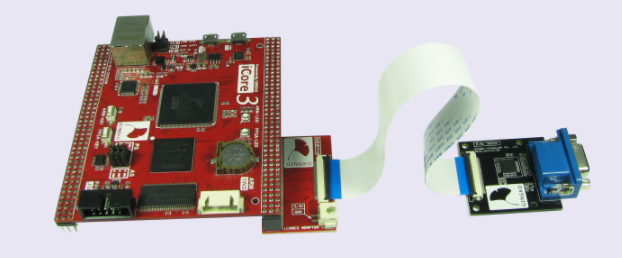

3 仿真器与开发板连接

1.选择iTool3下载器 第三代八合一调试工具箱 仿真器 支持iCore3开发板

2.准备好一根5p异面红白排线,一根10p的灰排线,iCore3开发板,和iTool3下载器

3.连接图如图所示

ARM程序下载口(ARM_SWD)与iTool3的ARM下载口用5p的异面红白排线相连

FPGA程序下载口(FPGA_JTAG)与iTool3的FPGA下载口用10p的灰白排线相连

如图,默认跳线帽选择中间,此时选择USB_UART端通过Microusb线与电脑端相连

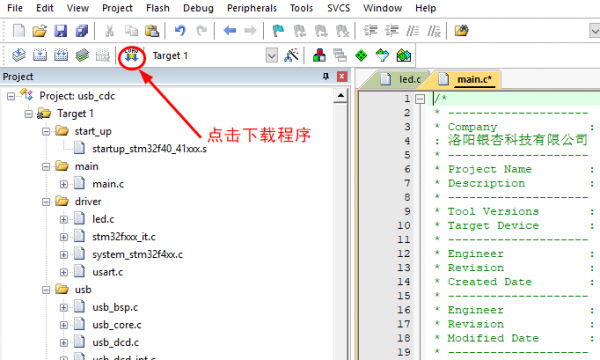

keil5中ARM程序下载如图

FPGA程序下载如图

4 出厂测试程序

4.1概要

本资料包包含5个文件夹:

- 1、“arm”里是 icore3上 arm的程序包,开发环境为 KEIL 5.17;

- 2、“fpga”里是 icore3 上 fpga的程序包,开发环境为 QuartusII 15.0(好像低版本的也可以打开);

- 3、“相关软件”里包含 putty 终端软件和 UDP 调试软件;

- 4、“屏幕截图”为工作时的截图;

- 5、“驱动”为板载 usb 转 uart的驱动程序,本实验之前需要安装到计算机。

4.2 准备工作

为了运行测试程序,需要做一些准备工作。

- 1、通过网线把iCore3与电脑连接,用于测试以太网功能;电脑ip设置为192.168.0.1网段;

- 2、把FPGA配置跳线置于PS模式;

- 3、电源供电跳线选择为USB UART模式;

- 4、通过micro usb转U盘线缆,连接一个U盘到icore3上,u盘必须为fat32文件系统;也可以把fpga工程下的sdram.rbf文件拷贝到u盘里,这样就可以通过u盘配置fpga了;

- 5、连接一个TF卡到iCore3卡座上,TF卡必须为fat32或者fat文件系统,也可以把fpga工程下的sdram.rbf文件拷贝到TF卡,这样就可以通过TF 配置fpga了;

- 6、通过micro usb线缆把USB UART端口与计算机USB接口相连,并安装好“驱动”目录里的驱动文件;使得板载的USB转UART可以正常工作。

4.3 测试过程

开始测试:

- 通过 micro usb线把iCore3的usb uart接口与计算机连接好后,计算机会识别到一个串口号。通过putty.exe 软件把此串口打开(端口号需要在“设备管理器”里查看),波特率配置为 115200,然后键入 test 并按回车进行测试。测试图片如图所示。

网络接口测试:

- 网络接口需要安装软件自带的UDP 测试工具,安装好后“新建连接”,选择UDP协议,并把目标IP 设置成 192.168.0.10, 目标端口设置成30000;即可通过此软件发送数据到iCore3,iCore3 接收到数据后会原封不动发向计算机。测试图片如图所示。

4.4测试内容解析

- 1、电源:紫色字体显示为[POWER ]为电源测试,可得到iCore3的5V供电、核心板电流、板载3.3V/1.2V/2.5V 的电压,测试成功后会显示[OK];

- 2、RTC实时时钟:会读出RTC时间和日期,若时间在走则说明功能正确,这里要注意的是时间还不准的(因为没有设定);

- 3、TF卡测试:此测试分为两部分,第一步首先探测TF卡信息并显示,第二步为读写实验,程序会在TF卡上建立一个10k大小的文件,写入并读取校验,测试结果也会显示出来;

- 4、U 盘测试:与TF卡测试类似,若U盘测试成功,则程序会在U盘上建立一个10k大小的文件,写入并读取校验,然后显示测试结果;

- 5、FPGA PS配置:程序会尝试通过TF卡或者U盘里读取sdram.rbf文件,并配置FPGA,若TF卡或者U盘里有此程序,则会配置成功;sdram.rbf 是通过quartusii软件转换过来的,此文件在fpga文件夹内;

- 6、总线读写测试:此功能通过stm32 fsmc读写fpga内ram数据,完成7个ram块的读写测试,每个ram块为512字节;

- 7、按键测试:在»提示符下,按下按键会显示按键按下信息;

- 8、LED测试:ARM和FPGA LED均会三色循环显示;

- 9、SDRAM读写测试:此测试由fpga程序完成,测试成功后fpga的LED会三色循环显示。测试失败后LED会显示“白色”;

4.5FPGA程序下载

4.5.1 JTAG模式

Core3工控板的JTAG接口与FPGA相连,即可用于芯片内部测试,还可对芯片进行在线编程。其电路连接图如图20所示,JTAG接口通过防静电芯片SRV05-4与FPGA相连,其中芯片SRV05-4是低电容、低漏电流的瞬态抑制二极管(TVS)阵列,SOT-26封装,5V的工作电压,可以保护JTAG接口与FPGA相连的四根高速数据线,这四根线分别为:

TCK——测试时钟输入;

TDI——测试数据输入,数据通过TDI输入JTAG口;

TDO——测试数据输出,数据通过TDO从JTAG口输出;

TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式;

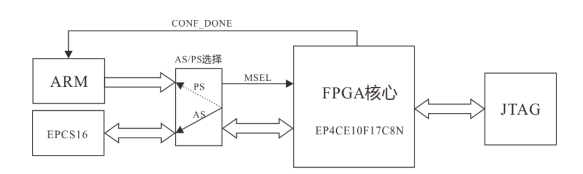

4.5.2 AS模式

iCore3异构双核心工控板上的FPGA有两种配置模式,分别为主动配置模式(AS)和被动配置 模式(PS)。所谓AS配置模式,即FPGA器件每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,从配置器件EPCS16主动发出读取数据信号,从而把EPCS16的数据读入FPGA中,实现对FPGA的编程。配置数据通过DATA0引脚送入FPGA,配置 数据被同步在DCLK输入上,1个时钟周期传送1位数据。

FPGA 配置模式示意图

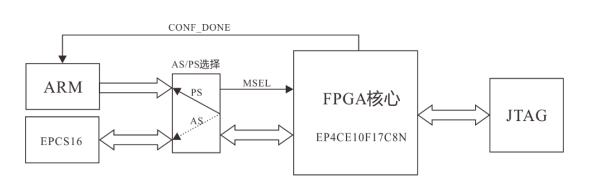

4.5.3 PS模式 (default)

所谓PS配置模式,则由ARM控制器控制配置过程。ARM作为控制器件,通过普通IO实现PS配置时序,实现对FPGA的编程。该模式可以实现对FPGA在线可编程,而且编程后FPGA立即工作,无需电源复位。

FPGA 配置模式示意图

5 接口电路

5.1 USB_OTG接口

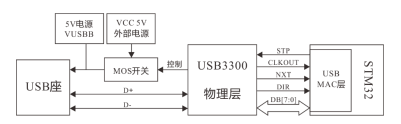

iCore3的USB有三种工作模式:DEVICE模式、HOST模式和OTG模式。当USB作为OTG 模式使用时其结构如图所示,USB3300为物理协议层,通过8个数据双向引脚,三个控制引脚STP、DIR和NXT,和一个时钟引脚CLKOUT,与STM32芯片中的USBMAC层相连,从而实现了STM32与USB座的连接。STM32的USB_OTG接口有两种工作模式:①当用作从机模式时,MOS关断;②当用作主机模式时(如U盘读取),MOS开关打开,通过USB座对外供电。

5.2 以太网接口

iCore3双核心工控板的网络模块采用W5500芯片作为以太网控制器,其通过SPI总线与STM32 的SPI口相连,STM32通过引脚LAN_CS对W5500进行片选,W5500则通过引脚LAN_INT进行 中断输出,另外通过信号收发线与隔离型网络接口连接,其连接示意图如图所示。为了减少系统能耗,W5500还提供了网络唤醒模式(WOL)及掉电模式供客户选择。

5.3 三色LED指示灯

iCore3异构双核心工控板的两个LED灯共有红、绿、蓝三种颜色,分别由ARM和FPGA控制。三色LED电路连接图如图所示。在编程调试过程中可用指示灯显示其状态,三色合一的设计,减少了LED灯占用空间,也使状态指示更加清晰明了。

5.4 独立按键

5.5 RTC实时时钟

iCore3异构双核心工控板采用32.768K无源晶体为系统提供RTC实时时钟,其电路连接图如图所示。32.768KHz外部无源晶体连接OSC32_IN和OSC32_OUT两引脚之间,为获得稳定的频率必须外加两个电容构成外部振荡电路。

5.6 SDRAM存储器

- iCore3异构双核心工控板载有一片SDRAM,其型号为HY57V641620HT,主要用作数据缓存,也可以用于内建NIOSII软核,将SDRAM作为它的主存储器。SDRAM与FPGA的连接示意图如图所示。

6 开发环境安装

- ARM和FPGA开发环境,推荐安装与例程版本相同的环境。否则会造成兼容性问题,导致例程无法正常使用。解压后FPGA 工程、ARM工程一定要保证没有中文路径。

7 外围模块

7.1 VGA显示模块

原理图: vga.pdf

外形结构(实物图):

连接方式:

特性:

- 1.此模块只支持与iCore3相连接;

- 2.提供分辨率800×600/1024×68两个分辨率的源码;

- 3.提供emwin5工程及实例支持;

- 4.模块使用iCore3提供电源,无需单独供电;

7.2 4.3寸液晶模块

原理图: i3_tft43.pdf

连接图

特性

- 1.此模块只支持与iCore3相连接;

- 2.480×272的分辨率,带电阻触摸,提供驱动源代码;

- 3.提供emwin5工程及实例支持;

- 4.模块使用iCore3提供电源,无需单独供电;

7.3 7.0寸液晶模块

原理图: i3_tft70.pdf

连接图:

特性:

- 1.此模块只支持和iCore3连接;

- 2.800×480的分辨率,带电阻触摸,提供驱动源代码;

- 3.提供emWin5工程及实例支持;

- 4.模块使用iCore3提供电源,无需单独供电;